## Ultra-low capacitance single line ESD protection

#### **Product status link**

ESDZX168B-1BF4

### **Features**

- Stand-off voltage : 16 V

- Ultra-low clamping voltage: 32 V at 16 A Ipp TLP

- Bidirectional protection

- Ultra-low capacitance: 0.12 pF

- Very high bandwidth: > 40 GHz

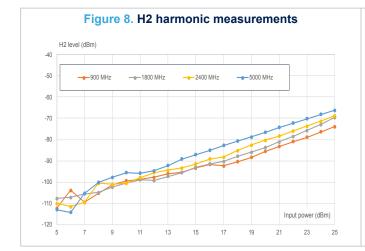

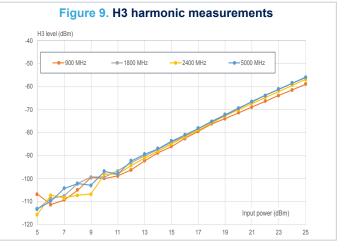

- Very low harmonic: H3 < -55 dBm at 25 dBm power

- Very low dynamic resistance :  $0.8 \Omega$

- 0201 package

- ECOPACK2 compliant component

- Exceeds IEC 61000-4-2 level 4 standard:

- ±12 kV (contact discharge)

- ±30 kV (air discharge)

### **Application**

Where transient over voltage protection in ESD sensitive equipment is required, such as:

- USB4, USB 3.1 Gen 1 and Gen 2

- HDMI 2.1

- Ethernet 1G, 10G

- DisplayPort

- LVDS

### **Description**

The ESDZX168B-1BF4 is a bidirectional single line TVS diode designed to protect the data lines or other I/O ports against ESD transients. Thanks to extra low capacitance, ESDZX168B-1BF4 can protect high-speed differential lines with no impact on signal integrity.

With an extremely low clamping voltage, ESDZX168B-1BF4 is able to protect the most sensitive, submicron technology circuits.

## 1 Characteristics

Table 1. Absolute maximum ratings (T<sub>amb</sub> = 25 °C)

| Symbol           |                                                                                  | Value | Unit        |    |

|------------------|----------------------------------------------------------------------------------|-------|-------------|----|

| V <sub>pp</sub>  | Peak pulse voltage  IEC 61000-4-2 contact discharge  IEC 61000-4-2 air discharge |       | ±12<br>±30  | kV |

| I <sub>pp</sub>  | Peak pulse current (8/20 µs)                                                     |       | 2.2         | Α  |

| T <sub>j</sub>   | Operating junction temperature range                                             |       | -55 to +150 |    |

| T <sub>stg</sub> | Storage junction temperature range                                               |       | -65 to +150 | °C |

| TL               | Maximum lead temperature for soldering during 10 s                               |       |             |    |

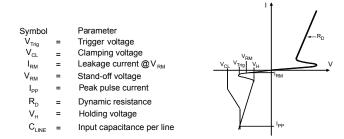

Figure 1. Electrical characteristics (definitions)

Table 2. Electrical characteristics (values) (T<sub>amb</sub> = 25° C)

| Symbol                           | Parameter Test condition                                                    |                                                            | Min. | Тур. | Max. | Unit  |  |

|----------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------|------|------|------|-------|--|

| V <sub>trig</sub>                | Trigger voltage                                                             |                                                            | 18   | 23   | 25   | V     |  |

| V <sub>H</sub>                   | Holding voltage                                                             |                                                            |      |      |      | V     |  |

| V <sub>RM</sub>                  | Reverse working voltage                                                     |                                                            |      |      | 16   | V     |  |

| I <sub>RM</sub>                  | Leakage current                                                             | V <sub>RM</sub> = 16 V                                     |      |      | 50   | nA    |  |

| I <sub>R</sub>                   | Leakage current                                                             | V <sub>R</sub> = 5 V                                       |      |      | 10   | nA    |  |

| V <sub>CL</sub> <sup>(1)</sup>   | Clamping voltage IEC 61000-4-2, 8 kV contact discharge measured after 30 ns |                                                            |      | 32   |      | V     |  |

| V <sub>CL</sub> <sup>(1)</sup>   | Clamping voltage 8/20 µs waveform, I <sub>PP</sub> = 2 A                    |                                                            |      |      | 24   | V     |  |

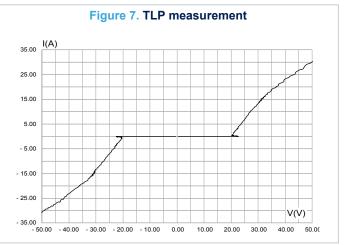

| ) (1)                            | TID magaziroment (pulse duration 100ps)                                     | I <sub>PP</sub> = 16 A                                     |      | 32   |      | V     |  |

| V <sub>CL</sub> <sup>(1)</sup>   | TLP measurement (pulse duration 100ns)                                      | I <sub>PP</sub> = 4 A                                      |      | 23   |      | \ \ \ |  |

| R <sub>D</sub> <sup>(1)</sup>    | Dynamic resistance                                                          | TLP - Pulse duration 100 ns - I <sub>PP</sub> [1 A – 16 A] |      | 0.8  |      | Ω     |  |

| C <sub>LINE</sub>                | Line capacitance                                                            | V <sub>LINE</sub> = 0 V, F = 1 MHz                         |      | 0.7  |      | pF    |  |

| C (1)                            | Line capacitance                                                            | V <sub>LINE</sub> = 0 V, F = 2.5 GHz                       |      | 0.11 | 0.17 |       |  |

| C <sub>LINE</sub> <sup>(1)</sup> | $V_{LINE} = 0 V, F = 5 GHz$                                                 |                                                            |      | 0.10 | 0.15 | pF    |  |

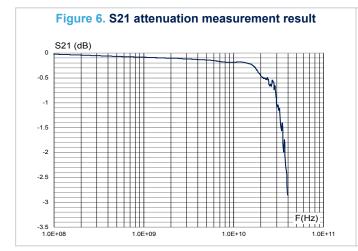

| F <sub>C</sub> <sup>(1)</sup>    | -3dB                                                                        |                                                            |      | > 40 |      | GHz   |  |

1. Evaluated by characterization – Not tested in production.

DS14431 - Rev 4 page 2/11

10

### 1.1 Characteristics (curves)

Figure 2. Leakage current versus junction temperature (typical values)

V<sub>RM</sub> = 5 V

T<sub>j</sub> (°C)

(typical values) C (pF) 0.9 0.8 0.7 0.5 0.4 0.3 0.2 0.1 f (Hz) 0 └── 1.0E+08 1.0E+09 1.0E+10 1.0E+11

Figure 3. Junction capacitance versus frequency

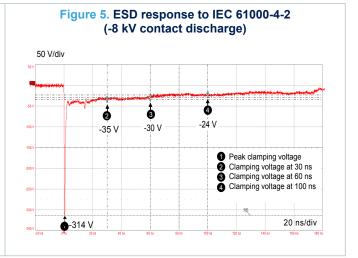

Figure 4. ESD response to IEC 61000-4-2 (+8 kV contact discharge)

50 V/div

Peak clamping voltage at 30 ns Quamping voltage at 60 ns Quamping voltage at 100 ns Quamping voltage at 10

DS14431 - Rev 4 page 3/11

DS14431 - Rev 4 page 4/11

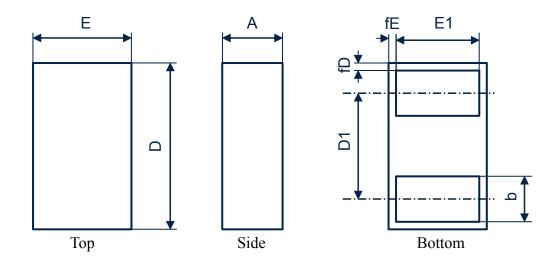

# 2 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at: www.st.com. ECOPACK is an ST trademark.

## 2.1 0201 package information

Figure 10. Package outline

Table 3. Package mechanical data

|      | Dimensions  |        |        |  |  |  |

|------|-------------|--------|--------|--|--|--|

| Ref. | Millimeters |        |        |  |  |  |

|      | Min.        | Тур.   | Max.   |  |  |  |

| А    | 0.180       | 0.200  | 0.220  |  |  |  |

| b    | 0.1475      | 0.1675 | 0.1875 |  |  |  |

| D    | 0.560       | 0.580  | 0.600  |  |  |  |

| D1   |             | 0.3375 |        |  |  |  |

| E    | 0.260       | 0.280  | 0.300  |  |  |  |

| E1   | 0.185       | 0.205  | 0.225  |  |  |  |

| fD   |             | 0.0375 |        |  |  |  |

| fE   |             | 0.0375 |        |  |  |  |

DS14431 - Rev 4 page 5/11

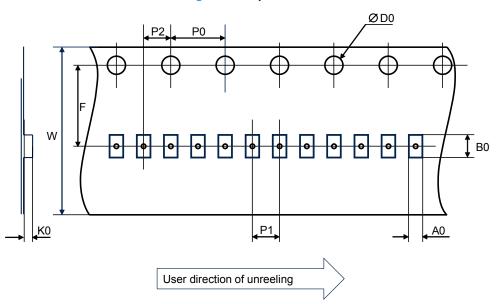

## 2.2 Packing and marking information

Figure 13. Tape outline

Table 4. Tape and reel mechanical data

|      | Dimensions  Millimeters |      |      |  |  |

|------|-------------------------|------|------|--|--|

| Ref. |                         |      |      |  |  |

|      | Min.                    | Тур. | Max. |  |  |

| A0   | 0.31                    | 0.34 | 0.37 |  |  |

| ВО   | 0.61                    | 0.64 | 0.67 |  |  |

| D0   | 1.40                    | 1.50 | 1.60 |  |  |

| F    | 3.45                    | 3.50 | 3.55 |  |  |

| K0   | 0.21                    | 0.24 | 0.27 |  |  |

| P0   | 3.90                    | 4.00 | 4.10 |  |  |

| P1   | 1.95                    | 2.00 | 2.05 |  |  |

| P2   | 1.95                    | 2.00 | 2.05 |  |  |

| W    | 7.90                    | 8.00 | 8.30 |  |  |

DS14431 - Rev 4 page 6/11

# 3 Recommendation on PCB assembly

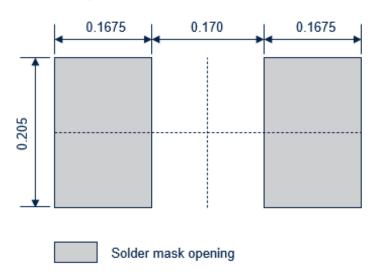

## 3.1 Footprint

Figure 14. Recommended footprint in mm

Note: Solder mask defined (SMD) recommended.

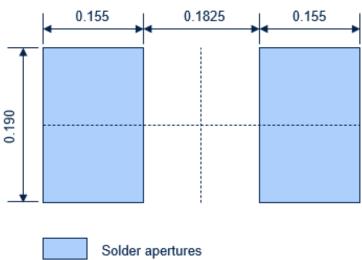

## 3.2 Stencil opening design

Stencil opening thickness: 75 µm / 3 mils

Figure 15. Stencil opening recommendations

DS14431 - Rev 4 page 7/11

### 3.3 Solder paste

- 1. Halide-free flux qualification ROL0 according to ANSI/J-STD-004.

- 2. "No clean" solder paste is recommended.

- 3. Offers a high tack force to resist component movement during high speed.

- 4. Use solder paste with fine particles: powder particle size 20-38 μm.

#### 3.4 Placement

- 1. Manual positioning is not recommended.

- 2. It is recommended to use the lead recognition capabilities of the placement system, not the outline centering

- 3. Standard tolerance of ±0.05 mm is recommended.

- 4. 1.0 N placement force is recommended. Too much placement force can lead to squeezed out solder paste and cause solder joints to short. Too low placement force can lead to insufficient contact between package and solder paste that could cause open solder joints or badly centered packages.

- 5. To improve the package placement accuracy, a bottom side optical control should be performed with a high resolution tool.

- 6. For assembly, a perfect supporting of the PCB (all the more on flexible PCB) is recommended during solder paste printing, pick and place and reflow soldering by using optimized tools.

### 3.5 PCB design preference

- 1. To control the solder paste amount, the closed via is recommended instead of open vias.

- 2. The position of tracks and open vias in the solder area should be well balanced. A symmetrical layout is recommended, to avoid any tilt phenomena caused by asymmetrical solder paste due to solder flow away.

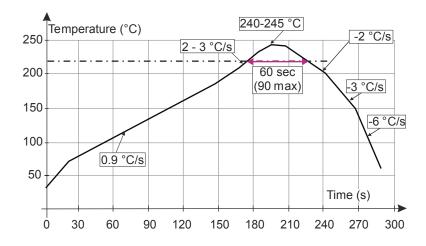

### 3.6 Reflow profile

Figure 16. ST ECOPACK recommended soldering reflow profile for PCB mounting

Note: Minimize air convection currents in the reflow oven to avoid component movement. Maximum soldering profile corresponds to the latest IPC/JEDEC J-STD-020.

DS14431 - Rev 4 page 8/11

# 4 Ordering information

Table 5. Ordering information

| Order code     | Marking          | Package | Weight   | Base qty. | Delivery mode |

|----------------|------------------|---------|----------|-----------|---------------|

| ESDZX168B-1BF4 | U <sup>(1)</sup> | ST0201  | 0.100 mg | 17000     | Tape and reel |

<sup>1.</sup> The marking can be rotated by multiples of 90° to differentiate assembly location

DS14431 - Rev 4 page 9/11

## **Revision history**

Table 6. Document revision history

| Date        | Revision | Changes                                                      |  |

|-------------|----------|--------------------------------------------------------------|--|

| 21-Sep-2023 | 1        | Initial release.                                             |  |

| 10-Jul-2024 | 2        | Updated Table 2, Figure 3, Figure 4, Figure 5, and Figure 6. |  |

| 16-Sep-2024 | 3        | Updated Product status link on cover page.                   |  |

| 26-Jun-2025 | 4        | Updated Section Features.  Added Figure 8, and Figure 9.     |  |

DS14431 - Rev 4 page 10/11

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

DS14431 - Rev 4 page 11/11