#### 50 A 800 V SCR in TOP3 insulated

**TOP3** Isolated

#### **Features**

- Max. repetitive blocking voltage = V<sub>DRM</sub>, V<sub>RRM</sub> = 800 V

- I<sub>GT</sub> maximum = 80 mA

- ECOPACK®2 component (RoHS and HF compliance)

- Complies with UL 1557 standard (File ref : E81734)

#### **Application**

- Solid state relays

- · Welding equipment

- High power motor control

- Heating systems

- Controlled AC/DC bridge

#### **Description**

Available in a high power package TOP3-I, the BTW69-800 is suitable in applications where power handling and power dissipation are critical, such as solid state relays, welding equipment, high power motor control and power converters.

This device offers a superior performance in surge current handling capabilities, allowing usage in industrial environment.

Thanks to its internal ceramic pad, it provide high voltage insulation (2500 $V_{RMS}$ ), complying with UL standards (file ref: E81734).

# Product status link BTW69-800

| Product summary     |       |  |

|---------------------|-------|--|

| I <sub>T(RMS)</sub> | 50 A  |  |

| $V_{DRM}/V_{RRM}$   | 800 V |  |

| I <sub>GT</sub>     | 80 mA |  |

### 1 Characteristics

Table 1. Absolute maximum ratings

| Symbol              | Parameters                                                                                                       | Value                                                                       | Unit                    |     |                  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------|-----|------------------|--|

| I <sub>T(RMS)</sub> | RMS on-state current (180° conduction angle)                                                                     | RMS on-state current (180 $^{\circ}$ conduction angle) $T_c = 75 ^{\circ}C$ |                         |     |                  |  |

| IT <sub>(AV)</sub>  | Average on-state current $T_c = 75  ^{\circ}\text{C}$ (180° conduction angle)                                    |                                                                             |                         |     | Α                |  |

| l                   | $t_{\rm p} = 8.3~{\rm ms}$                                                                                       |                                                                             |                         |     |                  |  |

| ITSM                | $I_{TSM}$ Non repetitive surge peak on-state current (full cycle, $T_j$ initial = 25 °C, $V_R$ = 0 V)            |                                                                             | t <sub>p</sub> = 10 ms  | 580 | A                |  |

| I <sup>2</sup> t    | $t_p = 10 \text{ ms}, T_j = 25^{\circ}\text{C}$                                                                  |                                                                             |                         |     | A <sup>2</sup> s |  |

| dl/dt               | Critical rate of rise of on-state current $I_G = 2 \times I_{GT}$ , $t_r \le 100 \text{ ns}$ $F = 60 \text{ Hz}$ |                                                                             | T <sub>j</sub> = 125 °C | 50  | A/µs             |  |

| I <sub>GM</sub>     | Peak gate current $t_p = 20 \mu s$                                                                               |                                                                             | T <sub>j</sub> = 125 °C | 8   | Α                |  |

| P <sub>G(AV)</sub>  | Average gate power dissipation                                                                                   | 1                                                                           | W                       |     |                  |  |

| T <sub>stg</sub>    | Storage junction temperature range                                                                               | -40 to +150                                                                 | °C                      |     |                  |  |

| Tj                  | Operating junction temperature range                                                                             | -40 to +125                                                                 | °C                      |     |                  |  |

| $V_{GRM}$           | Maximum peak reverse gate voltage                                                                                | 5                                                                           | V                       |     |                  |  |

| V <sub>ins</sub>    | Insulation RMS voltage, 1 minute                                                                                 | 2500                                                                        | V                       |     |                  |  |

Table 2. Electrical characteristics ( $T_j = 25^{\circ}C$ , unless otherwise specified)

| Symbol                             | Test conditions                                   |          | Value  | Unit |        |

|------------------------------------|---------------------------------------------------|----------|--------|------|--------|

| la-                                |                                                   |          | Min.   | 8    | mA     |

| I <sub>GT</sub>                    | $V_D = 12 \text{ V}, R_L = 33 \Omega$             |          | Max    | 80   | - IIIA |

| V <sub>GT</sub>                    |                                                   |          | Max    | 1.3  | V      |

| V <sub>GD</sub>                    | $V_D = V_{DRM}$ , $R_L = 3.3 \text{ k}\Omega$     | 125 °C   | Min.   | 0.2  | V      |

| I <sub>H</sub>                     | I <sub>T</sub> = 500 mA, gate open                | <u>'</u> | Max.   | 150  | mA     |

| IL                                 | I <sub>G</sub> = 1.2 x I <sub>GT</sub>            |          | Max.   | 200  | mA     |

| dV/dt                              | V <sub>D</sub> = 67 %, V <sub>DRM</sub> gate open | 125 °C   | Min.   | 1000 | V/µs   |

| V <sub>TM</sub>                    | I <sub>TM</sub> = 100 A, t <sub>p</sub> = 380 μs  |          | Max.   | 1.9  | V      |

| V <sub>TO</sub>                    | Threshold on-state voltage                        | 125 °C   | Max.   | 1.0  | V      |

| R <sub>D</sub>                     | On-state dynamic resistance                       | 125 °C   | Max.   | 8.5  | mΩ     |

| I <sub>DRM</sub> /I <sub>RRM</sub> | $V_D = V_{DRM}$ , $V_R = V_{RRM}$                 | 25 °C    | Max.   | 10   | μA     |

| ייאאטייRRM אויאמיי                 | AD - ADKW' AK - AKKW                              | 125 °C   | ividX. | 5    | mA     |

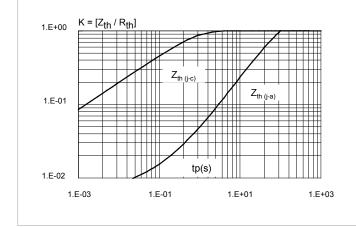

**Table 3. Thermal resistance**

| Symbol               | Parameters                | Value | Unit  |  |  |

|----------------------|---------------------------|-------|-------|--|--|

| R <sub>th(j-c)</sub> | Junction to case (D.C)    | 0.9   | °C/\/ |  |  |

| R <sub>th(j-a)</sub> | Junction to ambiant (D.C) | 50    | °C/W  |  |  |

DS13093 - Rev 2 page 2/9

#### 1.1 Characteristics (curves)

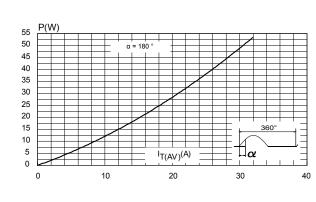

Figure 1. Maximum average power dissipation versus average on-state current

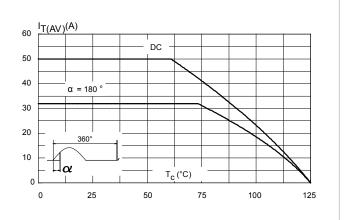

Figure 2. Average on-state current versus case temperature

Figure 3. Relative variation of thermal impedance versus pulse duration

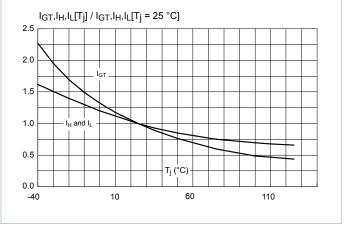

Figure 4. Relative variation of gate trigger current, holding current and latching current versus junction temperature

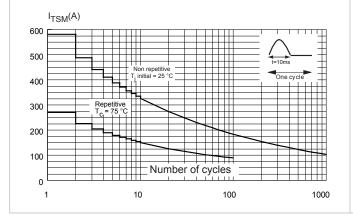

Figure 5. Surge peak on-state current versus number of cycles (V<sub>R</sub> = 0 V)

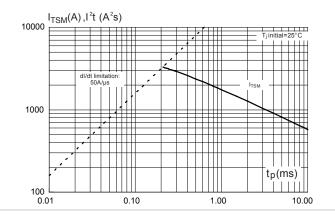

Figure 6. Non repetitive surge peak on-state current for a sinusoidal pulse with width  $t_p$ < 10 ms, and corresponding value of  $I^2t$  ( $V_R = 0$  V)

DS13093 - Rev 2 page 3/9

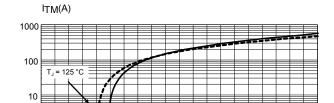

Figure 7. On-state characteristics (maximum values)

DS13093 - Rev 2 page 4/9

# Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

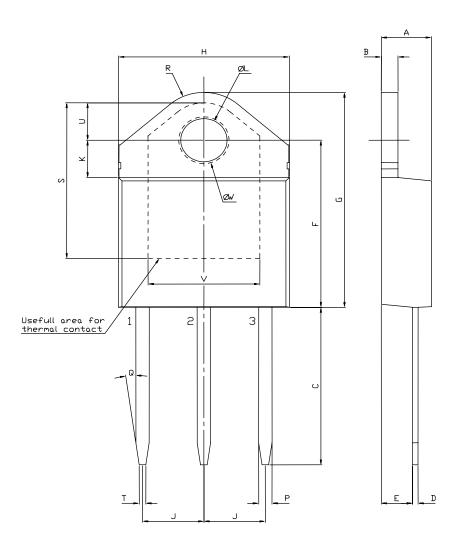

#### 2.1 TOP3 Ins. package information

- ECOPACK (lead-free plating and halogen free package compliance)

- Lead-free package leads finishing

- Halogen-free molding compound resin meets UL94 standard level V0

- Recommended torque: 1.05 N·m (max. torque: 1.2 N·m)

Figure 8. Package outline

DS13093 - Rev 2 page 5/9

Table 4. Mechanical data

|      | Dimensions |      |       |                       |        |        |

|------|------------|------|-------|-----------------------|--------|--------|

| Ref. | mm         |      |       | Inches <sup>(1)</sup> |        |        |

|      | Min.       | Тур. | Max.  | Min.                  | Тур.   | Max.   |

| Α    | 4.40       |      | 4.60  | 0.1732                |        | 0.1811 |

| В    | 1.45       |      | 1.55  | 0.0571                |        | 0.0610 |

| С    | 14.35      |      | 15.60 | 0.5650                |        | 0.6142 |

| D    | 0.50       |      | 0.70  | 0.0197                |        | 0.0276 |

| Е    | 2.70       |      | 2.90  | 0.1063                |        | 0.1142 |

| F    | 15.80      |      | 16.50 | 0.6220                |        | 0.6496 |

| G    | 20.40      |      | 21.10 | 0.8031                |        | 0.8307 |

| Н    | 15.10      |      | 15.50 | 0.5945                |        | 0.6102 |

| J    | 5.40       |      | 5.65  | 0.2126                |        | 0.2224 |

| K    | 3.40       |      | 3.65  | 0.1339                |        | 0.1437 |

| L    | 4.08       |      | 4.17  | 0.1606                |        | 0.1642 |

| Р    | 1.10       |      | 1.30  | 0.0430                |        | 0.0510 |

| R    |            | 4.60 |       |                       | 0.1811 |        |

<sup>1.</sup> Inches given for reference only

DS13093 - Rev 2 page 6/9

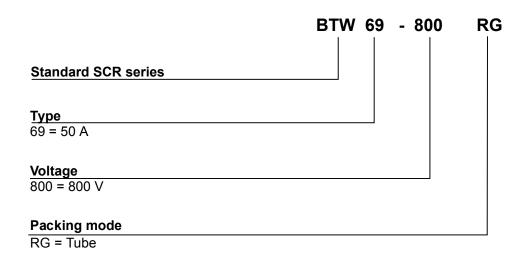

# 3 Ordering information

Figure 9. Ordering information scheme

**Table 5. Ordering information**

| Order code  | Marking  | Package   | Weight | Base qty. | Delivery mode |

|-------------|----------|-----------|--------|-----------|---------------|

| BTW69-800RG | BTW69800 | TOP3 Ins. | 4.5 g  | 30        | Tube          |

DS13093 - Rev 2 page 7/9

# **Revision history**

Table 6. Document revision history

| Date        | Revision | Changes                           |

|-------------|----------|-----------------------------------|

| 09-Sep-2019 | 1        | Initial release.                  |

| 27-Jul-2023 | 2        | Updated Table 4. Mechanical data. |

DS13093 - Rev 2 page 8/9

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

DS13093 - Rev 2 page 9/9