### Automotive synchronous Buck-Boost controller

VFQFN 32+4L (5x5x0.9 mm)

# Product status link STPM802A

| Product summary |            |          |  |  |

|-----------------|------------|----------|--|--|

| Order code      | Package    | Packing  |  |  |

| STPM802A-TR     | VFQPN32+4L | Tape     |  |  |

| STPW002A-TR     |            | and reel |  |  |

#### **Features**

Synchronous switching

Input voltage range: 4.2 V to 60 V

Output voltage range: 3.3 V to 14 V

Spread-spectrum frequency modulation

Integrated bootstrap diodes

Adjustable switching frequency: 177 kHz to 500 kHz

Peak drive current > 2.8 A

Standby mode

Developed according to ISO26262 for use in ASIL–D systems

#### **Description**

The STPM802A is a synchronous 4-switch single-phase non-inverting buck-boost DC/DC controller that regulates the output voltage, from an input voltage above, below, or equal to the output voltage. It offers an adjustable fixed-frequency operation and spread-spectrum capability to reduce EMI emissions.

The IC provides an inductor and output current monitor, OV/UV protections and a power-good flag. Fault protection is also provided to detect output short-circuit conditions, during which the IC retries, latches off, or keeps running.

The IC implements a low-power mode function, in which control loop management is adjusted in order to reduce power dissipation.

STPM802A offers a set of features to support applications that must meet functional safety requirements as defined by the Automotive Safety Integrity Level (ASIL) A-B-C-D depending on the application TSR.

#### 1 Overview

- The IC is a current mode DC/DC controller that can regulate output voltage and output current from an input voltage above, below or equal to the output voltage.

- A key pin (WAKE) is present.

- An internal comparator senses the VIN–ISN voltage drop, thus defining the regulation strategy for the control loop (buck mode, boost mode and transition mode).

- The device works regulating 1.2 V (internal reference voltage) at the FB pin. The regulated voltage is defined by means of an external voltage divider network.

- Shunt resistances (1 m $\Omega$  minimum) must be used both on the output high-side load current path (ISN/ISP) and on the low-side buck/boost current path (LSN/LSP). OVC\_LS and OVC\_HS thresholds can be selected from six different combinations by changing the external resistance on the OVC\_BUCK\_SEL and OVC\_BOOST\_SEL pins. The target inductor value with a 1 m $\Omega$  LSP/LSN shunt resistor is 3.3  $\mu$ H.

- Using external resistors of different values at the FS\_SEL pin is also used to configure the buck-boost switching frequency. The response in case of an undervoltage event on the VOUT pin (keep running, auto retry function, or turn-off) can be configured via the UV\_SS\_MODE pin, where spread spectrum can also be enabled.

- The device is equipped with a VOUT Undervoltage/Overvoltage detection, open drain fault pins (two for safety redundancy) and PGOOD diagnosis (output voltage within expected range).

- An internal low drop-out linear regulator (INTVCC) is present in order to drive low-side external MOSFETs, and to recharge the bootstrap capacitors.

- The bootstrap structure is used to drive high-side external MOSFETs.

- The device implements a standby function (using the STBY pin), in which some functions are turned off and the control loop is adjusted to ensure a reduction in power consumption.

DB5586 - Rev 1 page 2/10

# Block diagram and pin description

### 2.1 Block diagram

Figure 1. Block diagram INTVCC i\_dcm\_comp Charge Pump VINC Internal Supply Bandgap Generator **Ģ**GLS1 WAKE **Ģ**GLS2 Oscillators FAULT1 ₽LSS Control FAULT2 фгв\_мол logic **PGOOD** STBY\_ECHO STBY\_IN ↓ ↓ ↓ ↓ ↓ LSN OVCRED\_TSS OVC\_BUCK\_SELO SOFT\_START **ADC** UV\_SS\_MODE фсомр

DB5586 - Rev 1 page 3/10

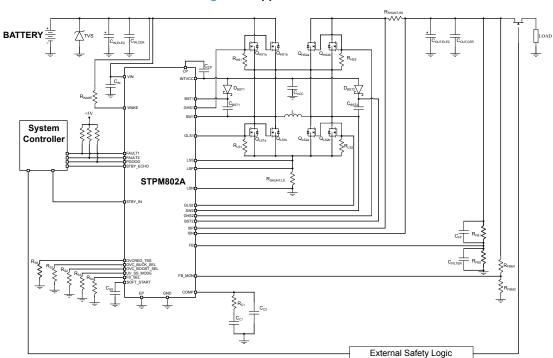

## 2.2 Applicative circuit

Figure 2. Applicative circuit

DB5586 - Rev 1 page 4/10

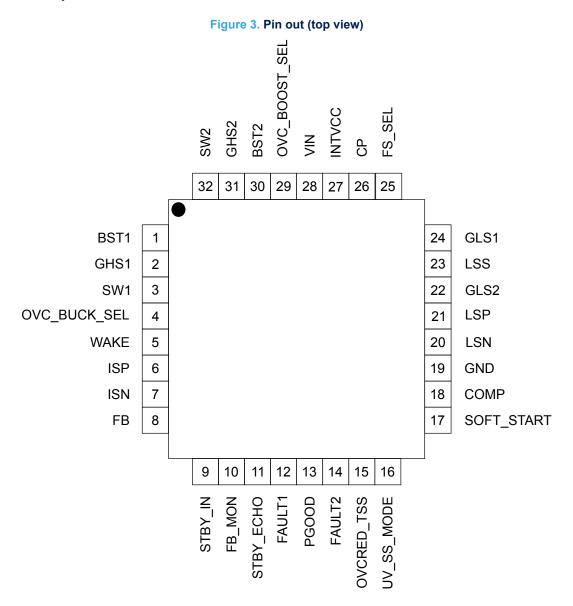

### 2.3 Pin description

The exposed pad is not electrically connected to the internal substrate. Connecting the exposed pad to the PCB ground plane through thermal vias improves thermal dissipation.

DB5586 - Rev 1 page 5/10

Table 1. Pin functions and description

| No. | Name          | Туре  | Description                                                                                                                                                                           |  |

|-----|---------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | BST1          | Local | Bootstrap capacitor/ bootstrap diode 1                                                                                                                                                |  |

| 2   | GHS1          | Local | High-side gate 1                                                                                                                                                                      |  |

| 3   | SW1           | Local | Switching node 1                                                                                                                                                                      |  |

| 4   | OVC_BUCK_SEL  | Local | Overcurrent value selection for buck operation and overload detection                                                                                                                 |  |

| 5   | WAKE          | Local | Device wake-up pin                                                                                                                                                                    |  |

| 6   | ISP           | Local | Load peak current detection shunt resistance – upper side                                                                                                                             |  |

| 7   | ISN           | Local | Load peak current detection shunt resistance – lower side                                                                                                                             |  |

| 8   | FB            | Local | Regulation feedback (external voltage divider)                                                                                                                                        |  |

| 9   | STBY_IN       | Local | If the defined pattern is applied to this pin, the device enters standby mode. An internal 30 $\mu$ A pull-up guarantees operation in normal mode if the pin is not driven externally |  |

| 10  | FB_MON        | Local | Safety redundancy pin for UV/OV diagnosis. The voltage divider is a copy of the one connected between the VOUT and FB pins. This pin is only a monitor, not used by the control loop  |  |

| 11  | STBY_ECHO     | Local | Open Drain with internal pull-up, IC provides an indication to the microcontroller whether the device is in normal or standby mode                                                    |  |

| 12  | FAULT1        | Local | Fault open drain                                                                                                                                                                      |  |

| 13  | PGOOD         | Local | Power-good open drain                                                                                                                                                                 |  |

| 14  | FAULT2        | Local | Fault open drain (safety redundancy)                                                                                                                                                  |  |

| 15  | OVCRED_TSS    | Local | Selection of reduced overcurrent threshold and of soft short diagnosis filter time                                                                                                    |  |

| 16  | UV_SS_MODE    | Local | Behavior in case of VOUT undervoltage and selection of spread spectrum function enable                                                                                                |  |

| 17  | SOFT_START    | Local | Soft start selection (external capacitor)                                                                                                                                             |  |

| 18  | COMP          | Local | Pin for external compensation network                                                                                                                                                 |  |

| 19  | GND           | Local | Signal ground                                                                                                                                                                         |  |

| 20  | LSN           | Local | Low-side current limitation shunt resistance – lower side                                                                                                                             |  |

| 21  | LSP           | Local | Low-side current limitation shunt resistance – upper side                                                                                                                             |  |

| 22  | GLS2          | Local | Low-side gate 2                                                                                                                                                                       |  |

| 23  | LSS           | Local | Low-side source common point                                                                                                                                                          |  |

| 24  | GLS1          | Local | Low-side gate 1                                                                                                                                                                       |  |

| 25  | FS_SEL        | Local | Switching frequency selection                                                                                                                                                         |  |

| 26  | СР            | Local | External capacitor, charge pump tank                                                                                                                                                  |  |

| 27  | INTVCC        | Local | Pin for LDO external bypass capacitor, bootstrap and low-side drivers supply                                                                                                          |  |

| 28  | VIN           | Local | Battery voltage                                                                                                                                                                       |  |

| 29  | OVC_BOOST_SEL | Local | Overcurrent value selection for boost operation                                                                                                                                       |  |

| 30  | BST2          | Local | Bootstrap capacitor / bootstrap diode 2                                                                                                                                               |  |

| 31  | GHS2          | Local | High-side gate 2                                                                                                                                                                      |  |

| 32  | SW2           | Local | Switching node 2                                                                                                                                                                      |  |

DB5586 - Rev 1 page 6/10

## 3 Package information

To meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions, and product status are available at: www.st.com. ECOPACK is an ST trademark.

#### 3.1 VFQFN (5x5x0.9, 32+4L) package information

BOTTOM VIEW D2  $\oplus$ В Д  $_{\Omega}$ ⋖ ppp ppp Z SECT Z-Z 7 L1 0.05 ref. PIN1 ID PLATED AREA eee CCCSIDE VIEW SEATING PLANE A2 (TOP VIEW  $\square$ Α В INDEX AREA  $(D/2 \times E/2)$ ш PPP ∆|aaa|C

Figure 4. VFQFN (5x5x0.9, 32+4L) package outline

DB5586 - Rev 1 page 7/10

Table 2. VFQFN (5x5x0.9, 32+4L) package mechanical data

| Symbol | Dimension in mm |                 |      |  |

|--------|-----------------|-----------------|------|--|

|        | Min.            | Тур.            | Max. |  |

| A      | A 0.80          |                 | 1.00 |  |

| A1     | 0.00            | 0.02            | 0.05 |  |

| A2     |                 | 0.2 REF         |      |  |

| A3     | 0.10            | -               | -    |  |

| b      | 0.20            | 0.25            | 0.30 |  |

| D      | -               | 5.00            | -    |  |

| е      | -               | 0.5             | -    |  |

| E      | -               | 5.00            | -    |  |

| L      | 0.35            | 0.45            | 0.55 |  |

| L1     | -               | 0.35            | -    |  |

| L2     | -               | 0.075           | -    |  |

| L3     | -               | 0.42            | -    |  |

| k      | 0.20            | -               | -    |  |

| N      |                 | 32+4            |      |  |

|        | Tolerance of fo | rm and position |      |  |

| aaa    | aaa 0.15        |                 |      |  |

| bbb    | 0.10            |                 |      |  |

| ccc    | 0.10            |                 |      |  |

| ddd    | 0.05            |                 |      |  |

| eee    |                 | 80.0            |      |  |

| fff    | 0.10            |                 |      |  |

|        | Expose PA       | D variation     |      |  |

| D2     | 3.55            | 3.60            | 3.65 |  |

| E2     | 3.55            | 3.60            | 3.65 |  |

Note:

4L additional corner pins are electrically floating, but it is recommended to solder them to GND in order to ensure the mechanical integrity of the package.

DB5586 - Rev 1 page 8/10

## **Revision history**

Table 3. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 07-Jul-2025 | 1       | Initial release. |

DB5586 - Rev 1 page 9/10

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

DB5586 - Rev 1 page 10/10