## FET driver for 3 phase BLDC motor

Data brief

### **Features**

- Supply voltage from 6 V to 36 V for working in 12 V and 24 V systems

- The device can withstand -7 V to 75 V at the FET high-side Driver pins

- Low standby current consumption

- 3.3 V internal regulator supplied by Vcc pin

- Boost regulator for full Rdson down to 6 V and over voltage protection

- 3 low-side + 3 high-side drivers:

- PWM operation up to 20 kHz

- Gate driver current adjustable via SPI in 4 steps. Range set via external resistor. Maximum gate controlled current 600 mA

- Source connection to each MOSFET

- Input pin for each gate driver

- 2-differential current sense amplifiers:

- Output offset selectable via SPI (0.2\*V<sub>CC</sub> offset for ground shunt resistors connection, 0.5\*V<sub>CC</sub> offset for phase shunt resistors connection)

- All the amplifier gain factors are programmable (10, 30, 50, 100)

### 8 MHz, 16-bit SPI:

Full diagnostic

- Programmable parameters:

- Cross conduction dead time with a fixed minimum value:

- 4 current steps driving the PowerMOS gates (25%, 50%, 75%, 100%);

- Phase or ground selection of current sense amplifier;

- Gain values for the current sense amplifiers;

- Zero current output voltage (offset) for the current sense amplifiers;

- Over voltage threshold selection for single or double battery operation;

- Short circuit detection thresholds for the low-side and the high-side MOSFETs (drain to source voltage monitor).

### Protection and diagnostic:

- FET driver:

- FET driver supply Undervoltage (UV) diagnostic;

- Gate to source output voltage limit;

- Gate to source passive switch off.

- Power supply pins V<sub>B</sub> and V<sub>CC</sub>

- Overvoltage (OV), Undervoltage (UV) diagnostic and protection

- All logic pins withstand 35 V

- Power MOSFET drain to source voltage drop measurement for overcurrent protection

- Over-temperature diagnostic and shutdown

- Fault status flag output

**Table 1: Device summary**

| Order code | Package                   | Packing     |

|------------|---------------------------|-------------|

| L9907A     | TQFP64 (10x10x1.0 mm)     | Tray        |

| L9907ATR   | TQFF04 (TUXTUXT.U IIIIII) | Tape & reel |

**Contents** L9907A

| CO | ntents   |                             |   |

|----|----------|-----------------------------|---|

| 1  | Descrip  | otion                       | 3 |

| 2  | Block d  | liagram and pin description | 4 |

|    | 2.1      | Block diagram               | 4 |

|    | 2.2      | Pin description             | 5 |

| 3  | Electric | al specifications           | 8 |

Absolute maximum ratings ...... 8

ESD protection ......9 Temperature ranges and thermal data ......9

TQFP64 (10x10x1 mm exp. pad down) package information....... 10

Package information......10

Cantanta

3.1

3.2

3.3

4.1

obsolete Product(s). Obsolete Obsolete

4

L9907A Description

### 1 Description

L9907A is a smart power device realized in STMicroelectronics advanced BCD-6s technology. It is able to drive all PowerMOS transistors for 3-phase BLDC motor applications. The circuit is suitable to operate in environments with high supply voltage such as double battery. Supply related pins are capable of withstanding up to 75 V. Moreover, the device is able to control the six pre-driver channels independently. In this way it is possible to implement all kind of electric motor control strategies. The integrated boost regulator provides sufficient gate charge for all PowerMOS down to a battery voltage of 6 V. All pre-drivers have dedicated connections with the MOSFET sources. The device offers programmability for a base gate output current via an external resistor. Moreover, via SPI, it is possible to select among 4 gate output current levels even while the application is running. All channels are protected against short circuit and the device is protected against overtemperature condition. Moreover, the boost converter implements an over voltage protection to allow safe functionality of pre-drivers in all battery voltage condition. During over voltage condition, BST\_C voltage is limited by temporarily switching off the boost regulator and pre-drivers are allowed to operate. Boost will be self reenabled as soon as the output voltage decreases to an acceptable value. The device is equipped with 2 current sense amplifiers. Both have SPI selectable amplifier gain (10, 30, 50 and 100) and output offset voltage level in order to allow max flexibility for phase or ground current sense strategy. All I/O pins are 35 V compatible. Full diagnostic is available through SPI. The device is available in TQFP64 and bare die, according to the application requirements. The device is protected against Shoot Through events. Josoleite Product(s).

# 2 Block diagram and pin description

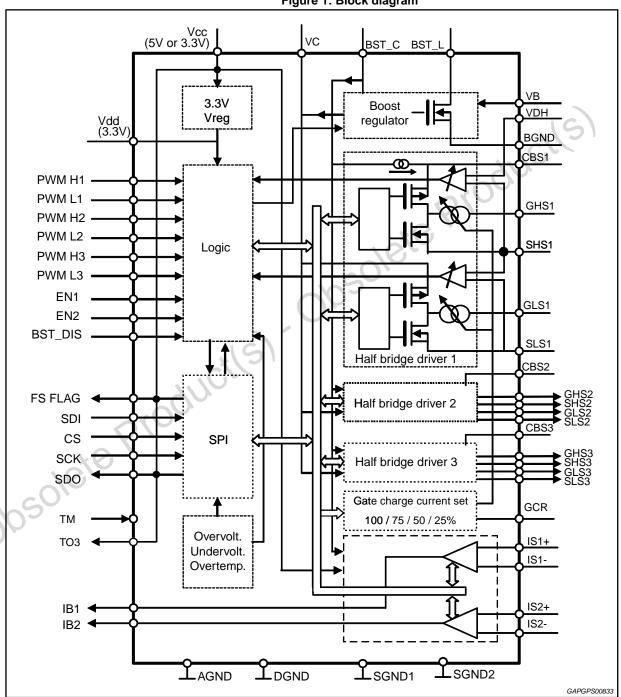

## 2.1 Block diagram

Figure 1: Block diagram

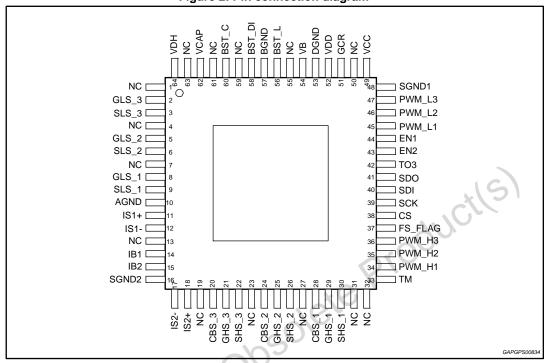

# 2.2 Pin description

Figure 2: Pin connection diagram

**Table 2: Pin function**

| Pin# | Pin name | Description                                                        | I/O Type |

|------|----------|--------------------------------------------------------------------|----------|

| 1    | NC       | NC (S)                                                             |          |

| 2    | GLS_3    | Gate connection for low-side MOSFET, phase 3                       | 0        |

| 3    | SLS_3    | Source connection for low-side MOSFET, phase 3                     | I        |

| 4    | NC       | NC                                                                 | -        |

| 5    | GLS_2    | Gate connection for low-side MOSFET, phase 2                       | 0        |

| 6    | SLS_2    | Source connection for low-side MOSFET, phase 2                     | I        |

| 7    | NC       | NC                                                                 | -        |

| 8    | GLS_1    | Gate connection for low-side MOSFET, phase 1                       | 0        |

| 9    | SLS_1    | Source connection for low-side MOSFET, phase 1                     | 1        |

| 10   | AGND     | Analog ground                                                      | GND      |

| 11   | IS1+     | Positive input for current sense amplifier 1                       | 1        |

| 12   | IS1-     | Negative input for current sense amplifier 1                       | 1        |

| 13   | NC       | NC                                                                 | ı        |

| 14   | IB1      | Output for current sense amplifier 1 (Test mode digital output #1) | 0        |

| 15   | IB2      | Output for current sense amplifier 2 (Test mode digital output #2) | 0        |

| 16   | SGND2    | Substrate (and ESD_GND) connection 2                               | GND      |

| 17   | IS2-     | Negative input for current sense amplifier 2                       | I        |

| 18   | IS2+     | Positive input for current sense amplifier 2                       | i        |

577

| gram and pin description L99 |                   |                                                                  |          |  |  |  |  |

|------------------------------|-------------------|------------------------------------------------------------------|----------|--|--|--|--|

| Pin#                         | Pin name          | Description                                                      | I/O Type |  |  |  |  |

| 19                           | NC                | NC                                                               | -        |  |  |  |  |

| 20                           | CBS_3             | Bootstrap capacitor for high-side MOSFET, phase 3                | I        |  |  |  |  |

| 21                           | GHS_3             | Gate connection for high-side MOSFET, phase 3                    | 0        |  |  |  |  |

| 22                           | SHS_3             | Source connection for high-side MOSFET, phase 3                  | I        |  |  |  |  |

| 23                           | NC                | NC                                                               | -        |  |  |  |  |

| 24                           | CBS_2             | Bootstrap capacitor for high-side MOSFET, phase 2                | I        |  |  |  |  |

| 25                           | GHS_2             | Gate connection for high-side MOSFET, phase 2                    | 0        |  |  |  |  |

| 26                           | SHS_2             | Source connection for high-side MOSFET, phase 2                  | I        |  |  |  |  |

| 27                           | NC                | NC                                                               |          |  |  |  |  |

| 28                           | CBS_1             | Bootstrap capacitor for high-side MOSFET, phase 1                | 2)       |  |  |  |  |

| 29                           | GHS_1             | Gate connection for high-side MOSFET, phase 1                    | 0        |  |  |  |  |

| 30                           | SHS_1             | Source connection for high-side MOSFET, phase 1                  | I        |  |  |  |  |

| 31                           | NC                | NC                                                               | -        |  |  |  |  |

| 32                           | NC                | NC                                                               | -        |  |  |  |  |

| 33                           | TM <sup>(1)</sup> | Test mode enable input                                           | I        |  |  |  |  |

| 34                           | PWM_H1            | PWM command input for high-side phase 1                          | I        |  |  |  |  |

| 35                           | PWM_H2            | PWM command input for high-side phase 2                          | I        |  |  |  |  |

| 36                           | PWM_H3            | PWM command input for high-side phase 3                          | I        |  |  |  |  |

| 37                           | FS_FLAG           | Fault status flag output                                         | 0        |  |  |  |  |

| 38                           | CS                | SPI chip select input                                            | I        |  |  |  |  |

| 39                           | SCK               | SPI serial clock input                                           | I        |  |  |  |  |

| 40                           | SDI               | SPI Serial data input                                            | I        |  |  |  |  |

| 41                           | SDO               | SPI serial data output                                           | 0        |  |  |  |  |

| 42                           | ТО3               | Test output                                                      | 0        |  |  |  |  |

| 43                           | EN2               | Enable Input 2 (ANDed with EN1 to enable any gate drive output). | I        |  |  |  |  |

| 44                           | EN1               | Enable Input 1 (ANDed with EN2 to enable any gate drive output). | I        |  |  |  |  |

| 45                           | PWM_L1            | PWM command input for low-side phase 1                           | I        |  |  |  |  |

| 46                           | PWM_L2            | PWM command input for low-side phase 2                           | I        |  |  |  |  |

| 47                           | PWM_L3            | PWM command input for low-side phase 3                           | I        |  |  |  |  |

| 48                           | SGND1             | Substrate (and ESD_GND) connection 1                             | GND      |  |  |  |  |

| 49                           | Vcc               | 5 V / 3.3 V power supply input                                   | I        |  |  |  |  |

| 50                           | NC                | NC                                                               | -        |  |  |  |  |

| 51                           | GCR               | Connection to resistor for current selection of gate driver      | 0        |  |  |  |  |

| 52                           | Vdd               | 3.3 V power supply output (for IC internal purpose only)         | 0        |  |  |  |  |

| 53                           | DGND              | Digital ground                                                   | GND      |  |  |  |  |

| 54                           | VB                | Protected battery monitor                                        | I        |  |  |  |  |

| 55                           | NC                | NC .                                                             |          |  |  |  |  |

| 2000171                                                                                                               | Pin# | Pin name | Description                                               | I/O Type |  |  |

|-----------------------------------------------------------------------------------------------------------------------|------|----------|-----------------------------------------------------------|----------|--|--|

|                                                                                                                       | 56   | BST_L    | Boost regulator inductance connection                     | О        |  |  |

|                                                                                                                       | 57   | BGND     | Boost ground                                              | GND      |  |  |

|                                                                                                                       | 58   | BST_DIS  | Boost disable                                             | I        |  |  |

|                                                                                                                       | 59   | NC       | NC NC                                                     | -        |  |  |

|                                                                                                                       | 60   | BST_C    | Boost regulator capacitance connection                    | ı        |  |  |

|                                                                                                                       | 61   | NC       | NC                                                        | -        |  |  |

|                                                                                                                       | 62   | VCAP     | Decoupling capacitor for power supply of low-side drivers | ı        |  |  |

|                                                                                                                       |      |          | 1 2 1                                                     |          |  |  |

|                                                                                                                       | 64   | VDH      | High-side drain voltage sense                             | 1        |  |  |

| 63 NC NC 64 VDH High-side drain voltage sense I  Notes:  (1) TM pin has to be connected to ground in the application. |      |          |                                                           |          |  |  |

# 3 Electrical specifications

## 3.1 Absolute maximum ratings

Maximum ratings are absolute ratings; exceeding any one of these values may cause permanent damage to the integrated circuit.

Table 3: Absolute maximum ratings

|       | Parameter                             | Condition                                                            | Min                 | Max               | Unit |

|-------|---------------------------------------|----------------------------------------------------------------------|---------------------|-------------------|------|

|       | Monitor supply pin                    | Pin VB                                                               | -0.3                | 75                | V    |

|       | ivioriitor suppry piri                | riii vo                                                              | -10                 | 10                | mA   |

|       |                                       | BST_C                                                                | -0.3                | 75                | V    |

|       |                                       | B31_0                                                                | -100                | 100               | mA   |

|       |                                       |                                                                      | -0.3                | 75                | V    |

|       |                                       | Pin: BST_L                                                           | -2.5 <sup>(1)</sup> | 75                | V    |

|       |                                       |                                                                      | -100                | 100               | mA   |

|       | Power supply pins                     | Pin V <sub>cc</sub>                                                  | -0.3                | 35                | V    |

|       |                                       | FIII V <sub>CC</sub>                                                 | -10                 | 25                | mA   |

|       |                                       | Pin V <sub>dd</sub>                                                  | -0.3                | 4.6               | V    |

|       |                                       | FIII V dd                                                            | -10                 | 15                | mA   |

|       |                                       | Pin VCAP                                                             | -0.3                | 20                | V    |

|       | .15                                   | FIII VOAF                                                            | -100                | 100               | mA   |

|       |                                       | PWM_H1 to 3, PWM_L1 to 3, IB1,                                       | -0.3                | 35 <sup>(2)</sup> | V    |

|       | Miscellaneous Analog/Digital I/O pins | IB2, EN1, EN2, FS_FLAG,<br>BST_DIS,TM, CS, SCK, SDI,<br>SDO, TO3     | -10                 | 10                | mA   |

|       | Cata attract calcation nin            | Pin GCR                                                              | -0.3                | 4.6               | V    |

|       | Gate current selection pin            |                                                                      | -10                 | 10                | mA   |

| 7/6   | Current sense amplifier pins          | IS1+,IS1-,IS2+,IS2-                                                  | -7                  | 75                | V    |

| 1250. | Current sense ampliller pins          |                                                                      | -10                 | 10                | mA   |

| Oh    | Differential voltage between ISx +/-  | Abs  ISx+ - ISx-                                                     |                     | 15                | ٧    |

|       | High-side drain sense                 | Pin VDH                                                              | -4                  | 75                | V    |

|       | night-side drain sense                |                                                                      | -10                 | 10                | mA   |

|       |                                       | HS Bootstrap Cap pins: CBS_1 to 3                                    | -0.3                | 75                | V    |

|       |                                       | Differential gate to source HS pins: V(GHS_x) - V(SHS_x), x = 1 to 3 | -0.3                | 20                | V    |

|       | FET driver pins                       | Source HS pins: SHS_1 to 3                                           | -7                  | 75                | V    |

|       |                                       | Source LS pins: SLS_1 to 3                                           | -7                  | 10                | V    |

|       |                                       | Differential gate to source LS pins: V(GLS_x) - V(SLS_x), x = 1 to 3 | -0.3                | 20                | V    |

DocID027507 Rev 2

| Parameter                                    | Condition          | Min  | Max | Unit |

|----------------------------------------------|--------------------|------|-----|------|

| Current sense amplifier differential voltage | BST_C-ISxx         | -0.3 | 75  | V    |

| CND pine                                     | Pins BGND and DGND | -0.3 | 4.6 | V    |

| GND pins                                     | Pin AGND and EP    | -0.3 | 0.3 | V    |

### Notes:

#### **ESD** protection 3.2

**Table 4: ESD protection**

| ESD protection           | Table 4: ESD protection               | odil | cile |      |

|--------------------------|---------------------------------------|------|------|------|

| Parameter                | Condition                             | Min  | Max  | Unit |

| Logic and power pins     | Human body model (HBM) <sup>(1)</sup> | -2   | 2    | kV   |

| FET driver pins          | Human body model                      | -2   | 2    | kV   |

| All pins but corner pins | Charge device model                   | -250 | 250  | V    |

| Corner pins              | Charge device model                   | -750 | 750  | V    |

#### Temperature ranges and thermal data 3.3

Table 5: Temperature ranges and thermal data

| Symbol                 | Parameter                                             | Min | Max | Unit |

|------------------------|-------------------------------------------------------|-----|-----|------|

| 7                      | Operating junction temperature                        | -40 | 150 | °C   |

| T <sub>j</sub>         | 100 hours over lifetime temperature <sup>(1)</sup>    | -   | 175 | °C   |

| T <sub>stg</sub>       | Storage temperature                                   | -55 | 150 | °C   |

| T <sub>ot</sub>        | Thermal shutdown temperature                          | 175 | 205 | °C   |

| T <sub>hys</sub>       | Thermal shudown temperature hysteresis <sup>(2)</sup> | 10  | -   | °C   |

| R <sub>th j-amb</sub>  | Thermal resistance junction-to-ambient (3)            | -   | 23  | °C/W |

| R <sub>th j-case</sub> | Thermal resistance junction-to-case                   | -   | 3   | °C/W |

### Notes:

$<sup>^{(1)}</sup>$ -2.5 V for t < 1  $\mu$ s.

<sup>(2)</sup> In standard battery level application (12 V systems) the I/O pins and Vcc pin can stand a short to battery up to 35 V. A short to 35 V battery on any I/O pin also forces the Vcc to approximately 35 V. Care must be taken in order to avoid that under such condition the Vcc pin is strongly pulled down to 5 V (or 3.3 V) with a current exceeding the absolute maximum ratings level.

<sup>(1)</sup>HBM according to MIL 883C, Method 3015.7 or EIA/JESD22-A114\_A. HBM with all unzapped pins grounded.

<sup>&</sup>lt;sup>(1)</sup>Functionality is guaranteed, the specified limits may be exceeded.

<sup>&</sup>lt;sup>(2)</sup>Guaranteed by design.

<sup>&</sup>lt;sup>(3)</sup>IC soldered on 2s2p PCB thermally enhanced.

L9907A Package information

#### 4 **Package information**

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: www.st.com. ECOPACK<sup>®</sup> is an ST trademark.

#### 4.1 TQFP64 (10x10x1 mm exp. pad down) package information

**BOTTOM VIEW** D2 D1/4 4x N/4 TIPS △aaa C A-B D △bbbHA-BD 4x C □ ccc C b ddd MAD -0.05 GAUGE PLANE D1 D BAAAAAAAAAAAAAAA SECTION B-B E1/4 WITH PLATING Jbsole te В D1/4 E1 BASE METAL TOP VIEW < GAPGPS03451

Figure 3: TQFP64 (10x10x1 mm exp. pad down) package outline

Table 6: TQFP64 (10x10x1 mm exp. pad down) mechanical data

| Symbol |     | Milimeters |     |     | Inches <sup>(1)</sup> |     |

|--------|-----|------------|-----|-----|-----------------------|-----|

| Symbol | Min | Тур        | Max | Min | Тур                   | Max |

| θ      | 0°  | 3.5°       | 6°  | 0°  | 3.5°                  | 6°  |

| θ1     | 0°  | -          | -   | 0°  | -                     | -   |

| θ2     | 11° | 12°        | 13° | 11° | 12°                   | 13° |

| θ3     | 11° | 12°        | 13° | 11° | 12°                   | 13° |

7278840\_G\_9I

L9907A Package information

|                   |            |            | Package information |           |                       |        |  |  |

|-------------------|------------|------------|---------------------|-----------|-----------------------|--------|--|--|

| Symbol            |            | Milimeters |                     |           | Inches <sup>(1)</sup> |        |  |  |

| Symbol            | Min        | Тур        | Max                 | Min       | Тур                   | Max    |  |  |

| Α                 | -          | -          | 1.2                 | -         | -                     | 0.0472 |  |  |

| A1                | 0.05       | -          | 0.15                | 0.002     | -                     | 0.0059 |  |  |

| A2                | 0.95       | 1          | 1.05                | 0.0374    | 0.0394                | 0.0413 |  |  |

| b                 | 0.17       | 0.22       | 0.27                | 0.0067    | 0.0079                | 0.0091 |  |  |

| b1                | 0.17       | 0.2        | 0.23                | 0.0067    | 0.0079                | 0.0091 |  |  |

| С                 | 0.9        | -          | 0.2                 | 0.0354    | -                     | 0.0079 |  |  |

| c1                | 0.9        | -          | 0.16                | 0.0354    | -                     | 0.0063 |  |  |

| D                 | -          | 12.00 BSC  | -                   | -         | 0.4724 BSC            |        |  |  |

| D1 <sup>(2)</sup> | -          | 10.00 BSC  | -                   | -         | 0.3937 BSC            | (2)    |  |  |

| D2                |            |            | V                   | ARIATION  | 1,10                  |        |  |  |

| е                 | -          | 0.50 BSC   | -                   | -         | 0.0197 BSC            | -      |  |  |

| Е                 | -          | 12.00 BSC  | -                   | -         | 0.4724 BSC            | -      |  |  |

| E1 <sup>(2)</sup> | -          | 10.00 BSC  | -                   | 10.       | 0.3937 BSC            | -      |  |  |

| E2                |            |            | V                   | ARIATION  |                       |        |  |  |

| L                 | 0.45       | 0.6        | 0.75                | 0.0177    | 0.0236                | 0.0295 |  |  |

| L1                | -          | 1.00 REF   | 102                 | -         | 0.0394 REF            | -      |  |  |

| N                 | -          | 64         | ) -                 | -         | 2.5197                | -      |  |  |

| R1                | 0.08       |            | -                   | 0.0031    | -                     | -      |  |  |

| R2                | 0.08       | 4(2)       | 0.2                 | 0.0031    | -                     | 0.0079 |  |  |

| S                 | 0.2        | J          | -                   | 0.0079    | -                     | -      |  |  |

|                   | 0,0        | TOLERANCE  | OF FORM             | AND POSIT | ION                   |        |  |  |

| aaa               | <b>O</b> . | 0.2        | -                   | -         | 0.0079                | -      |  |  |

| bbb               | -          | 0.2        | -                   | -         | 0.0079                | -      |  |  |

| ccc               | -          | 0.08       | -                   | -         | 0.0031                | -      |  |  |

| ddd               | -          | 0.07       | -                   | -         | 0.0028                | -      |  |  |

|                   | VARIATIONS |            |                     |           |                       |        |  |  |

| Option A          |            |            |                     |           |                       |        |  |  |

| D2                | -          | 4.5        | -                   | -         | 0.1772                | -      |  |  |

| E2                | -          | 4.5        | -                   | -         | 0.1772                | -      |  |  |

| Option B          |            |            |                     |           |                       |        |  |  |

| D2                | -          | 6          | -                   | -         | 0.2362                | -      |  |  |

| E2                | -          | 6          | -                   | -         | 0.2362                | -      |  |  |

|                   |            |            |                     |           |                       |        |  |  |

#### **Notes**

<sup>&</sup>lt;sup>(2)</sup>Dimensions D1 and E1 do not include mold flash or protrusions. Allowable mold flash or protrusion is "0.25 mm" per side.

$<sup>\</sup>ensuremath{^{(1)}}\mbox{Values}$  in inches are converted from mm and rounded to 4 decimal digits.

Revision history L9907A

# 5 Revision history

**Table 7: Document revision history**

| Date        | Revision | Changes                                                                                     |

|-------------|----------|---------------------------------------------------------------------------------------------|

| 16-Feb-2015 | 1        | Initial release.                                                                            |

| 23-Feb-2015 | 2        | Updated supply voltage from 35 V to 36 V for working in 24 V system, in Section "Features". |

Obsolete Product(s). Obsolete Product(s)

### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2015 STMicroelectronics – All rights reserved