## AC measurements on op amps

## Introduction

The aim of this application note is to first review the main characteristics of an operational amplifier in the frequency domain, and then explain how these characteristics can be measured.

# 1 Main AC characteristics: GPB, FU, phase margin and gain margin

## 1.1 Frequency response of an op amp in open-loop

In order to analyze the op amp frequency response and the potential stability of the op amp in a closed-loop system, we first consider the open-loop response on the Bode diagram. The frequency response can be modeled with its open-loop gain  $A(\omega)$ :

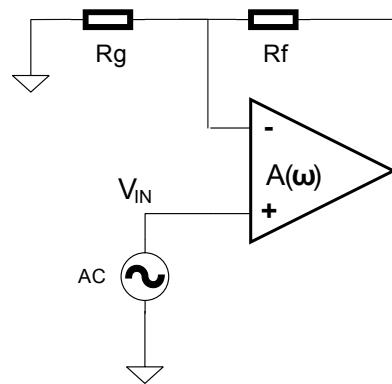

Figure 1. Simplified op amp AC model schematic

$$A(\omega) = \frac{V_{OUT}}{V_+ - V_-} \quad (1)$$

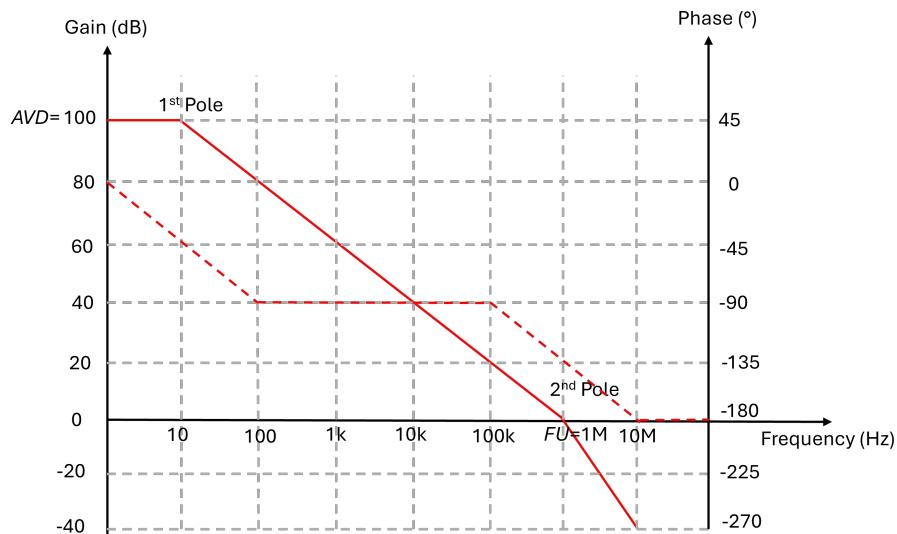

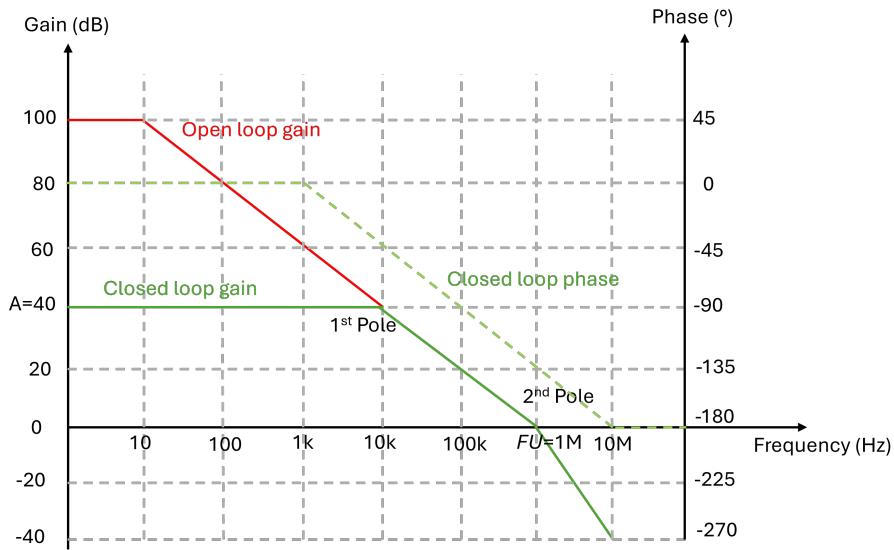

Most modern op amps have a Bode diagram similar to the one shown in Figure 2. At low frequency, the open-loop gain of the amplifier is very high and corresponds to the static AVD documented in the datasheet. Then, we have a first pole followed by a region where the gain drops at 20 dB per decade. This is due to the compensation of the op amp by an internal capacitor called the Miller capacitor, leading to a behavior similar to that of a first order filter.

Figure 2. Schematic Bode diagram of an op amp in open-loop

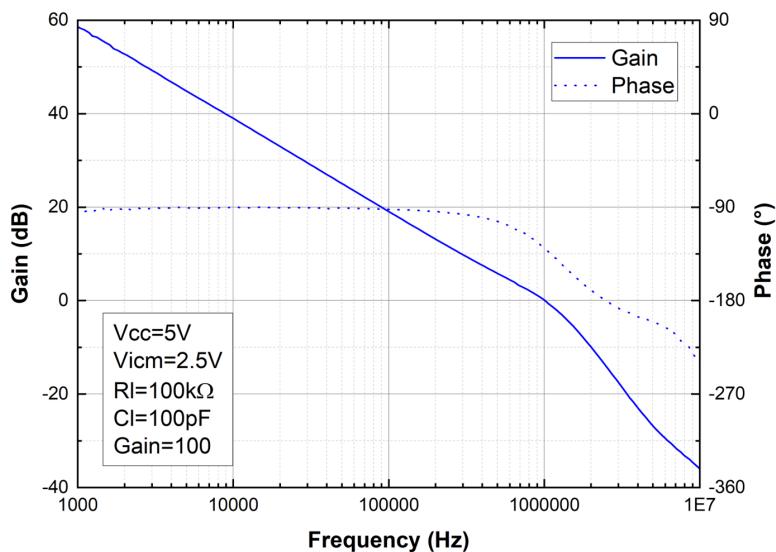

Figure 3. Actual Bode diagram of TSV631 in open-loop

In this region, the product of the gain (A) and the bandwidth (f) is a constant:

$$GBP = A \cdot f \quad (2)$$

At the point where the gain  $A = 1$  (0 dB), the corresponding frequency is called the unity-gain frequency (FU). If the decrease of the gain is strictly 20 dB per decade down to unity gain, the FU value is equal to the GBP.

Then, the decrease of the gain with frequency increases to 40 dB per decade after a second pole of the Bode diagram. This second order behavior is generally a function of the capacitance seen at the output of the op amp, as a combination of the internal output capacitance of the circuit, and the load capacitance added at the output. When this output capacitance is low, the second pole is generally after the FU, but as the load capacitance is increased, the second pole occurs at a lower frequency.

This is why the Bode diagram and the AC characteristics of an op amp are always given for a precise load capacitance value, intended to mimic the parasitic capacitances seen by the op amp in a real application.

## 1.2

### Phase margin and gain margin

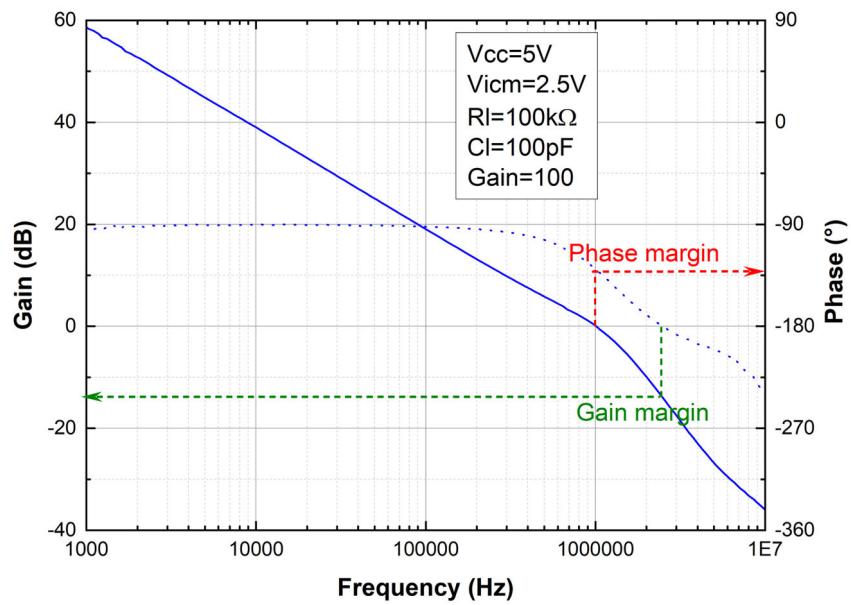

Unlike a perfect op amp where the frequency response would be infinite and the output signal would be in phase with the differential input, each pole introduce a  $90^\circ$  phase rotation, as seen in Figure 2 and Figure 3. This has an impact on the stability of the system. Indeed, when the phase is rotated by  $180^\circ$ , the negative feedback stabilizing a closed-loop system is turned into positive feedback. If this happens at a frequency where the gain of the circuit is greater than 1, the circuit will be unstable.

This is why the phase margin and gain margin are introduced as indicators of system stability. The phase margin is defined as the difference between the phase value and  $-180^\circ$  when the gain is 1 (0 dB). The gain margin is the gain value when the phase reaches  $-180^\circ$ .

If the phase margin is negative, and the gain margin greater than 0 dB, the circuit is unstable. A usual criterion for very good stability is a phase margin  $> 45^\circ$ , and a gain margin  $> 10$  dB.

Figure 4. Phase margin and gain margin measurements on TSV631 Bode diagram

## 2

## AC characteristics of an op amp in closed-loop

The open-loop frequency response is practically never observed directly, as the op amp is not stable in open-loop, so this figure is theoretical. The closed-loop frequency, however, can be measured, and in our work, the aim of the measurement on a closed-loop circuit is to be able to measure AC characteristics as close as possible to the open-loop characteristics.

## 2.1

## Case of the non-inverting circuit

Figure 5. Schematic of the non-inverting op amp circuit

With:

$$V_{OUT} = A \cdot (V_+ - V_-) \quad (3)$$

$$V_- = V_{OUT} \cdot \frac{R_G}{R_G + R_F} \quad (4)$$

We can demonstrate:

$$\frac{V_{OUT}}{V_{IN}} = \frac{A}{1 + \frac{A}{1 + \frac{R_F}{R_G}}} \quad (5)$$

And with  $G = 1 + \frac{R_F}{R_G}$ :

$$\frac{V_{OUT}}{V_{IN}} = \frac{A}{1 + \frac{A}{G}} \quad (6)$$

At very low frequencies when

$$A \gg 1 + \frac{R_F}{R_G}, \text{ and so } \frac{A}{G} \gg 1,$$

The gain can be expressed:

$$\frac{V_{OUT}}{V_{IN}} = G \quad (7)$$

When the op amp is set in gain, the gain of this system is limited at low frequencies to the circuit gain, set by the resistors. Consequently, the AVD value cannot be reached.

However, for higher frequencies when  $A \ll 1 + \frac{R_F}{R_G}$ , and therefore  $\frac{A}{G} \ll 1$ ,

We have  $\frac{V_{OUT}}{V_{IN}} = A$

The response will be limited by the op amp's frequency limitation described in the previous paragraph. So the GBP and the FU will be observable (see Figure 4).

Figure 6. Schematic Bode diagram of an op amp in closed-loop

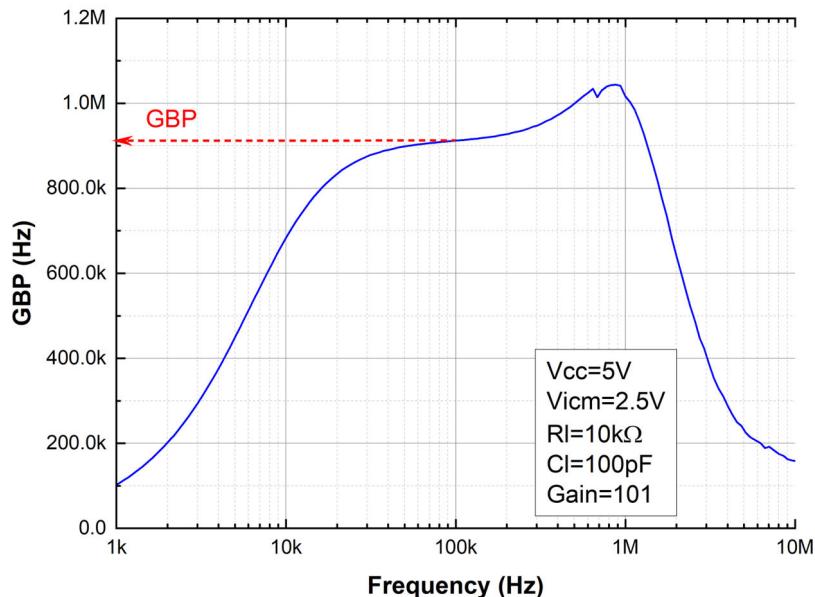

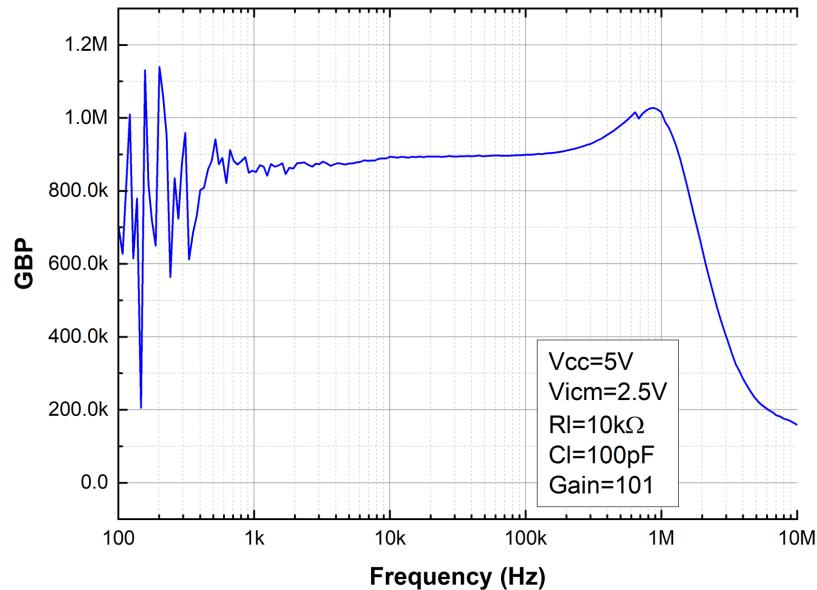

As observed in the open-loop bode diagram, the GBP is constant and can be measured at any point in the -20 dB per decade part of the characteristic, between the 1<sup>st</sup> and 2<sup>nd</sup> poles.

Practically, on a real op amp, the GBP measurement point should be chosen far enough from the poles, to avoid the gain decrease they induce, as shown in Figure 5

Figure 7. GBP vs. frequency on TSV631

In case the second pole is well after the gain = 1 (0 dB) crossing point, the GBP and FU value should theoretically be identical. However, the second pole is usually close enough to the 0 dB crossing so that the FU is slightly lower than the GBP.

Some op amps use a more complex architecture leading to a different poles/zeros structure, and do not have a strict 20 dB per decade slope. In this case, the GBP is usually measured in the 20 dB per decade region at low frequency, but it is not significant for a low-gain application. Also, the FU in this case is very different from the GBP value.

In order to be able to approximate the intrinsic (open loop) AC characteristics of an op amp with a closed loop measurement correctly, the resistors of the circuit have to be chosen so that the gain of the circuit is large enough to fulfill the previously described condition:

$$A \ll 1 + \frac{R_F}{R_G} \quad (8)$$

The higher the circuit gain is, the closer to the open-loop values the measurements will be.

By definition, the phase margin is measured with  $A = 1$ , so the value of  $G = 100$  is often considered as sufficient. However, there is still a small residual error on the phase margin. A higher gain value can further reduce the error, but may introduce another issue that will be explained in [Section 5.1](#).

## 2.2 Case of the inverting circuit

Figure 8. Schematic of the inverting op amp circuit

With:

$$V_{OUT} = A \cdot (V_+ - V_-) \quad (9)$$

$$V_- = V_{IN} \cdot \frac{R_F}{R_G + R_F} + V_{OUT} \cdot \frac{R_G}{R_G + R_F} \quad (10)$$

We can demonstrate:

$$\frac{V_{OUT}}{V_{IN}} = \frac{-R_F}{\frac{R_F + R_G}{A} + R_G} \quad (11)$$

If  $A \gg R_F + R_G$ , then

$$\frac{V_{OUT}}{V_{IN}} = G = \frac{-R_F}{R_G} \quad (12)$$

If  $A \ll 1 + \frac{R_F}{R_G}$  and therefore  $\frac{R_F + R_G}{A} \gg R_G$ ,

$$\frac{V_{OUT}}{V_{IN}} = A \cdot \frac{-R_F}{R_F + R_G} \quad (13)$$

In conclusion, when the gain is large, we indeed have  $\frac{V_{OUT}}{V_{IN}} \sim -A$ . However, there is a small error when the schematic is inverting, which is not present when the op amp is not inverting. The non-inverting schematic is therefore preferable.

## 2.3

## Impact of the output impedance: non-inverting

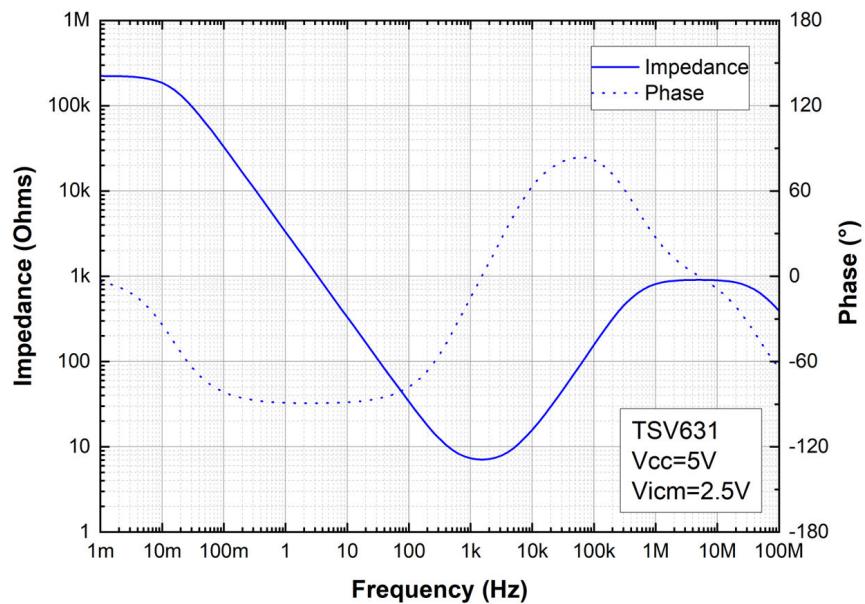

In the previous paragraphs, we have considered the op amp output impedance to be null. This is, however, not fully the case. Modern op amps usually have an output impedance that varies with the frequency. However, the impedance values can have very different values from one op amp to another, depending on the bandwidth and the design of the output stage. Figure 9 shows the output impedance of the TSV631:

Figure 9. TSV631 open-loop output impedance

This behavior is typical of modern op amps with a capacitive behavior at low frequencies, followed by an inductive behavior before the GBP. The value of interest for our analysis is mainly the impedance at GBP (900 kHz for the TSV631). This value depends on the op amp model, and, generally speaking, high-bandwidth op amps tend to have a lower output impedance.

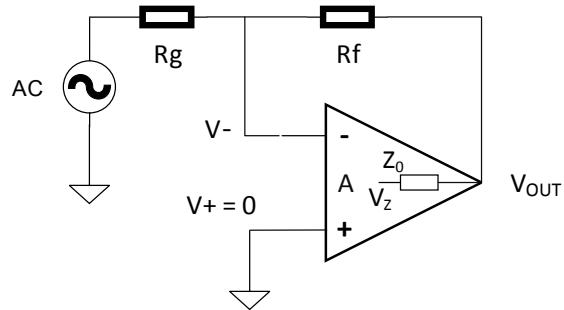

We can calculate the impact of a non-null output impedance ( $Z_0$ ) in the case of a non-inverting circuit as follows:

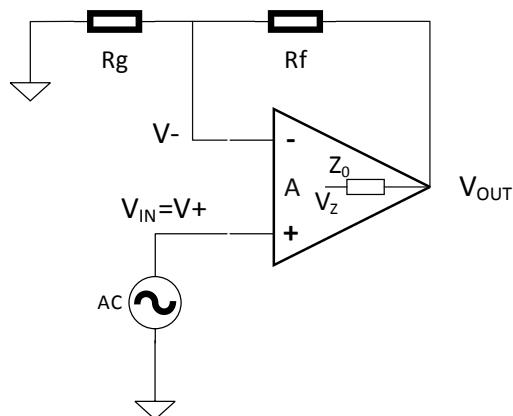

Figure 10. Schematic of the non-inverting op amp circuit with output impedance

With:

$$V_z = A \cdot (V_+ - V_-) \quad (14)$$

$$G = 1 + \frac{R_f}{R_g} \quad (15)$$

We can demonstrate:

$$\frac{V_{OUT}}{V_{IN}} = \frac{A}{1 + \frac{A}{G} + \frac{Z_0}{R_G + R_F}} \quad (16)$$

With  $G = 1 + \frac{R_F}{R_G}$

In the frequency region where  $A$  is very large, the term  $\frac{Z_0}{R_G + R_F}$  can most likely be neglected. However, in the region of interest for the phase and gain margin measurements where  $A \leq 1$ , we need the condition  $Z_0 \ll R_G + R_F$  to be fulfilled in order to be able to neglect the output impedance effect.

In our example for the TSV631, at FU f = 900 kHz, the open-loop output impedance is approximately 800  $\Omega$ . With typical resistor values  $R_F = 10 \text{ k}\Omega$  and  $R_G = 100 \Omega$ , the error on the phase margin introduced will probably be negligible, but maximizing the  $R_F$  and  $R_G$  resistor values will lower the impact of the output impedance.

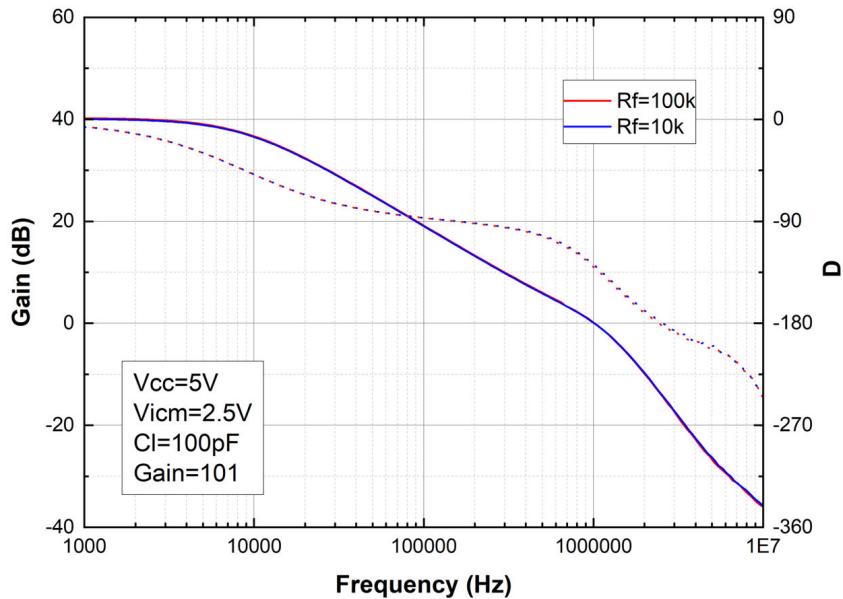

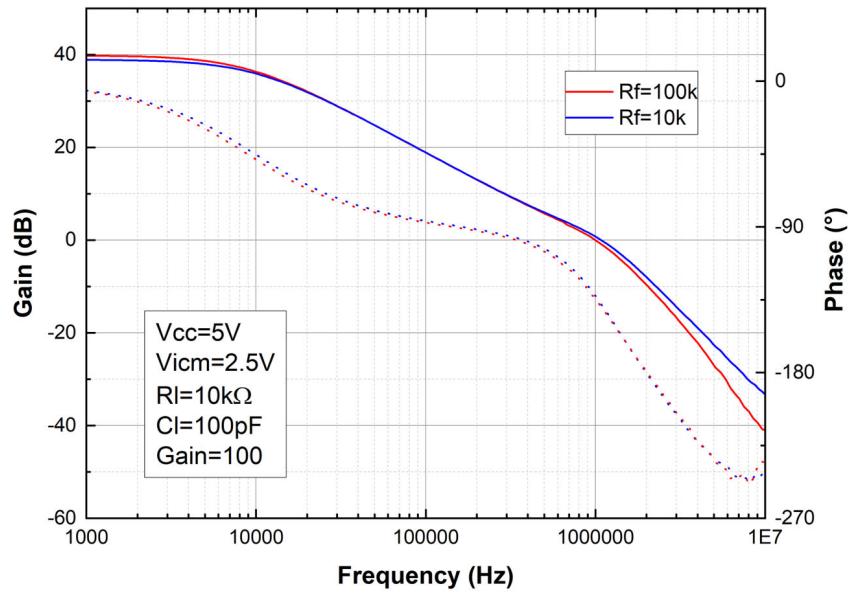

Figure 11 shows the Bode diagram in closed-loop for gain 101 with  $R_F = 100 \text{ k}\Omega$ ,  $R_G = 1 \text{ k}\Omega$  and for  $R_F = 10 \text{ k}\Omega$ ,  $R_G = 100 \Omega$ . There is no difference, confirming that the output impedance introduces no significant error for this op amp with these resistor values. However, the analysis should be carried out for each op amp model.

**Figure 11. Closed-loop Bode measurement of TSV631 in non-inverting configuration**

## 2.4

## Impact of the output impedance: inverting

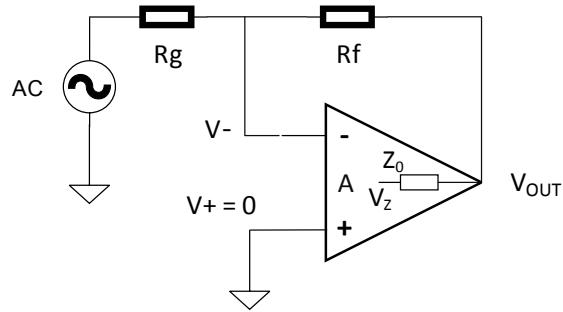

We can run the same analysis for the inverting configuration.

Figure 12. Schematic of the inverting op amp circuit with output impedance

With:

$$V_z = A \cdot (V_+ - V_-) \quad (17)$$

We can demonstrate:

$$\frac{V_{OUT}}{V_{IN}} = \frac{\frac{Z_0}{R_G + R_F} - A \cdot \frac{R_F}{R_G + R_F}}{1 + \frac{Z_0}{R_G + R_F} + A \cdot \frac{R_G}{R_G + R_F}} \quad (18)$$

In the frequency region where  $A$  is very large, the term  $\frac{Z_0}{R_G + R_F}$  can most likely be neglected and the equation reduces to the case of [Section 2.2](#):

$$\frac{V_{OUT}}{V_{IN}} = A \cdot \frac{-R_F}{R_G} \quad (19)$$

However, in the region of interest for the phase and gain margin measurements where  $A \sim 1$ , the condition  $Z_0 \ll R_G + R_F$  is not sufficient to neglect the output impedance. Indeed, the numerator term gives:

$$\frac{Z_0}{R_G + R_F} \ll A \cdot \frac{R_F}{R_G + R_F} \text{ With } \frac{R_F}{R_G + R_F} \sim 1, \text{ so}$$

$$\frac{Z_0}{R_G + R_F} \ll A \quad (20)$$

In our example for the TSV631, at  $f = 900$  kHz,  $Z_0 \sim 800 \Omega$ . With typical resistor values  $R_F = 10 \text{ k}\Omega$  and  $R_G = 100 \Omega$ , the error on the phase margin introduced will not be negligible. This error is difficult to evaluate with the equation as  $Z_0$  is a complex impedance and also introduces a phase rotation, but maximizing the  $R_F$  and  $R_G$  resistor values will lower the impact of the output impedance.

Figure 13. Closed-loop Bode measurement of TSV631 in inverting configuration

Obviously here, the phase and gain margin measurements are different with the two resistor sets.

To summarize the results for both inverting and non-inverting configurations:

Table 1. AC measurements in closed-loop on TSV631

|               |                         | GBP (kHz) | FU (kHz) | Phase margin (°) | Gain margin (dB) |

|---------------|-------------------------|-----------|----------|------------------|------------------|

| Non-Inverting | R <sub>F</sub> = 10 kΩ  | 896       | 1013     | 51.2             | 14.1             |

|               | R <sub>F</sub> = 100 kΩ | 911       | 1013     | 49.1             | 13.3             |

| Inverting     | R <sub>F</sub> = 10 kΩ  | 880       | 1083     | 42.2             | 7.9              |

|               | R <sub>F</sub> = 100 kΩ | 879       | 996      | 45.6             | 9.6              |

We can conclude that the error introduced by the output impedance is much lower with a non-inverting configuration. In an inverting configuration, the errors on both the phase margin and on the gain margin are quite high. The GBP is also slightly lower than in a non-inverting configuration.

So, generally speaking, it is advised to use a non-inverting configuration.

### 3 Stability and output capacitance

As explained in [Section 1.1](#), the second pole in the Bode diagram is linked not only to the circuit itself, but also to the external capacitance seen by the circuit output. Indeed, the second observable pole on the op amp gain is a combination of the output impedance and the external capacitance  $C_L$  seen by the op amp output with:

$$f_c = \frac{1}{2\pi Z_0 C_L} \quad (21)$$

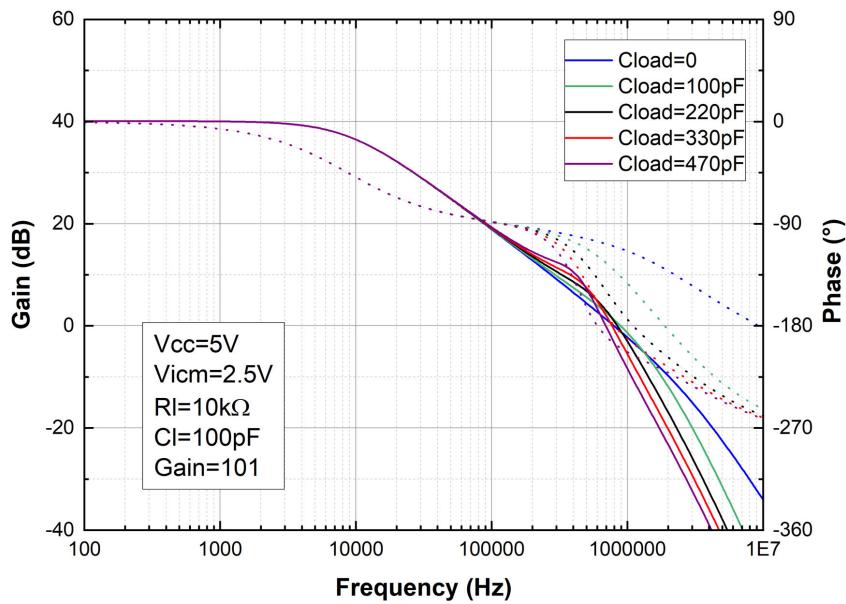

The higher the output capacitance, the lower the pole frequency. Thus, a higher capacitive load usually reduces the stability of the circuit and lowers the phase and gain margin. This is illustrated in [Figure 14](#).

**Figure 14. Closed-loop Bode simulation of TSV631 in non-inverting configuration**

**Table 2. Closed-loop Bode simulation of TSV631 in non-inverting configuration**

| Cload (pF) | GBP (kHz) | FU (kHz) | Phase margin (°) | Gain margin (dB) |

|------------|-----------|----------|------------------|------------------|

| 0          | 880       | 800      | 70               | 33               |

| 100        | 888       | 890      | 44               | 11               |

| 220        | 897       | 840      | 18               | 5                |

| 330        | 908       | 766      | 3                | 1                |

| 470        | 918       | 691      | -8               | -3               |

Characterizing the AC characteristics of an op amp, it is essential to take into account the parasitic capacitances introduced by the measurement system: board layout, cables and measurement instruments.

## 4 Stability and input capacitance

The capacitance at the op amp input also plays a role in the op amp stability. This capacitance is composed of the intrinsic capacitance of the op amp inputs (typically a few pF), and the parasitics (board trace, coaxial cables and so on) plugged directly into the input.

This capacitance has an impact on the op amp stability because it can alter the feedback voltage  $V_-$ .

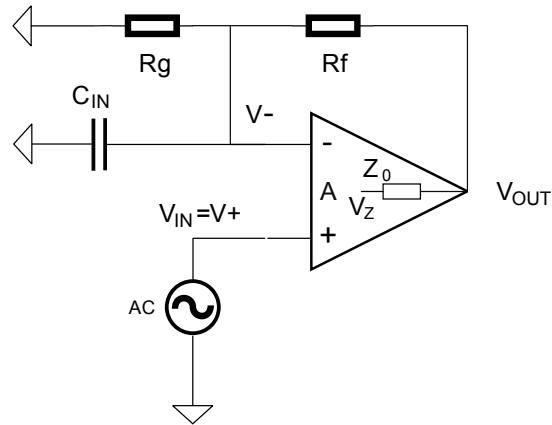

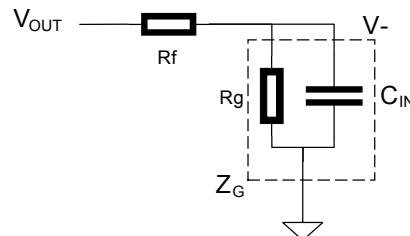

**Figure 15. Schematic of the non-inverting op amp circuit with simplified input impedance**

As compared to the ideal case where  $C_{IN}$  is negligible, let's consider an impedance  $Z_G$  constituted of  $R_G$  and  $C_{IN}$  in parallel:

**Figure 16. Simplified schematic of the impedance seen by the op amp output**

We can express the feedback transfer function with:

$$\frac{V_-}{V_{OUT}} = \frac{Z_G}{Z_G + R_F} \quad (22)$$

With  $Z_G = \frac{1}{jC_{IN}\omega + \frac{1}{R_G}}$ ,

$$\frac{V_-}{V_{OUT}} = \frac{R_G}{R_G + R_F + jR_G R_F C_{IN} \omega} \quad (23)$$

Finally, the input capacitance will be negligible if  $R_G R_F C_{IN} \omega \ll R_G + R_F$

So,

$$C_{IN} \ll \frac{R_G + R_F}{R_G R_F \cdot 2\pi f} \quad (24)$$

The input capacitance will NOT be negligible when:

- The gain is low (but, as previously stated, it is not a suitable configuration for AC measurements)

- The resistor values are high

- And, of course, if the capacitance value is high.

Practically, the input capacitance should not be a concern for moderate-bandwidth op amps. Indeed, for the TSV631 at  $F_U$  (900 kHz), with  $R_F = 100$  k and  $R_G = 1$  k, the  $C_{IN}$  should be lower than 180 pF. As both the parasitic input capacitances and the board parasitic are usually in the few pF range, this should not be an issue. However, connecting a scope input with a coaxial cable directly to the op amp input would impact the stability. Therefore, using a low capacitance probe is recommended.

## 5 Practical measurement considerations

### 5.1

#### Hardware setup and measurement conditions

The general principle of the Bode measurement is to provide a small sine at the input of the DUT, and measure the gain and phase at the output.

Such a measurement can be done with a sine generator and an oscilloscope, measuring the amplitude of the input and output signals, and the outphasing between them. In the case of an op amp with a very low GBP, where measurements below 10 Hz can be necessary and dedicated analyzers are hard to find, this may be the best option. Sine generators with a small amplitude can be difficult to find, but a signal attenuator can be used.

However, it is more convenient to use a network analyzer as it integrates the small sine source and the measurement, and is able to compute and display the gain and phase. Only the forward transmitted signal (S21) will be used to plot the Bode diagram. So, the network analyzers dedicated to Bode measurements at low frequencies are often not able to measure the reverse S-parameters because no signal source is available at the output port.

Although any network analyzer should be able to measure the Bode plot of an op amp, most VNA (vector network analyzers) available on the market are not able to operate a low enough frequency for usual op amps. As analyzers able to operate at such frequencies are difficult to find today, or discontinued by the equipment suppliers, the best solution is to use oscilloscopes with an integrated or piloted voltage source and a dedicated integrated software for spectral analysis.

When characterizing usual op amps with a GBP < 10 MHz, it is not necessary to perform open, short and load calibrations, as the extracted parasitic effects are negligible at these frequencies. Unless abnormal attenuation on the signal path or excessively long cables are present, it is also not necessary to perform a thorough calibration. Indeed, as long as the total cable signal length is negligible versus the electrical length, no signal distortion or outphasing are seen.

The input amplitude should be low enough to ensure that:

- The op amp output does not saturate, given the circuit gain and the characteristics of the output stage. The possible value of the input offset (also amplified by the circuit gain) should also be taken into account.

- The op amp stays in a linear regime, where  $V+ \sim V-$ . If the output voltage variation is close to the slew-rate, this condition is not fulfilled anymore.  $V_{IN}$  should be kept lower than  $V_{IN,max} = \frac{2 \cdot \pi \cdot f}{SR \cdot Gain}$ .

#### Network analyzers and instrument input impedance

The input impedance of network analysis is usually  $50 \Omega$ , which is not compatible with most op amps. Indeed, the output stage is usually not capable of driving such a low impedance. So, an active probe with a high impedance is needed.

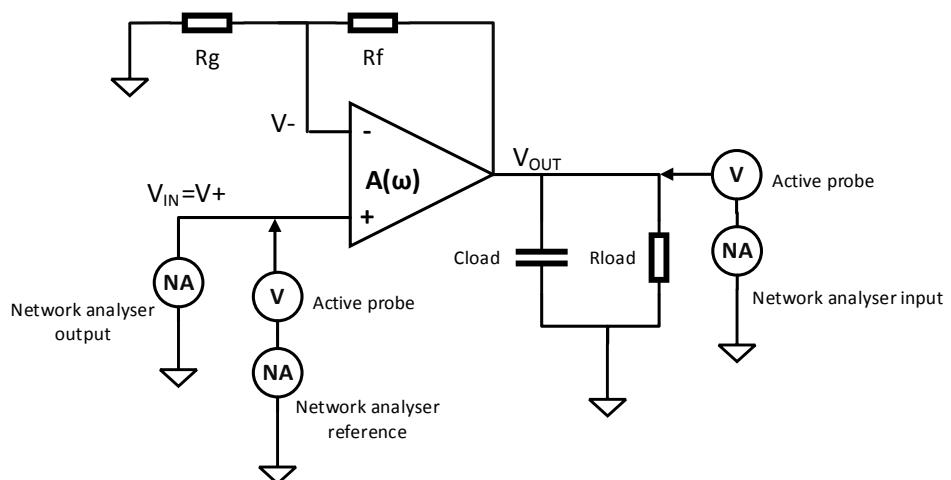

**Figure 17.** Schematic of the op amp AC measurement using a network analyzer and high-impedance signal probes

The parasitic capacitance of this type of probe is usually low, but should be considered in the probe choice, and in the definition of the  $C_{load}$  value.

In case an oscilloscope coupled to a frequency generator is used, it can usually be switched to high-impedance input, which allows the op amp output to drive the oscilloscope input directly without an additional probe. However, the parasitic capacitance of the scope input can be high, and the cable parasitics also has to be taken into account.

## 5.2

### Frequency generator output impedance

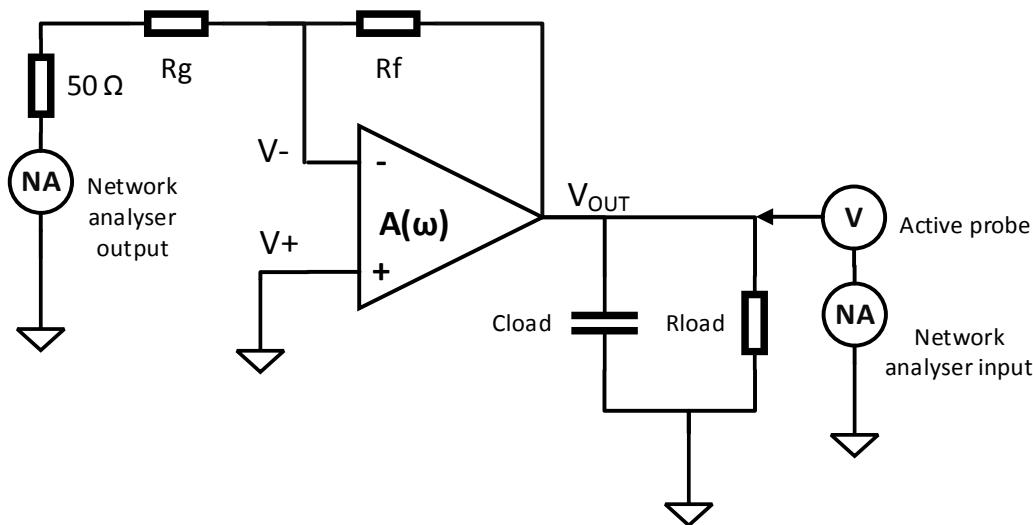

When using a inverting circuit (although this is not recommended), the output impedance can interfere with the circuit schematic. Indeed, in most cases the frequency generator has a  $50\ \Omega$  output impedance than should be taken into account to compute the circuit gain.

**Figure 18. Schematic of the op amp AC measurement, impact of the signal generator output impedance**

However, as the circuit gain and  $R_g$  value are not directly needed to compute the op amp AC parameters, this effect can usually be neglected.

## 5.3

**Closed-loop or pseudo-open-loop?**

A perfect op amp with inputs polarized at the same bias would have its output at the same voltage. However, with a real op amp with a non-null  $V_{IO}$ , the  $V_{OUT}$  is:

$$V_{OUT,DC} = V_{IO} \cdot A(f = 0) \quad (25)$$

Given the large value of the gain  $A$  in DC, the output is saturated either at high or low rail, and AC measurements are not possible in this configuration.

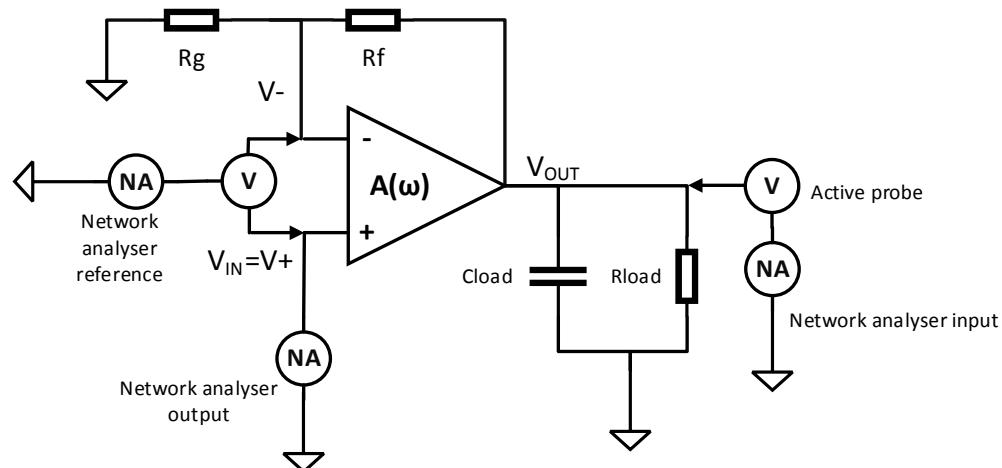

A negative feedback path is mandatory to properly polarize the op amp in DC, which is why measurements are carried out in closed-loop with a large gain. However, even in a closed-loop configuration, it is possible to measure the open-loop response of the op amp by going back to the definition of the open-loop gain:

$$A(\omega) = \frac{V_{OUT}}{V_+ - V_-} \quad (26)$$

Two probes should be used, one (either differential or not) connected to the output, and one differential probe between the positive and negative inputs.

On a network analyzer with a reference input, this is straightforward as the signal actually analyzed is Input/Reference. On an oscilloscope with Bode functionality, it is usually possible to perform such a numerical operation between the two probes signal.

**Figure 19. Schematic of the op amp AC measurement in pseudo-open-loop**

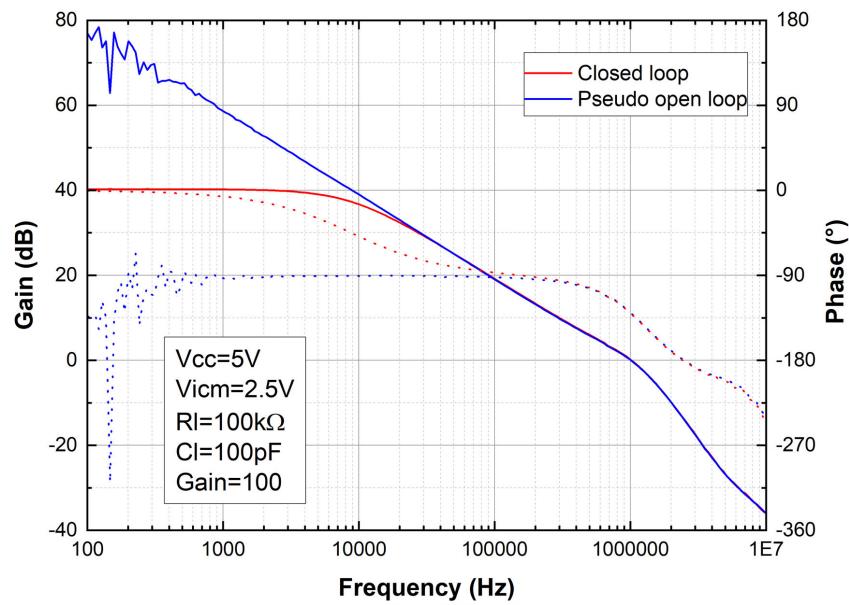

Figure 20. Measurements of the TSV631 in closed-loop and pseudo-open-loop

In the high-gain region, the pseudo-open-loop measurement allows to measure the op amp intrinsic gain even for a gain larger than the circuit gain. It is also possible to get rid of the gain condition stated in Section 2.1, and perform the measurement for a low circuit gain. However, for a very large op amp gain the measurement starts to be noisy because the signal measured by the probe is very low. Indeed, from equations 1 and 7 we can write:

$$V_+ - V_- = \frac{V_{IN}}{1 + \frac{A}{G}} \quad (27)$$

When  $A$  is large, the signal  $V_+ - V_-$  is small. For this reason, it is usually not possible to measure constant DC gain regions at very low frequencies for modern op amps, with a DC gain usually well above 100 dB. This is even more problematic when the gain  $G$  is low, so using a large circuit gain is also advised here.

However, pseudo-open-loop measurement can be useful because it allows to access the op amp intrinsic gain for a frequency range larger than the usual closed-loop measurement, and independent of the circuit gain set by the resistors values. As shown in Figure 21, the frequency range where the GBP is stable is much larger than in closed-loop measurement (Figure 7), making it easier to achieve a reliable GBP measurement.

**Figure 21. Measurements of the TSV631 GBP versus frequency in pseudo-open-loop**

## 5.4

### Board design

In order to measure the AC characteristics of op amps with a GBP lower than 10 MHz, no specific board design is needed. However, it is useful to:

- Reduce the trace lengths in order to reduce the parasitics between the op amp and the gain resistors, and lower the noise.

- Decouple the power supply as close as possible to the op amp.

- Calibrate the parasitic capacitance seen by the op amp on its output. Indeed, as the phase and gain margins are largely dependent on the capacitive load, these parasitics have to be taken into account in the total capacitive load.

The STEVAL-CCA057V01 to V05 boards available on the STMicroelectronics website (st.com) for commonly used packages (SOT23-5, MiniSO-8, SO-8, DFN8) are very well suited for this purpose.

Figure 22. STEVAL-CCA057V1 for SO-8 package

## 6 Conclusion

General principles and theory for the measurement of op amps AC characteristics (gain-bandwidth product, unity frequency, phase margin and gain margin) are given. Practical measurement methodologies and schematics are provided. These techniques can usually be used for op amps with a GBP of up to 10 MHz. For higher frequencies, these methodologies need to be adapted – please consult the application note “AC measurements on high-speed op amps” [AN6369](#).

## 7

## References

---

- [Datasheet TSV631](#)

- [Op-amps prototyping boards](#)

## Revision history

**Table 3. Document revision history**

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 20-Jan-2026 | 1       | Initial release. |

## Contents

|          |                                                                            |           |

|----------|----------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Main AC characteristics: GPB, FU, phase margin and gain margin.....</b> | <b>2</b>  |

| 1.1      | Frequency response of an op amp in open-loop.....                          | 2         |

| 1.2      | Phase margin and gain margin .....                                         | 3         |

| <b>2</b> | <b>AC characteristics of an op amp in closed-loop .....</b>                | <b>5</b>  |

| 2.1      | Case of the non-inverting circuit .....                                    | 5         |

| 2.2      | Case of the inverting circuit .....                                        | 8         |

| 2.3      | Impact of the output impedance: non-inverting .....                        | 9         |

| 2.4      | Impact of the output impedance: inverting .....                            | 11        |

| <b>3</b> | <b>Stability and output capacitance .....</b>                              | <b>13</b> |

| <b>4</b> | <b>Stability and input capacitance .....</b>                               | <b>14</b> |

| <b>5</b> | <b>Practical measurement considerations.....</b>                           | <b>16</b> |

| 5.1      | Hardware setup and measurement conditions .....                            | 16        |

| 5.2      | Frequency generator output impedance.....                                  | 17        |

| 5.3      | Closed-loop or pseudo-open-loop?.....                                      | 18        |

| 5.4      | Board design .....                                                         | 21        |

| <b>6</b> | <b>Conclusion .....</b>                                                    | <b>22</b> |

| <b>7</b> | <b>References .....</b>                                                    | <b>23</b> |

|          | <b>Revision history .....</b>                                              | <b>24</b> |

## List of tables

|                                                                                                |    |

|------------------------------------------------------------------------------------------------|----|

| <b>Table 1.</b> AC measurements in closed-loop on TSV631 . . . . .                             | 12 |

| <b>Table 2.</b> Closed-loop Bode simulation of TSV631 in non-inverting configuration . . . . . | 13 |

| <b>Table 3.</b> Document revision history . . . . .                                            | 24 |

## List of figures

|                   |                                                                                                            |    |

|-------------------|------------------------------------------------------------------------------------------------------------|----|

| <b>Figure 1.</b>  | Simplified op amp AC model schematic . . . . .                                                             | 2  |

| <b>Figure 2.</b>  | Schematic Bode diagram of an op amp in open-loop . . . . .                                                 | 2  |

| <b>Figure 3.</b>  | Actual Bode diagram of TSV631 in open-loop . . . . .                                                       | 3  |

| <b>Figure 4.</b>  | Phase margin and gain margin measurements on TSV631 Bode diagram . . . . .                                 | 4  |

| <b>Figure 5.</b>  | Schematic of the non-inverting op amp circuit . . . . .                                                    | 5  |

| <b>Figure 6.</b>  | Schematic Bode diagram of an op amp in closed-loop . . . . .                                               | 6  |

| <b>Figure 7.</b>  | GBP vs. frequency on TSV631 . . . . .                                                                      | 6  |

| <b>Figure 8.</b>  | Schematic of the inverting op amp circuit . . . . .                                                        | 8  |

| <b>Figure 9.</b>  | TSV631 open-loop output impedance . . . . .                                                                | 9  |

| <b>Figure 10.</b> | Schematic of the non-inverting op amp circuit with output impedance . . . . .                              | 9  |

| <b>Figure 11.</b> | Closed-loop Bode measurement of TSV631 in non-inverting configuration . . . . .                            | 10 |

| <b>Figure 12.</b> | Schematic of the inverting op amp circuit with output impedance . . . . .                                  | 11 |

| <b>Figure 13.</b> | Closed-loop Bode measurement of TSV631 in inverting configuration . . . . .                                | 12 |

| <b>Figure 14.</b> | Closed-loop Bode simulation of TSV631 in non-inverting configuration . . . . .                             | 13 |

| <b>Figure 15.</b> | Schematic of the non-inverting op amp circuit with simplified input impedance . . . . .                    | 14 |

| <b>Figure 16.</b> | Simplified schematic of the impedance seen by the op amp output . . . . .                                  | 14 |

| <b>Figure 17.</b> | Schematic of the op amp AC measurement using a network analyzer and high-impedance signal probes . . . . . | 16 |

| <b>Figure 18.</b> | Schematic of the op amp AC measurement, impact of the signal generator output impedance . . . . .          | 17 |

| <b>Figure 19.</b> | Schematic of the op amp AC measurement in pseudo-open-loop . . . . .                                       | 18 |

| <b>Figure 20.</b> | Measurements of the TSV631 in closed-loop and pseudo-open-loop . . . . .                                   | 19 |

| <b>Figure 21.</b> | Measurements of the TSV631 GBP versus frequency in pseudo-open-loop . . . . .                              | 20 |

| <b>Figure 22.</b> | STEVAL-CCA057V1 for SO-8 package . . . . .                                                                 | 21 |

**IMPORTANT NOTICE – READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to [www.st.com/trademarks](http://www.st.com/trademarks). All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2026 STMicroelectronics – All rights reserved