Application note

# Guidelines to select the right IPD BALFHB/LB-WL-0xD3 for STM32WL5x/Ex reference design

#### Introduction

This application note is dedicated to selecting the right IPD BALFHB/LB-WL-0xD3 according to the desired frequency band and power level associated with STM32WL5/E MCUs.

STMicroelectronics develops integrated passive device (IPD) companion chips for optimized matching, filtering, and balun. The IPD is a very compact solution covering each MCU package and each of the main use cases such as 22 dBm at 915 MHz, 15 dBm at 868 MHz, and 17 dBm at 490 MHz.

#### IPDs for STM32WL5/E and reference designs

9 integrated passive devices (IPD) companion chips are available to match each STM32WL5 configuration. The IPD integrates Tx matching networks, Rx matching networks, Balun, harmonics filter, and ESD shunt inductor. IPD is a very compact solution with a size of 1.83\*2.13 mm² (see Figure 1).

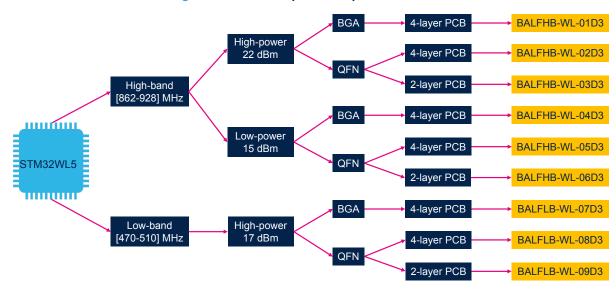

Figure 2 shows RF IPD companion chips for STM32WL5/E. For more information on BALFHB/LB-WL-0xD3, refer to the website https://www.st.com.

Figure 1. Integrated filter matched balun BALFHB/LB-WL-0xD3

Figure 2. RF IPD companion chips for STM32WL5

The STM32WL series provides a portfolio of system-on-chip solutions integrating both a low-power microcontroller and a long-range, energy-efficient sub-GHz radio on the same chip.

For more information on the STM32WL series, refer to the website https://www.st.com.

A portfolio of companion integrated passive devices (IPD) integrates in a tiny footprint the RF fine-tuned BOM, such as harmonic filters, impedance matching, and balun (WL5/E only), available for each STM32WL SoC. STM32WL55 and STM32WLE5.

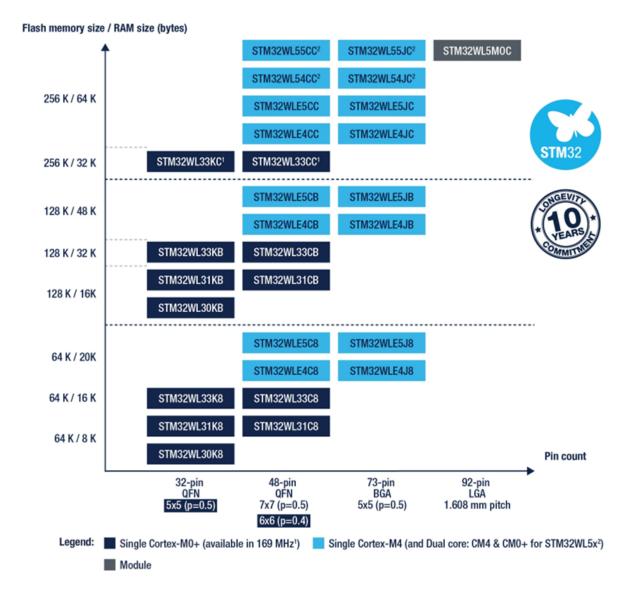

Figure 3 lists the STM32WL series available. This application note refers to STM32WL5x/Ex (light blue reference).

AN6322 - Rev 2 page 2/14

Figure 3. STM32WL series portfolio

Firstly, it is important to define the best package and STM32WL5x/Ex part number suited for the user application. For more information on the STM32WL5x/Ex series, refer to the website https://www.st.com.

Once the package and MCU part number are selected, this allows the user to select line 1 or 2 in the first column of Table 1.

For 73-pin BGA package, only the 4-layer version is available.

For 48-pin QFN, it is possible to choose between a 2-layer or 4-layer PCB. See for more details paragraph 2-layer or 4-layer PCB recommendations.

Finally, the user must select the desired frequency and power level to choose the recommended IPD reference.

AN6322 - Rev 2 page 3/14

Table 1, IPDs for STM32WL5/E MCUs and web reference

| STM32WL5<br>Part number                                     | MCU<br>Package | PCB<br># of layers | Power /<br>frequency | IPD            | Web<br>reference | Board<br>reference |

|-------------------------------------------------------------|----------------|--------------------|----------------------|----------------|------------------|--------------------|

| STM32WL54JC,<br>STM32WL55JC,                                |                |                    | 22 dBm /<br>915 MHz  | BALFHB-WL-01D3 | STDES-WL5I4IHH   | MB1849-HP          |

| STM32WLE4JC,<br>STM32WLE5JC                                 | BGA73          | 4                  | 15 dBm /<br>868 MHz  | BALFHB-WL-04D3 | STDES-WL5I4ILH   | MB1849-LP          |

| STM32WLE4JB,<br>STM32WLE5JB,<br>STM32WLE4J8,<br>STM32WLE5J8 | BOATS          | 4                  | 17 dBm /<br>490 MHz  | BALFLB-WL-07D3 | STDES-WL5I4IHL   | MB1849-HP          |

|                                                             |                |                    | 22 dBm /<br>915 MHz  | BALFHB-WL-02D3 | STDES-WL5U4IHH   | MB1848-HP          |

| STM32WL54CC,<br>STM32WL55CC,                                |                | 4                  | 15 dBm /<br>868 MHz  | BALFHB-WL-05D3 | STDES-WL5U4ILH   | MB1848-LP          |

| STM32WLE4CC,<br>STM32WLE5CC,                                | OFNIAO         |                    | 17 dBm /<br>490 MHz  | BALFLB-WL-08D3 | STDES-WL5U4IHL   | MB1848-HP          |

| STM32WLE4CB,<br>STM32WLE5CB,                                | QFN48          |                    | 22 dBm /<br>915 MHz  | BALFHB-WL-03D3 | STDES-WL5U2IHH   | MB1874-HP          |

| STM32WLE4C8,<br>STM32WLE5C8                                 |                | 2                  | 15 dBm /<br>868 MHz  | BALFHB-WL-06D3 | STDES-WL5U2ILH   | MB1874-LP          |

|                                                             |                |                    | 17 dBm /<br>490 MHz  | BALFLB-WL-09D3 | STDES-WL5U2IHL   | MB1874-HP          |

Once the IPD reference has been selected for the user application, it is important to obtain reference designs, layout, and associated BOM recommendations to help the user in the design of the user application to get the right RF performance, and to pass certification.

For reference designs covering different packages and performance, cost, and complexity trade-offs, refer to the data brief STM32WL reference designs (web reference DB4597).

Inside the STM32WL reference designs (DB4597), STM32WL5x, and STM32WLEx reference designs and codification are available for a matching, filtering, and balun solution with SMD or integrated passive devices (IPD). Reducing PCB footprint and achieving the right RF performance with STM32WL5/E's IPD.

This application note focuses mainly on design references with a portfolio of 9 RF integrated passive devices (IPDs), BALFHB/LB-WL-0xD3.

When all the parameters of the user application are known as well as the required IPD reference. Table 1 is used to obtain web references associated with IPD. These web references allow the user to obtain layout and associated BOM recommendations.

AN6322 - Rev 2 page 4/14

#### 2 2-layer or 4-layer PCB recommendations for 48-pin QFN package

Integrated passive device (IPD) companion chips are tested and validated for achievable right power level on 4-layer PCB with 0.160 mm gap between the top layer and first ground inner layer (see Table 2, row 3), and on 2-layer PCB with 0.710 mm thickness (see Table 3, row 3) with 48-pin QFN package.

Table 2. Stack-up recommendation for 4-layer PCB with QFN package

| Layer name    | Material           | Thickness (µm) | Dielectric Constant |

|---------------|--------------------|----------------|---------------------|

| Top solder    | Solder resist      | 10             | 3.5                 |

| Top Layer     | Copper             | 35             |                     |

| Prepreg 1     | 1 * 2116 + 1 * 106 | 160            | 3.7                 |

| Layer 1       | Copper             | 17.5           |                     |

| Core          | FR4                | 610            | 5                   |

| Layer 2       | Copper             | 17.5           |                     |

| Prepreg 2     | 1 * 2116 + 1 * 106 | 160            | 3.7                 |

| Bottom Layer  | Copper             | 35             |                     |

| Bottom solder | Solder resist      | 10             | 3.5                 |

Table 3. Stack-up recommendation for 2-layer PCB with QFN package

| Layer name    | Material      | Thickness (µm) | Dielectric Constant |

|---------------|---------------|----------------|---------------------|

| Top solder    | Solder resist | 10             | 3.5                 |

| Top Layer     | Copper        | 35             |                     |

| Core          | FR4           | 710            | 5                   |

| Bottom Layer  | Copper        | 35             |                     |

| Bottom solder | Solder resist | 10             | 3.5                 |

The recommended stack-up can be changed but it is important to respect some rules on the distance between the top layer and first ground inner layer (Table 2, column 3, row 3), or ground bottom layer for a 2-layer PCB (Table 3, column 3, row 3). These rules are described in more detail in the following paragraph.

The distance between the top layer and first ground inner layer of the 4-layer PCB should be close to 0.160 mm. The recommendation is to use IPD companion chips reference for 4-layer PCB (see Table 1). IPD are optimized for achieving the right power level on 4-layer PCB configurations with a separation of minimum 0.110 mm and of maximum 0.210 mm between the top layer and first ground inner layer (see Table 4). The other parameters of the stack up can vary slightly without having a major impact on the overall functioning of the product.

Table 4. Prepreg 1 thickness variation for 4-layer PCB with QFN package

| Stack up 4-layer | Min thickness (µm) | Recommended thickness (µm) | Max thickness (µm) |

|------------------|--------------------|----------------------------|--------------------|

| Prepreg 1        | 110                | 160                        | 210                |

The distance between the top layer and ground bottom layer of the 2-layer PCB should be close to 0.710 mm. The recommendation is to use IPD companion chips reference for 2-layer PCB (see Table 1). IPD are optimized for achieving the right power level on 2-layer PCB configurations with a separation of minimum 0.500 mm and of maximum 0.900 mm between the top layer and ground bottom layer (see Table 5). The other parameters of the stack up can vary slightly without having a major impact on the overall functioning of the product.

AN6322 - Rev 2 page 5/14

#### Table 5. Core thickness variation for 2-layer PCB with QFN package

| Stack up 2-layer | Min thickness (µm) | Recommended thickness (µm) | Max thickness (µm) |

|------------------|--------------------|----------------------------|--------------------|

| Core             | 500                | 710                        | 900                |

Note:

For thinner 2-layer PCB, if the distance between the layer 1 and the layer 2 is close to 0.200 mm, the user should choose IPD dedicated to 4-layer PCB.

AN6322 - Rev 2 page 6/14

#### 3 4-layer PCB recommendations for 73-pin BGA package

Integrated passive device (IPD) companion chips are tested and validated for achievable right power level on 4-layer PCB with 0.108 mm gap between the top layer and first ground inner layer (see Table 6, row 3) with 73-pin BGA package.

Table 6. Stack-up recommendation for 4-layer PCB with BGA package

| Layer name    | Material      | Thickness (µm) | Dielectric Constant |

|---------------|---------------|----------------|---------------------|

| Top solder    | Solder resist | 20             | 3.7                 |

| Top Layer     | Copper        | 35             |                     |

| Prepreg 1     | 1 * 2116      | 108            | 3.8                 |

| Layer 1       | Copper        | 35             |                     |

| Core          | FR4           | 710            | 5                   |

| Layer 2       | Copper        | 35             |                     |

| Prepreg 2     | 1 * 2116      | 108            | 3.8                 |

| Bottom Layer  | Copper        | 35             |                     |

| Bottom solder | Solder resist | 10             | 3.7                 |

The recommended stack-up can be changed but it is important to respect some rules on the distance between the top layer and first ground inner layer (Table 6, column 3, row 3). These rules are described in more detail in the following paragraph.

The distance between the top layer and first ground inner layer of the 4-layer PCB should be close to 0.108 mm. The recommendation is to use IPD companion chips reference for 4-layer PCB (see Table 1).

IPD are optimized for achieving the right power level on 4-layer PCB configurations with a separation of minimum 0.080 mm and of maximum 0.140 mm between the top layer and first ground inner layer (see Table 7).

The other parameters of the stack up can vary slightly without having a major impact on the overall functioning of the product.

Table 7. Prepreg 1 thickness variation for 4-layer PCB with BGA package

| Stack up 4-layer | Min thickness (µm) | Recommended thickness (µm) | Max thickness (µm) |

|------------------|--------------------|----------------------------|--------------------|

| Prepreg 1        | 80                 | 108                        | 140                |

AN6322 - Rev 2 page 7/14

#### 4 Example to select the right IPD and reference design associated

For example, the user application needs:

- 128 Kbytes flash memory and 48 Kbytes RAM and 48-pin QFN package. Using Figure 3, the MCU STM32WLE5CB or STM32WLE4CB can be suitable.

- Using Table 1 to select the right column and row for the package and MCU reference.

- The user application is manufactured on a PCB with a distance between the top layer and the first inner layer around 0.200 mm. The recommendation is to use a 4-layer PCB (Table 1, column 3, row 2)

- The user application operates at a power of 22 dBm at the frequency of 915 MHz (Table 1, column 4, row 4).

- Using Table 1, we can find the IPD that is recommended for the user application is BALFHB-WL-02D3 (Table 1, column 5, row 4).

Now that we have selected the right BALFHB-WL-02D3 IPD for the user application, the web reference is available (Table 1, column 5, row 4). This web reference STDES-WL5U4IHH allows the user to reach the CAD resources for BALFHB-WL-02D3 IPD.

In the CAD resources tab, all information about board manufactured specifications, bill of materials and schematics are available to help the user to design the user application.

AN6322 - Rev 2 page 8/14

#### 5 Conclusion

In summary, to select the right BALFHB/LB-WL-0xD3 IPD for the user application:

- 1. Choose the reference for ST32WL5x/Ex MCUs and the package needed.

- 2. Choose 2-layer or 4-layer for manufactured PCB.

- 3. Choose the desired frequency and power level.

- 4. Choose the right BALFHB/LB-WL-0xD3 based on the information from the points above and using Table 1.

- 5. Obtain the web reference of the selected BALFHB/LB-WL-0xD3 using Table 1 to have all the information about board manufactured specifications, bill of materials and schematic are available to help the user to design the user application.

AN6322 - Rev 2 page 9/14

# **Revision history**

**Table 8. Document revision history**

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 24-Jun-2025 | 1        | Initial release. |

| 25-Jul-2025 | 2        | Updated Table 1. |

AN6322 - Rev 2 page 10/14

# **Contents**

| 1    | IPDs for STM32WL5/E and reference designs                       | 2    |

|------|-----------------------------------------------------------------|------|

| 2    | 2-layer or 4-layer PCB recommendations for 48-pin QFN package   | 5    |

| 3    | 4-layer PCB recommendations for 73-pin BGA package              | 7    |

| 4    | Example to select the right IPD and reference design associated | 8    |

| 5    | Conclusion                                                      | 9    |

| Rev  | vision history                                                  | 10   |

| Lis  | t of tables                                                     | 12   |

| List | t of figures                                                    | . 13 |

# **List of tables**

| Table 1. | IPDs for STM32WL5/E MCUs and web reference                     | . 4 |

|----------|----------------------------------------------------------------|-----|

| Table 2. | Stack-up recommendation for 4-layer PCB with QFN package       | . 5 |

| Table 3. | Stack-up recommendation for 2-layer PCB with QFN package       | . 5 |

| Table 4. | Prepreg 1 thickness variation for 4-layer PCB with QFN package | . 5 |

| Table 5. | Core thickness variation for 2-layer PCB with QFN package      | . 6 |

| Table 6. | Stack-up recommendation for 4-layer PCB with BGA package       | . 7 |

| Table 7. | Prepreg 1 thickness variation for 4-layer PCB with BGA package | . 7 |

| Table 8. | Document revision history                                      | 10  |

AN6322 - Rev 2 page 12/14

# **List of figures**

| Figure 1. | Integrated filter matched balun BALFHB/LB-WL-0xD3 | 2 |

|-----------|---------------------------------------------------|---|

| Figure 2. | RF IPD companion chips for STM32WL5               | 2 |

| Figure 3. | STM32WL series portfolio                          | 3 |

AN6322 - Rev 2 page 13/14

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

AN6322 - Rev 2 page 14/14