# STSPIN32G0x low voltage family layout guidelines

### Introduction

The low voltage STSPIN32G0x family's devices are systems-in-package integrating all the circuitry required for a three-phase brushless motor driving application:

- A triple half-bridge gate driver with a current capability of 600 mA (sink and source) and integrated bootstrap diodes.

- A complete power management circuitry composed of a buck converter and an LDO linear regulator provides both 12 V supply voltage for gate drivers and 3.3 V voltage for the MCU and external components.

- Up to three integrated operational amplifiers are available for signal conditioning, such as, current sensing through shunt resistors.

- A comparator with a programmable threshold is integrated to perform the overcurrent protection.

- The integrated MCU (STM32G031 with 64 kB flash and extended temperature range) allows performing field-oriented control, six-step, and other advanced driving algorithms including the speed and position control loop.

This document provides guidelines for the PCB layout of applications based on these devices.

# 1 Buck regulator and MCU supplies

The step-down buck regulator embedded in the devices is based on a hysteretic control, making it stable in a wide input voltage and load current ranges.

More details about the operation and selection of the external components are available in the dedicated Application Note AN5128.

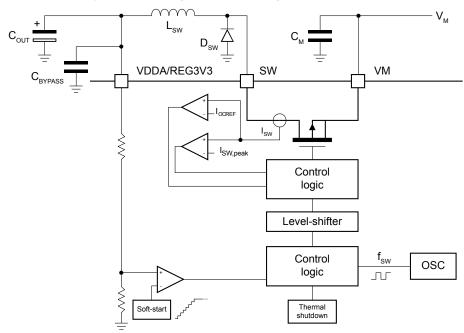

Figure 1. Buck regulator block diagram and schematic

The positioning and layout of the buck regulator's components are critical from both a noise and EMI point of view.

The following is a list of the key points to be considered during the layout of this section:

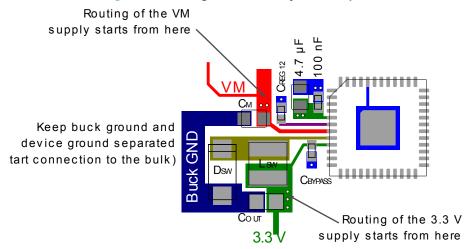

- A ceramic input capacitor (C<sub>M</sub>) should be positioned as near as possible to the VM pin.

- Keep the loop area composed of a recirculation diode, inductor (L<sub>SW</sub>), and output capacitor (C<sub>OUT</sub>) as small as possible.

- One 100 nF ceramic bypass capacitor (C<sub>BYPASS</sub>) must be positioned as near as possible to the REG3V3

pin with the ground side directly connected to the device ground. Keep the bypass capacitor on the same

side of the device.

- The output capacitor (C<sub>OUT</sub>) must be positioned between the inductor (L<sub>SW</sub>) and bypass capacitor (C<sub>BYPASS</sub>).

- The routing of the 3.3 V supply to other components should start from the output capacitor, before the bypass capacitor (C<sub>BYPASS</sub>).

- It is preferred to separate the ground connection of the output capacitor (C<sub>OUT</sub>) from device ground.

- Connection between bypass capacitors and respective pins must be direct, with no via or other traces in between.

AN6254 - Rev 1 page 2/16

Figure 2. Buck regulator block layout example

## 1.1 VDD, VBAT, and VREF+ supplies

All embedded MCU supplies require dedicated ceramic filtering capacitors as below:

- 100 nF + 4.7 μF ceramic capacitors on VDD.

- 100 nF ceramic capacitor on VBAT (STSPIN32G0A1 and STSPIN32G0B1 only).

- 100 nF + 1 µF ceramic capacitors on VREF+ (STSPIN32G0A1 and STSPIN32G0B1 only).

The capacitors must be positioned as near as possible to the respective pin with the ground side directly connected to the device ground. Keep the bypass capacitor on the same side of the device.

AN6254 - Rev 1 page 3/16

# 2 Linear regulator

The regulator requires an output capacitor ( $C_{REG12\_POL}$ ) making the control loop stable and a 100 nF bypass capacitor ( $C_{REG12}$ ) providing pulsed currents during gate driver commutations. The bypass capacitor must be placed as near as possible to the REG12 pin and on the same side of the device.

Routing of the 12 V supply to other components must start from the output capacitor avoiding connection between the bypass capacitor and the REG12 pin.

Both the output and bypass capacitor grounds should be directly connected to the device's ground. This ground is the return path of the low-side gate currents and the charging currents of bootstrap capacitors as described in Section 3.3.

AN6254 - Rev 1 page 4/16

### 3 Gate drivers

## 3.1 High-side gate drivers

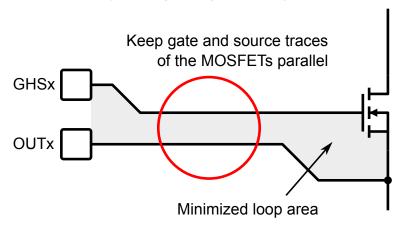

Connection between high-side gate drivers and gate must be as direct as possible, avoiding, if possible, via holes. The return path of the gate currents is the respective OUTx connection, and it should be parallel to the high-side gate trace. Minimizing this loop reduces EMI radiated emission.

Figure 3. High-side gate driver layout

## 3.2 Bootstrap capacitors

Bootstrap capacitors should be positioned as near as possible to the device between the BOOTx and OUTx pins. If possible, keep the bootstrap capacitors on the same side of the device.

If a decoupling resistance between the OUTx pin and high-side MOSFET's source is present, it must be positioned after the bootstrap capacitor.

## 3.3 Low-side gate drivers

Connection between low-side gate drivers and gate must be as direct as possible, avoiding, if possible, via holes. The return path of the gate currents is the device ground, in particular the 12 V regulator ground. Minimizing this loop reduces EMI radiated emission.

In this case, the best approach is having a dedicated layer for the ground layout.

AN6254 - Rev 1 page 5/16

## 3.4 Below-ground and overshoot protection diodes (optional)

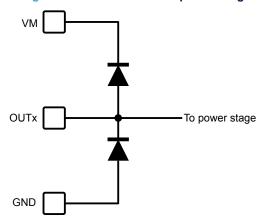

If, for any reason, the power stage output shows below-ground or overshoot ringings violating the absolute rating of the device, some protection diodes on the OUTx pin could be required.

In this case, the diodes should be positioned as near as possible to the pin.

If a decoupling resistance between the OUTx pin and the high-side MOSFET's source is present, it must be positioned after the diodes.

Connect the below-ground protection diodes between the OUTx pin (cathode) and the device's ground (anode) in the most direct way possible. The same for the overshoot protection diodes between the OUTx pin (anode) and VM supply of the device (cathode).

Figure 4. Protection diodes positioning

AN6254 - Rev 1 page 6/16

## 4 Power stage

The power stage is a switching circuitry composed by three half-bridges having a high-side and a low-side MOSFET. The high powers managed by the inverter make it particularly sensitive to parasitics introduced by the layout: fast voltage transitions are easily coupled through parasitic capacitance and commutated currents could cause ringing when flowing into parasitic inductance.

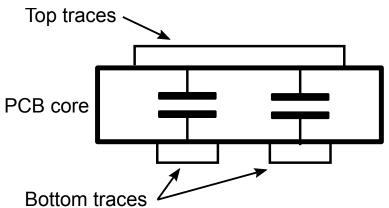

Considering the cross section of the board, the capacitive coupling occurs when the switching node's trace overlaps with other traces routed on a different layer. For this reason, it is important to avoid positioning of signals and analog/digital supplies directly below the switching circuitry. The only traces that can overlap with the switching node are the inverter supply bus and the power ground. If more than 2 layers are available, it is possible to route other signals below the switching circuitry putting a power ground shield in the intermediate layer.

Figure 5. Capacitive coupling between traces

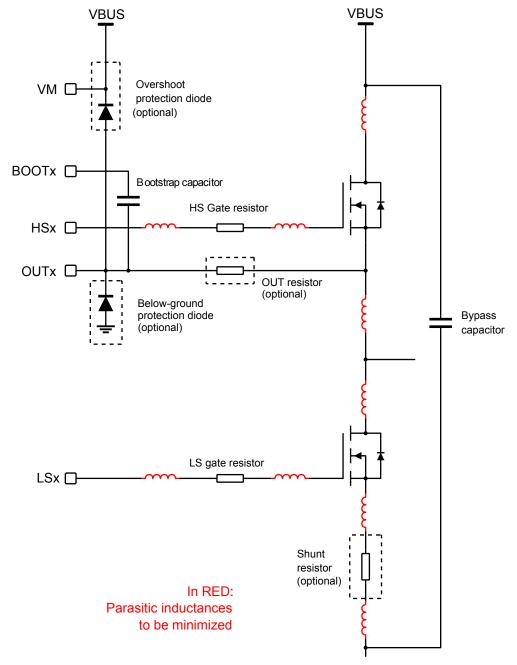

Figure 5 shows the half-bridge schematic with the primary parasitics introduced by connections between the MOSFETs. All these effects should be minimized by making the respective connection as short and wide as possible. Use of vias on these critical paths is not recommended but if not possible to avoid, place multiple vias.

AN6254 - Rev 1 page 7/16

Figure 6. Half-bridge schematic including primary parasitics

AN6254 - Rev 1 page 8/16

### 4.1 Current loops

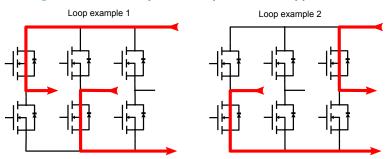

The supply input, the power stage, and the motor phases are part of some high-current loops. In fact, according to the control algorithm, the power stage sources current from the power supply input, distributes it into the motor phases, and closes the loop on the power supply negative lead.

Figure 7. Current loops in three-phase motor applications

These loops are subject to high switching currents, so it is important to keep their area as small as possible, preventing ringing and radiated EMI.

Guidelines for the layout of these loops are:

- Minimize distances between loop components (high-side and low-side switches, shunt resistors, bulk and bypass capacitors). In this way both loop area and parasitics are minimized.

- Keep the trace size wide (lower parasitics).

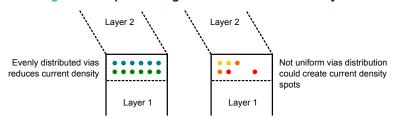

- Connection between layers must be performed using multiple vias distributed over the entire width of the trace.

- Take advantage of different layers allowing the return current to flow back to the negative supply lead parallel to the one coming from the positive lead.

Figure 8. Via positioning for connection between layers

AN6254 - Rev 1 page 9/16

## 5 Bulk and bypass capacitors

In most of the applications a bulk capacitor mitigates the effects of switched currents on the supply inputs providing a fast current source available during load transitions. In fact, the parasitic inductance of the connection cables could limit the supply current during transients.

For this purpose, low ESR parts are recommended. Multiple capacitors in parallel help to achieve high capacitance values reducing the total ESR.

The bulk should be positioned between the supply input and the power stage: the supply line of all the half-bridges must pass through the bulk capacitor to make it effective.

A bypass capacitor of few hundreds of nF should be placed next to each half-bridge filtering high-frequency currents from MOSFETs' commutation.

When ceramic capacitors are selected, particular attention must be paid to the voltage derating factor. The actual capacitance value decreases when the components are biased with a DC voltage, with a derating factor that could reach 50%. For this reason, it is recommended a voltage rating two times the supply voltage that must be filtered.

AN6254 - Rev 1 page 10/16

# 6 Ground layout

Ground separation is a key point, in particular for high current applications.

Three main grounds should be considered:

- 1. Device ground (pin 44 and exposed pad): It is the ground reference for the MCU, operational amplifiers, comparators, 12 V regulator, and low-side gate drivers.

- 2. Buck ground: It is the ground of the buck's output capacitor.

- 3. Power ground: It is the power stage ground where the inverter current flows.

The connection point of the three grounds is the input bulk capacitor.

The exposed pad of the device should be connected to the ground plane using multiple via holes. This has the main purpose of improving the heat dissipation of the device.

AN6254 - Rev 1 page 11/16

# **Revision history**

Table 1. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 10-Feb-2025 | 1       | Initial release. |

AN6254 - Rev 1 page 12/16

# **Contents**

| 1   | Buc    | k regulator and MCU supplies                            | 2  |

|-----|--------|---------------------------------------------------------|----|

|     |        | VDD, VBAT, and VREF+ supplies                           |    |

| 2   | Line   | ear regulator                                           | 4  |

| 3   | Gate   | e drivers                                               | 5  |

|     | 3.1    | High-side gate drivers                                  | 5  |

|     | 3.2    | Bootstrap capacitors                                    |    |

|     | 3.3    | Low-side gate drivers                                   | 5  |

|     | 3.4    | Below-ground and overshoot protection diodes (optional) | 6  |

| 4   | Pow    | ver stage                                               | 7  |

|     | 4.1    | Current loops                                           | 9  |

| 5   | Bull   | k and bypass capacitors                                 | 10 |

| 6   | Gro    | und layout                                              | 11 |

| Rev | /ision | history                                                 | 12 |

# **List of tables**

| Table 1. | Document revision history | <i>.</i> | <br> | <br>′ | 12 |

|----------|---------------------------|----------|------|------|------|------|------|------|------|------|-------|----|

|          |                           | ,        | <br>  |    |

AN6254 - Rev 1 page 14/16

# **List of figures**

| Figure 1. | Buck regulator block diagram and schematic         | 2 |

|-----------|----------------------------------------------------|---|

| Figure 2. | Buck regulator block layout example                | 3 |

| Figure 3. | High-side gate driver layout                       | 5 |

| Figure 4. | Protection diodes positioning                      | 6 |

| Figure 5. | Capacitive coupling between traces                 | 7 |

| Figure 6. | Half-bridge schematic including primary parasitics | 8 |

| Figure 7. | Current loops in three-phase motor applications    | 9 |

| Figure 8. | Via positioning for connection between layers      | 9 |

AN6254 - Rev 1 page 15/16

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

AN6254 - Rev 1 page 16/16