# Introduction to digital camera interface pixel pipeline for STM32 MCUs

### Introduction

As the demand for capturing and processing high-quality images increases, the imaging domain continually evolves, giving rise to advanced technologies across a wide range of applications.

Nowadays, fields such as automotive, security, and home automation introduce new requirements like computer vision and image processing. Consequently, there is a growing need for robust image acquisition capabilities at the edge, which is ensured by DCMIPP on the STM32 microcontrollers.

The STM32 MCUs offer CPU, MCU subsystem, DSP, and FPU. They also provide an extensive set of peripheral and interface combinations, such as XSPI, UART, I2C, SDIO, USB, Ethernet, or I2S. Additionally, STM32 MCUs boast a rich graphical portfolio, including LTDC, DSI, GPU2D, GFXMMU, and DMA2D. Furthermore, they are supported by an industry-leading development environment that ensures sophisticated applications and connectivity solutions (IoT).

This application note provides the STM32 users with essential information about the DCMIPP peripheral along with configuration and examples on how to use it.

Table 1. Applicable products

| Туре               | Product lines                   |  |  |  |  |  |

|--------------------|---------------------------------|--|--|--|--|--|

| Microcontroller    | STM32H7R3/7S3 and STM32H7R7/7S7 |  |  |  |  |  |

| Wilci Ocortu oliei | STM32N6x5 and STM32N6x7         |  |  |  |  |  |

# 1 General information

The STM32 devices are 32-bit microcontrollers based on the Arm<sup>®</sup> Cortex<sup>®</sup> processor.

Note: Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

## **Reference documents**

| [1] | STM32H7Rx/7Sx Arm®-based 32-bit MCUs, reference manual (RM0477)                                            |

|-----|------------------------------------------------------------------------------------------------------------|

| [2] | STM23H7Sxxx datasheet (DS14359)                                                                            |

| [3] | STM23H7Rxxx datasheet (DS14360)                                                                            |

| [4] | STM32N647xx/657xx Arm®-based 32-bit MCUs, reference manual (RM0486)                                        |

| [5] | STM32N6x5xx/STM32N6x7xx datasheet (DS14791)                                                                |

| [6] | Getting started with Octo-SPI, Hexadeca-SPI, and XSPI interfaces on STM32 MCUs, application note (AN5050). |

| [7] | Discovery kit with STM32H7S7L8 MCU, user manual (UM3289)                                                   |

| [8] | Introduction to LCD-TFT display controller (LTDC) on STM32 MCUs, application note (AN4861)                 |

| [9] | Discovery kit with STM32N657X0 MCU, user manual (UM3300)                                                   |

AN6211 - Rev 1 page 2/55

# Digital camera interface pixel pipeline description

## 2.1 Introduction

This section provides a general overview of the DCMIPP peripheral availability across the STM32H7R7/7S7 and STM32N6x5/6x7 products and gives an easy-to-understand explanation on the DCMIPP integration in the STM32 MCUs architecture.

The DCMIPP provides communication interfaces with high-resolution camera sensor and a pixel processing pipeline to process the acquired pixels into a usable form by the application. Two acquisition interfaces are available: a parallel interface with pins for pixel clock and HSYNC and VSYNC synchronization signals as well as a CSI-2 compliant serial interface to capture pixels from camera sensors. The pixel pipeline applies processing such as decimation, cropping, downsizing, color conversion, gamma correction directly on the received pixels.

It offers higher performance compared to former MCUs by moving from AHB slave (DCMI) to AXI master, increasing data transfer rates from 48 Mbytes to 2800 Mbytes. It supports modern CSI-2 interfaces, accommodating high-resolution sensors.

Additionally, the DCMIPP features a dedicated applicative pipe that spares postprocessing and bandwidth by adapting resolution and pixel format to the application needs. Typically, it downsizes on-the-fly to 1080p-YUV420 for video encoding and to QVGA-RGB for NPU analysis.

The DCMIPP application offers high-speed uncompressed image capture for superior image quality and supports compressed image capture in JPEG format for efficient storage space utilization.

The DCMIPP offers flexible operating modes to support most camera sensors.

It supports both color and monochrome cameras, using various data formats. It is compatible with multiple types of external sensors, including:

- Raw Bayer sensors without internal ISP, which output unprocessed raw Bayer pixels

- Sensors with an internal ISP, which usually output RGB or YUV pixels

- Sensors supporting video compression, which output a bit-stream, such as JPEG or H.264

- · Sensors with interlaced video, which output their odd and even fields sequentially

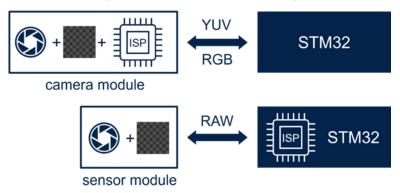

### 2.2 Camera module

The camera module integrates the following components:

- · Lens: Focuses light onto the sensor

- Bayer matrix and filter: Used to capture color information by filtering the incoming light into red, green, and blue components

- Optionally, an image signal processor (ISP): Processes images, converting the raw data from the sensor into a usable format

- Data interface such as CSI-2 interface or parallel interface

AN6211 - Rev 1 page 3/55

These elements work together to capture and process images. Digital cameras typically generate YUV, RGB, and raw Bayer output formats. The sensor modules, in particular, generate Raw bayer output format with bit depths that can vary, including 8, 10, 12, and 14 bits. This raw Bayer format preserves the unprocessed data from the sensor, allowing for greater flexibility and precision in postprocessing and image enhancement.

Scene Bayer filter

Sensor Embedded Image processor image output

Figure 1. Camera module components

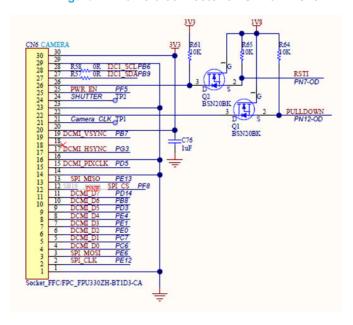

### 2.3 Hardware interfaces

The camera module can be interfaced with an MCU using two types of interfaces: parallel and CSI-2.

## 2.3.1 Parallel interface

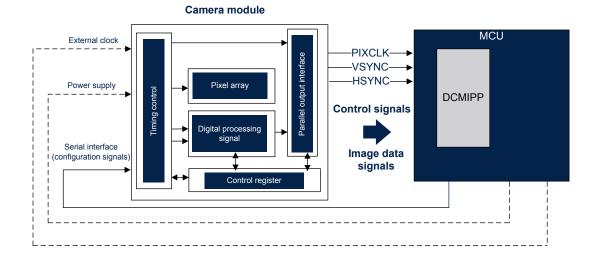

A camera module requires four main types of signals to transmit image data properly: control signals, image data signals, power supply signals, and camera configuration signals.

Figure 2 illustrates a typical interconnection with an MCU.

Figure 2. Parallel interfacing a camera module with an STM32 MCU

74390V1

AN6211 - Rev 1 page 4/55

The interconnection has the following characteristics:

Control signals are used for clock generation and data transfer synchronization

The camera clock must be provided according to the camera specification. The camera also provides two data synchronization signals: HSYNC (for horizontal/line synchronization) and VSYNC (for vertical/frame synchronization).

### Image data signals

Each of them transmits a bit of the image data. Their width represents the number of bits to be transferred at each pixel clock. This number depends on both the parallel interface of the camera module and the embedded system interface.

### Power supply signals

As any embedded electronic system, the camera module needs to have a power supply. The operating voltage of the camera module is specified in Operating condition section inside the device datasheet reference.

- Configuration signals are used for the following:

- Configuring image resolution, format, frame rate, contrast, and brightness, over a dedicated I2C interface, even for the parallel interface (to the sensor).

- The remaining configuration signal used to select the type of interface could be a combination of a sensor pin configuration and/or a firmware initialization sequence sent to the sensor over I2C.

Note: Most camera modules are parametrized through an I<sup>2</sup>C communication bus.

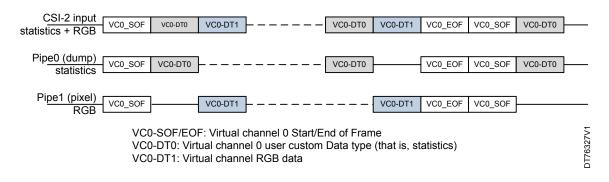

#### 2.3.2 CSI-2 interface

CSI-2 host Camera sensor ISR-DL1P Byte DL1N Clock DCMIPP decode DLOP (LLP) **DL0N** D-PHY D-PHY receiver CSI-2 TX transceiver -PHY\_TX) (D-PHY\_RX) CLKP CLKN JT74391V1 D-PHY interface

Figure 3. Serial interfacing a camera module with an STM32 MCU

The camera serial interface 2 (CSI-2) is part of a group of communication protocols defined by the MIPI® Alliance.

The MIPI® CSI-2 Host controller is a digital core that implements all protocol functions defined in the MIPI® CSI-2 v1.2 specification.

It provides an interface between the system and the MIPI<sup>®</sup> D-PHY, enabling communication with CSI-2 compliant cameras. The CSI-2 host connects external serial cameras to the CSI-2 Host controller, using unidirectional slave data lanes and clock lanes to handle data transmission from CSI-2 protocol-based camera devices to subsystems for data processing handled by the DCMIPP.

The STM32N6 interfaces with serial camera modules by incorporating the MIPI® CSI-2 Host controller. This controller, equipped with a D-PHY receiver physical layer, efficiently and cost-effectively extracts and decodes data packets, processing them frame by frame from the CSI-2 device to the host.

The CSI-2 host connects external serial cameras to the CSI-2 Host controller. It is based on unidirectional slave data lanes and clock lanes to handle data transmission from the CSI-2 protocol-based camera devices to subsystems for data processing handled by the DCMIPP.

# 2.4 DCMIPP availability and features across STM32 MCUs

Table 2 summarizes the STM32 products embedding the DCMIPP. The table also highlights the availability of other hardware resources that facilitates DCMIPP operation. These hardware resources can also be used with the DCMIPP in the same application.

AN6211 - Rev 1 page 5/55

| STM32                          | Max<br>DCMIPP<br>pixel clock<br>input freq.<br>(MHz) | Max<br>Kernel<br>clock<br>freq.<br>(MHz) | Max DCMIPP<br>Interconnect<br>clock freq.<br>(MHz) | Pipe0<br>(dump<br>pipe) | Pipe1<br>(Main<br>Pipe) | Pipe2<br>(ancillary<br>pipe) | Serial<br>interface<br>(CSI-2) | Parallel<br>interface |

|--------------------------------|------------------------------------------------------|------------------------------------------|----------------------------------------------------|-------------------------|-------------------------|------------------------------|--------------------------------|-----------------------|

| STM32H7R3/7S3<br>STM32H7R7/7S7 | 120                                                  | 250                                      | 400                                                | Yes                     | No                      | No                           | No                             | Yes                   |

| STM32N6x5<br>STM32N6x7         | 120                                                  | 333                                      | 250                                                | Yes                     | Yes                     | Yes                          | Yes                            | Yes                   |

Table 2. DCMIPP capabilities

## 2.5 DCMIPP architecture

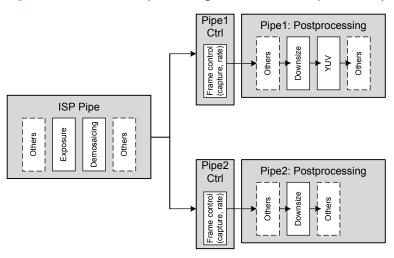

The DCMIPP handles image acquisition and processing through the integrated parallel and abutted CSI-2 interfaces. On the acquisition path, DCMIPP reads input from these interfaces, while on the output path, it writes to memory through the IP-Plug block, acting as an AXI master and using output FIFOs to manage pixel transfers and address memory latency issues. The DCMIPP features include ISP functions in Pipe 1 (shareable with Pipe 2) and differentiated postprocessing pipelines. Pipe 1 and Pipe 2 offer cropping, downsizing, and pixel formatting capabilities.

Pipe 0

ISP

Postprocessing

Pipe 1

Postprocessing

Pipe 2

Figure 4. DCMIPP overview

The DCMIPP offloads the MCU from all image acquisition tasks through up-to-three dedicated camera pipelines, incorporating ISP features for sensor modules such as:

- RGB Bayer pattern processing

- Bad pixel correction

- Decimation

- Black level adjustment

- Exposure control

- Demosaicing

- Color conversion

- Contrast enhancement

Additionally, it offers robust postprocessing functionalities including:

- Cropping

- Decimation

- Downsizing

- · Region of interest (ROI) selection

- Gamma correction

- YUV conversion

- Pixel packing

AN6211 - Rev 1 page 6/55

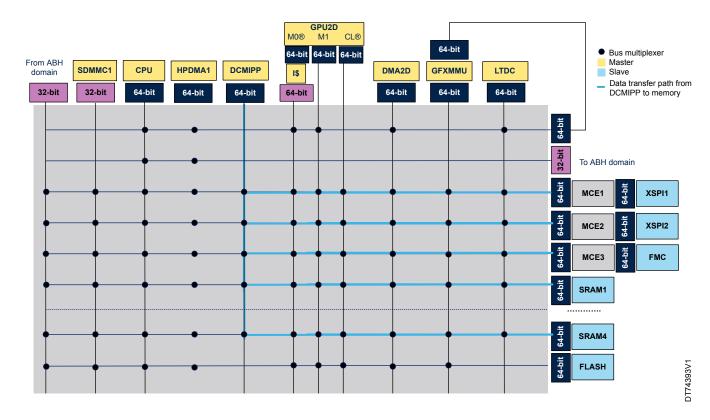

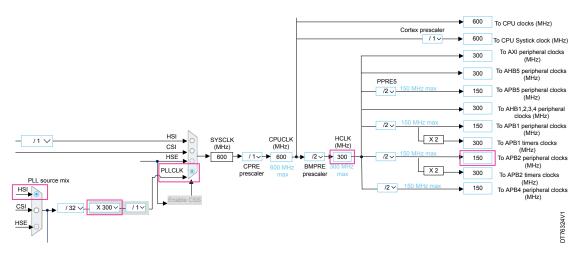

### 2.5.1 STM32H7R7/7S7 system architecture

The STM32H7R7/7S7 line is a bootflash-based MCU powered by a Cortex®-M7 core running up to 600 MHz, with 64 Kbytes of user bootflash, 620 Kbytes of flexible SRAM, and 32 x 32 Kbytes of cache with Flex ECC.

The STM32H7R7/TS7 devices embed two bus matrices: one 64-bit AXI matrix and one 32-bit AHB matrix. This configuration allows efficient and simultaneous operation of high-speed peripherals and removes bus congestion when several masters are simultaneously active (different masters located in separate bus matrices). Each bus matrix ensures and arbitrates concurrent accesses from multiple masters to multiple slaves. The arbitration uses a round-robin algorithm. The maximum bus matrix frequency is half the maximum CPU frequency.

The DCMIPP embeds an AXI bus master to drain all the valid data captured into the pipe from the internal FIFO to the targeted memory.

Figure 5 shows the DCMIPP interconnection and the data path in STM32H7R7/7S7 devices.

Figure 5. DCMIPP interconnection and data path on STM32H7R7/7S7

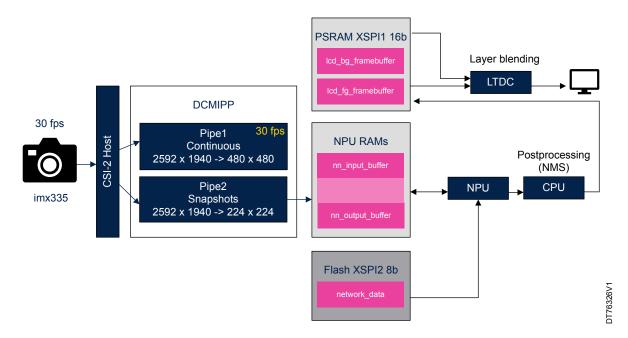

## 2.5.2 STM32N6x5/6x7 system architecture

The STM32N6x5/6x7 is based on the Arm® Cortex®-M55 running at 800 MHz, the first CPU to introduce Arm Helium vector processing technology, bringing DSP processing capability to a standard CPU.

The STM32N6x5/6x7 is the first STM32 MCU to embed the ST Neural-ART accelerator<sup>™</sup>, an in-house developed neural processing unit (NPU) engineered for power-efficient edge AI applications. Clocked at 1 GHz and providing up to 600 GOPS, it enables real-time neural network inference for computer vision and audio applications.

A dedicated computer vision pipeline with a MIPI $^{\otimes}$  CSI-2 interface and image signal processing (ISP) ensures compatibility with a wide range of cameras. The STM32N6x5/6x7 also features an H264 hardware encoder and the NeoChrom  $^{\text{TM}}$  Accelerator for graphics, making it suitable for feature-rich products.

Figure 6 represents the architecture of the system based on the Cortex-M55 processor and the Neural-ART processing unit (NPU). The Cortex-M55 includes 64 KB ITCM, 128 KB DTCM, and 32 KB I-CACHE, and DCACHE (32 KB) memories. The Neural-ART unit is associated with AXI SRAM3, AXI SRAM4, AXI SRAM5, and AXI SRAM6 memories (448 KB each), as well as a cache memory (CACHERAM of 256 KB) via the NPU NIC AXI 64-bit interface.

The memory system includes up to 1024 KB AXI SRAM1, 1024 KB AXI SRAM2, 128 KB VENC RAM, XSPIM1 (16-bit), and XSPIM2 (8-bit) interfaces for accessing external flash and RAM memories.

AN6211 - Rev 1 page 7/55

DT74394V1

The graphical peripherals are composed of:

- Digital camera interface pixel pipeline (DCMIPP)

- LCD display controller (LTDC)

- 2D graphics accelerator (GPU2D)

- Chrom-ART graphics accelerator (DMA2D)

- H.264 video encoder (VENC)

The STNoC AXI 64-bit bus (400 MHz) manages noncacheable NPU traffic and CPU traffic to NPU memories, enabling advanced processing and memory capabilities for applications such as computer vision, signal processing, and machine learning.

AXI-SRAM3 AXI-SRAM! Neural-ART NPL 1000 MHz CORTEX M-55 800 MHz NPU NIC AXI 64-bits NPU Cacheable NPU Traffic to external memories CACHE DCTM Traffic for NPU 256 KB 2 MB NPU RAMs (900 MH) CPU Traffic to NPU RAMs DMIPE LTDC GPU2D VENC Non-cacheable NPU Traffic STNOC AXI 64-bits (400MHz) **VENCRAM** External flash and RAM Overdrive mode 2 MB system RAMs

Figure 6. DCMIPP interconnection and data path on STM32N6x7

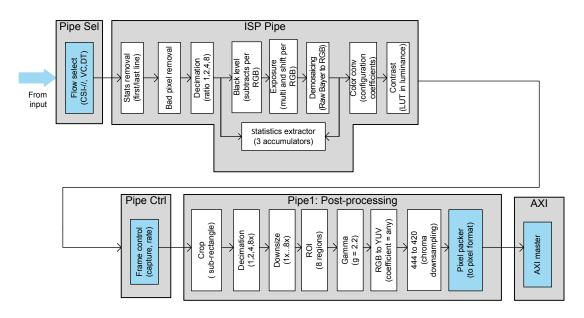

# 2.6 DCMIPP functional description

This section details the DCMIPP and how it handles image data and synchronization signals.

## 2.6.1 Block diagram

As mentioned in Figure 7, the DCMIPP receives pixels from either a parallel or CSI interface. Once the pixel data enters, it passes through a flow selector (FLOWSEL) that directs the data to the appropriate processing pipelines. The architecture features three main pipelines for pixel processing:

- Pipe0-Dump serves as a side dump pipe for legacy functions (similar to DCMI), statistics, and raw Bayer

data for still images. Depending on the product configuration, it includes stages such as data decimation,

reformatting, frame control, and image cropping.

- Pipe1-ISP is more complex, it converts raw Bayer into full-resolution RGB. It also adjusts exposure and

white balance parameters, with stages such as byte conversion, defective pixel correction, demosaicing,

color conversion, and contrast adjustment.

- Pipe1-PostProc and Pipe2-PostProc handle postprocessing for different applications, adapting full-resolution RGB to specific needs such as capture rate, cropping, resizing, and color conversion, with the capability to convert to YUV420 for JPEG or H.264 encoding. Both postprocessing pipes include stages such as frame control, cropping, decimation, downsizing, gamma correction, and pixel packing. The Pipe2-PostProc offers an additional option to sample RGB data before ISP processing. The processed data is then sent to the AXI interface for further use.

AN6211 - Rev 1 page 8/55

Note: STM32H7R3/7S3 includes only **Pipe0-Dump** pipeline in the DCMIPP architecture.

DCMIPP Pipe0 Sel Pipe0 Ctrl Pipe0: Dump AXI Frame control rate) Others Others (CSI-//, CSI-HOST (not in DCMIPP) Pipe1 Ctrl ISP Pipe Pipe1: Postprocessing CSI2 select VC,DT) control re, rate) Input selector Downsize AXI master Others Others Others  $\leq$ AXI bus Parallel interface 64 bits PipeDiff=1 PipeDiff=0 Pipe2 Parallel Input Pipe2: Postprocessing Ctrl select , VC,DT) Frame control (capture, rate) Downsize Others Others SEL Flow s (CSI-//, ' PipeDiff=1

Figure 7. DCMIPP architecture

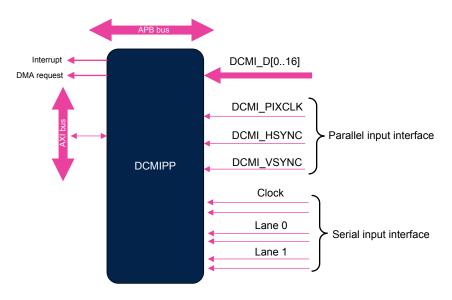

### 2.6.2 Hardware interfaces

The DCMIPP includes:

- Parallel input interface:

- Up to 16 data lines (D15-D0)

- Pixel clock line DCMIPP \_PIXCLK

- DCMIPP \_HSYNC line (horizontal synchronization)

- DCMIPP \_VSYNC line (vertical synchronization)

- CSI-2 camera serial interface:

- Clock lane

- Data lanes (Lane 0, Lane 1)

Figure 8. DCMIPP signals

DT74395V1

### 2.6.3 Parallel interface

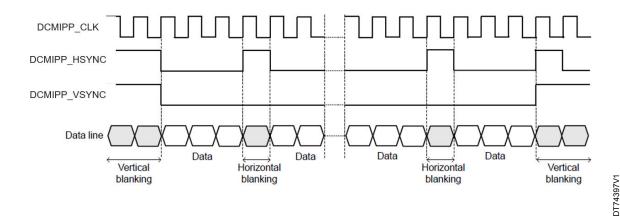

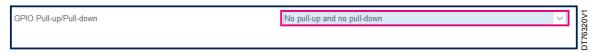

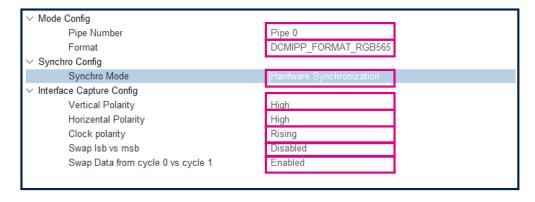

#### 2.6.3.1 Hardware synchronization mode

In hardware synchronization mode, the system uses two synchronization signals, DCMIPP\_HSYNC and DCMIPP\_VSYNC. Depending on the camera module and mode, data can be transmitted during horizontal and vertical synchronization periods. DCMIPP\_HSYNC and DCMIPP\_VSYNC act as blanking signals, as all data received during DCMIPP HSYNC and DCMIPP VSYNC active periods are ignored.

To correctly transfer images in the RAM buffer, data transfer is synchronized with the DCMIPP\_HSYNC and DCMIPP\_VSYNC signals.

When the hardware synchronization mode is selected and capture is enabled (CPTREQ bit set in DCMIPP\_PXFCTCR), data transfer is synchronized with the deassertion of the DCMIPP\_VSYNC signal (next start of frame).

Then, the transfer can be continuous, with successive frames transferred by the IP-Plug to either the same buffers, succesive buffers or circular buffers.

Figure 9 illustrates an example of data transfer when DCMIPP\_VSYNC and DCMIPP\_HSYNC signals are active high, and when the capture edge for DCMIPP\_PIXCLK is the rising edge.

Figure 9. Frame structure in hardware synchronization mode

### 2.6.3.2 Embedded data synchronization mode

The embedded data synchronization mode is available only with the parallel interface capture mode. In this mode, the data flow is synchronized using embedded 32-bit codes with the values 0x00 and 0xFF, which are no longer used in the data.

There are four types of codes, all with 0xFF0000XY format. The embedded synchronization codes are supported only in 8-bit parallel data capture (in the DCMIPP\_PRCR register, the EDM[2:0] bits must be programmed to "000"). For other data widths, the synchronization mode generates unpredictable results.

/ C

Note:

Camera modules generate up to eight synchronization codes when in interleaved mode, while the DCMIPP reacts to one single code. Therefore, in an interleaved flow with an embedded synchronization, every other frame is discarded because it is not detected.

#### Mode 1

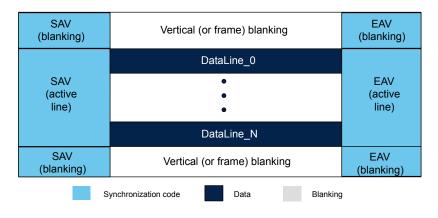

This mode is ITU656 compatible (ITU656 is the digital video protocol of ITU-R BT.656).

The following reference codes indicate a set of four events:

- SAV (active line): line-start

- EAV (active line): line-end

- SAV (blanking): line-start during inter-frame blanking period

- EAV (blanking): line-end during inter-frame blanking period

AN6211 - Rev 1 page 10/55

This mode can be supported by programming the following codes:

- FS ≤ 0xFF

- FE ≤ 0xFF

- LS ≤ SAV (active)

- LE ≤ EAV (active)

Figure 10 illustrates the frame structure using this mode.

Figure 10. Frame structure in embedded synchronization mode 1

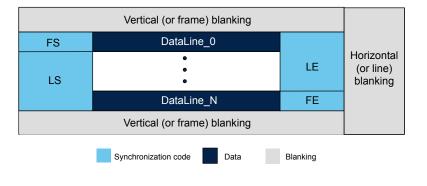

Mode 2

The embedded synchronization codes signal another set of events:

- Frame-start (FS)

- Frame-end (FE)

- Line-start (LS)

- Line-end (LE)

A 0xFF value programmed as a frame-end (FE) means that all the unused codes (the possible values of codes other than FS, LS, LE) are interpreted as valid FE codes.

In this mode, once the camera interface has been enabled, the frame capture starts after the first occurrence of an FE code followed by an FS code.

Figure 11 illustrates the frame structure when using this mode.

Figure 11. Frame structure in embedded synchronization mode 2

399V1

DT74398V1

AN6211 - Rev 1

#### 2.6.4 CSI-2 camera serial interface

#### 2.6.4.1 CSI-2 overview

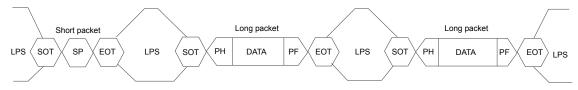

The CSI-2 low-level protocol supports the transport of arbitrary data using both short and long packet formats, with packets transmitted over the physical D-PHY interface. The protocol has the following characteristics:

- Transport of arbitrary data

- 8-bit wordsize

- Special packets for frame start, frame end, line start, and line end information

- · Descriptor for the type, pixel depth, and format of the application-specific payload data

- 16-bit checksum code for error detection

- 6-bit error correction code (ECC)

Figure 12. Low-level protocol overview

LPS: low-power state, SOT: start of transmission, EOT: end oF transmission, PH: packet header, PF: packet footer

As illustrated in the figure before, the sequence of the CSI-2 frames begins with an exit from the low-power state (LPS), followed by the start of transmission (SOT) signal, indicating the start of the packet.

Initially, a short packet (SP) is transmitted, followed by the end of transmission (EOT) signal, and a return to low-power state. The sequence then transitions again with SOT to transmit a long packet, which includes a packet header (PH), payload data (DATA), and a packet footer (PF) for error detection, followed by EOT and a return to low-power state. This process repeats for subsequent long packets, ensuring efficient and robust communication.

## 2.6.4.2 CSI-2 packet description

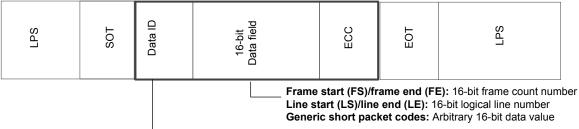

The CSI-2 low-level protocol consists of short and long packets, each with a distinct role.

## **Short packet**

The CSI-2 short-packet format for a D-PHY physical layer is shown in the figure below. It is similar to the long packet header, except that the word count field is replaced by a 16-bit data field. The ECC 8-bit code is present to secure headers having potential bit corruption.

Figure 13. CSI-2 short-packet structure based on D-PHY physical layer

Short packet (32-bit wide)

The data ID contains a data type value from 0x00 to 0x0F to identify a short packet.

JT53050V1

## Long packet

The figure below presents the long packet format. It includes a data ID that consists of a virtual channel number, associated with the data packets, and the corresponding data type.

The word-count field allows the LLP to determine the data-payload width before detecting the packet footer and the EOT. This information is used to detect shorter-than-expected packets, and to trigger a corresponding error The ECC corrects a single erroneous bit in the packet header in the case of data corruption.

The packet data corresponds to the data payload for a given virtual channel and for an identified data type. To complete the long-packet reception block, a packet footer that contains a 16-bit CRC checksum is received and compared to that which is internally calculated by the LLP, to check the data integrity of the received data payload.

Figure 14. CSI-2 long-packet structure for a D-PHY physical layer

|         | 32-bit<br>Packet hea<br>(PH) | ider | Le     | cket da<br>ngth =<br>dth (8 | word o | 16-bit<br>packet<br>footer<br>(PF) |                   |           |           |           |           |                    |

|---------|------------------------------|------|--------|-----------------------------|--------|------------------------------------|-------------------|-----------|-----------|-----------|-----------|--------------------|

| Data ID | Word count<br>(WC)           | ECC  | Data 0 | Data 1                      | Data 2 | Data 3                             |                   | Data WC-4 | Data WC-3 | Data WC-2 | Data WC-1 | 16-bit<br>checksum |

|         |                              |      |        |                             |        |                                    | ( ECC) for the pa |           |           |           | it        |                    |

errors to be detected.

16-bit word count (WC): LLP reads the next WC data words independent of their values. The LLP uses the WC value to determine the end-of-packet. The word count value is transmitted least significant bit first.

Data identifier (ID): contains the virtual channel identifier and the data type code, that denotes the format/content of the application specific payload data (used by the application layer).

### 2.6.5 DCMIPP interrupts

The DCMIPP handles the following interrupts for both the parallel interface and all pipes (Pipe 0, Pipe 1, and Pipe 2):

- Parallel interface interrupts

- IT\_ERR indicates the detection of an error in the embedded synchronization code sequence (only in embedded synchronization mode). This interrupt is indicated by bit 6 in the DCMIPP PRSR register.

- General pipe interrupts:

Specific to Pipe 0

- IT\_LIMIT: This interrupt is triggered when the received volume is larger than the maximum allowed dump volume. It indicates unexpected behavior in Pipe 0, which usually does not occur if there are no issues.

- IT\_LINE: This interrupt is for stripe-based operators and is triggered after every 1/2/4/8/16/32/64/128 dumped lines and the last line. It is measured and extracted at the end of the pipe, close to the output to memory.

- IT\_FRAME: This is a secondary interrupt, serving as a backup for fast software. It is triggered after

the last data dump of this pipe and is inactive if no capture has occurred. It is typically used to quickly

reconfigure non-shadow registers (during only vertical blanking) and to trigger the usage of the

previously captured frame.

- IT\_OVR: This interrupt is triggered when there is a data overflow, meaning the memory was too slow compared to the received pixels. This indicates unexpected behavior in Pipe0, which usually does not occur if there are no issues. The recommendation is to skip the impacted frame.

- IT\_VSYNC: This is the main interrupt, where most software can sit. It is triggered at VSync (mid blanking) and is permanent, even if no dump is active. It is typically used to slowly reconfigure the pipes (at least shadow registers) for the next frame and to trigger the usage of the previously captured frame.

Each pipe has a dedicated interrupt local register that controls the fourth interrupt event (OVR, VSYNC, FRAME, LINE), as indicated in the DCMIPP\_P0SR, DCMIPP\_P1SR and DCMIPP\_P2SR registers for Pipe0, Pipe1, and Pipe2.

## 2.6.6 DCMIPP events

The DCMIPP contains four events to alert the software to react to certain application situations. These events are linked to the pipeline. The table below mentions these events:

Table 3. DCMIPP events

| Pipe   | Event |

|--------|-------|

|        | HSYNC |

| Pipe0  | VSYNC |

| ripeu  | Frame |

|        | Line  |

|        | HSYNC |

| Pipe1  | VSYNC |

| ripe i | Frame |

|        | Line  |

|        | HSYNC |

| Pipe2  | VSYNC |

| i ipez | Frame |

|        | Line  |

AN6211 - Rev 1 page 14/55

### 2.6.7 Capture modes

The DCMIPP captures only the frames required by the application optimizing memory access, AXI bus occupation and power consumption. The applicative software may request to get continuous frames from the camera sensor, or only frame in snapshot mode. These two different modes are selected thanks to the bit CPTMODE inside the DCMIPP PXFSCR register.

### 2.6.7.1 Snapshot mode

In snapshot mode, the software triggers the bit CPTREQ to launch the acquisition from the next start of frame for a single frame only. The bit CPACT remains high only for one frame. It is deasserted at the end of the active frame. At the same time, the bit CPTREQ is cleared by hardware to be ready for future requests, other snapshot acquisitions, or even continuous acquisition after modifying CPTMODE bit in such case.

VSYNC (StartOfFrame) VSYNC (capture complete) VSYNC VSYNC

Static CPTMODE = 1 (Snapshot mode)

CPTREQ = 1

CAPTURE to AXI

Figure 15. Snapshot capture mode

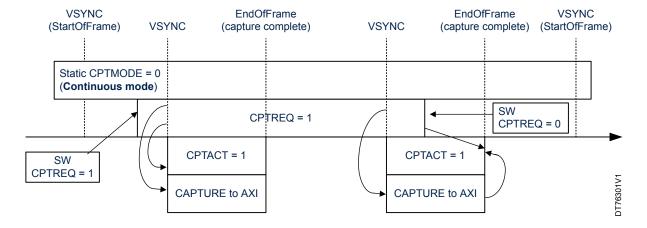

#### 2.6.7.2 Continuous mode

In continuous mode, the DCMIPP processes the frames continuously. The software needs to arm the bit CPTREQ = 1, and the next VSYNC triggers the data acquisition until the deassertion of this bit. The bit CPTACT remains high, indicating this continuous mode operation.

Figure 16. Continuous capture mode

## 2.7 DCMIPP pixel format support

This section describes the pixel formats used in the parallel interface, pixel pipes, and dump pipe. The DCMIPP supports the following data formats:

- Monochrome (8, 10, 12, 14 bit)

- RGB444, RGB565, RGB666, RGB888

AN6211 - Rev 1 page 15/55

- Raw Bayer (8, 10, 12, 14 bit)

- YUV422 and YUV444

Note:

The parallel interface does not input specifically RGB444, RGB555 and RGB666. However, a sensor with this output can connect them onto the DCMIPP, by selecting RGB565 and RGB888. The missing bits can then be connected or strapped to the MSB of the sensor output.

Wide input pixel formats can be sampled in single, double, triple, or quadruple cycles. The table below describes the input pixel formats for the parallel interface and the number of cycles of each format.

Table 4. Supported pixel formats on the parallel interface

| I/O pin                        | 1 cycle | 2 cycles | 3 cycles | 4 cycles |

|--------------------------------|---------|----------|----------|----------|

| Byte                           | Х       | -        | -        | -        |

| Raw 8-bit                      | Х       | -        | -        | -        |

| Raw 10-bit                     | Х       | -        | -        | -        |

| Raw 12-bit                     | Х       | -        | -        | -        |

| Raw 14-bit                     | Х       | -        | -        | -        |

| Monochrome 8-bit               | Х       | -        | -        | -        |

| Monochrome 10-bit              | Х       | -        | -        | -        |

| Monochrome 12-bit              | Х       | -        | -        | -        |

| Monochrome 14-bit              | Х       | -        | -        | -        |

| Sensor RGB444 to DCMIPP RGB565 | Х       | -        | -        | -        |

| Sensor RGB555 to DCMIPP RGB565 | Х       | -        | -        | -        |

| RGB565 – 8-bit                 | -       | Х        | -        | -        |

| RGB565 – 16-bit                | Х       | -        | -        | -        |

| RGB444 – 12-bit                | -       | Х        | -        | -        |

| Sensor RGB555 to DCMIPP-RGB565 | Х       | -        | -        | -        |

| Sensor RGB444 to DCMIPP-RGB565 | Х       | -        | -        | -        |

| RGB888 - 24-bit                | -       | -        | Х        | -        |

| YUV444 - 24-bit                | -       | -        | Х        | -        |

| Sensor RGB666 to RGB888        | -       | -        | Х        | -        |

| YUV422 - 16-bit (YUYV)         | -       | Х        | -        | -        |

## 2.7.1 Monochrome pixel format

The DCMIPP supports monochrome formats with bit depths of 8, 10, 12, and 14 bits per pixel (bpp), which are used to represent different shades of gray. For example, an 8-bit monochrome image can display 256 shades of gray.

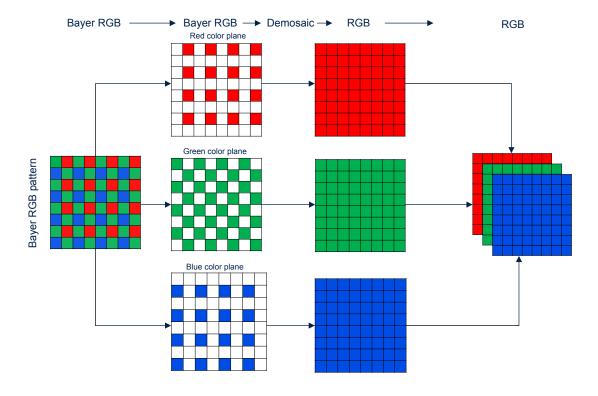

## 2.7.2 Raw Bayer pixel formats

The DCMIPP supports raw Bayer formats with bit depths of 8, 10, 12, and 14 bits per pixel (bpp). The raw Bayer format captures raw image data directly from the camera sensor without any color processing. The sensor pixels are arranged in a Bayer pattern, consisting of alternating rows of red, green, and blue filters.

Each pixel in the raw Bayer format represents only one color component (red, green, or blue), and the full-color image is reconstructed through a process called demosaicing.

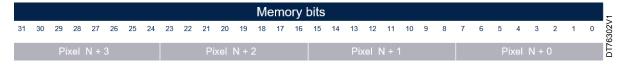

The memory bits have the structure illustrated in Figure 17.

AN6211 - Rev 1 page 16/55

Memory bits

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Pixel N+1

Pixel N+2

Bn + 2

Rn + 3

Figure 17. DCMIPP data register filled with monochrome/raw Bayer data

#### 2.7.3 RGB pixel formats

RGB refers to red, green, and blue, which represent the three hues of light. Any color is obtained by mixing these three colors.

The different RGB formats (RGB444, RGB565, RGB666, RGB888) indicate the number of bits allocated to each color channel.

As an example, RGB888 is used to indicate that each pixel consists of 24 bits, divided as follows:

- 8 bits for encoding the red value (the most significant 5 bits)

- 8 bits for encoding the green value

- 8 bits for encoding the blue value (the less significant 5 bits)

Each component has the same spatial resolution. Each sample has a red (R), a green (G) and a blue (B) component. Figure 18 illustrate the memory bits containing RGB data, when an 8-bit data width is selected.

Figure 18. DCMIPP data register filled with RGB data

## 2.7.4 YUV pixel formats

YUV is a family of color spaces that separates the luminance or luma (brightness) from the chrominance or chroma (color differences).

YUV consists of three components:

- Y refers to the luminance or luma (black and white)

- U refers to the blue chroma

- V refers to the red chroma

For YUV422-1 buffer (YUYV), each pixel is stored with 8 bits for Y (luminance), and the chrominance components U and V are shared between two pixels. Specifically, the memory layout alternates between Y, U, Y, V for consecutive pixels (that is, pixel N has Y0, U0, Y1, V0, and pixel N+1 has Y2, U1, Y3, V1).

For example, in the YUV422-2 buffers configuration, the Y components are stored in one buffer and the U and V components are stored in another buffer. For instance, the buffer contains Y values for pixel N, N+1, N+2, and N+3, while buffer contains the U and V values for pixel N and N+1.

AN6211 - Rev 1 page 17/55

Figure 19 illustrates the memory bits containing YUV422-1 data when an 8-bit data width is selected.

Figure 19. DCMI data register filled with YUV data

|    |    |     |      |       |      |       |     |    |    |    |     |     | Me | emo | ory | bits |    |     |       |       |    |     |       |      |     |    |     |       |    |    |    |

|----|----|-----|------|-------|------|-------|-----|----|----|----|-----|-----|----|-----|-----|------|----|-----|-------|-------|----|-----|-------|------|-----|----|-----|-------|----|----|----|

| 31 | 30 | 29  | 28   | 27    | 26   | 25    | 24  | 23 | 22 | 21 | 20  | 19  | 18 | 17  | 16  | 15   | 14 | 13  | 12    | 11    | 10 | 9   | 8     | 7    | 6   | 5  | 4   | 3     | 2  | 1  | 0  |

| Y7 | Y6 | Y5  | Y4   | Y3    | Y2   | Y1    | Y0  | Y7 | Y6 | Y5 | Y4  | Y3  | Y2 | Y1  | Y0  | Y7   | Y6 | Y5  | Y4    | Y3    | Y2 | Y1  | Y0    | Y7   | Y6  | Y5 | Y4  | Y3    | Y2 | Y1 | Υ( |

|    |    | Buf | fer0 | : Pix | el N | 1 + 3 |     |    |    | Pi | xel | N + | 2  |     |     |      |    | Pix | cel 1 | V + 1 |    |     |       |      |     | Pi | xel | N + I | 0  |    |    |

| V7 | V6 | V5  | V4   | V3    | V2   | V1    | V0  | U7 | U6 | U5 | U4  | U3  | U2 | U1  | U0  | V7   | V6 | V5  | V4    | V3    | V2 | V1  | V0    | U7   | U6  | U5 | U4  | U3    | U2 | U1 | U  |

|    |    | Buf | fer1 | : Pix | el N | 1+2   | and | 3  |    |    |     |     |    |     |     |      |    |     |       |       | Pi | xel | N + 1 | 0 an | d 1 |    |     |       |    |    |    |

# 2.8 Supported pixel formats on the CSI-2 interface

This section describes the pixel formats used in CSI-2 interface, pixel pipes, and dump pipe.

Table 5 lists the supported pixel formats in the input interfaces (parallel, CSI), as input to the pixel Pipe1 and Pipe2, and in the three output pipes.

Table 5. Supported pixel formats on the CSI-2 interface

| Pixel format                 | ВРР                    | Parallel input<br>(clk/pix) <sup>(1)</sup> | CSI input        | Pipe0 output<br>(dump) | Pipe1 and<br>Pipe2 input | Pipe1<br>output<br>(main) | Pipe2 output<br>(ancillary) |

|------------------------------|------------------------|--------------------------------------------|------------------|------------------------|--------------------------|---------------------------|-----------------------------|

| Bytes                        |                        |                                            |                  |                        |                          |                           |                             |

| (CSI: long packets and user) | 8                      | -                                          | Y                | Y                      | -                        | -                         | -                           |

| Byte stream                  |                        |                                            |                  |                        |                          |                           |                             |

| (JPEG, compressed video)     | 8                      | Y, 1                                       | -                | Y                      | -                        | -                         | -                           |

| Other data                   | 8 to 16 <sup>(2)</sup> | Y, 1                                       |                  | Y                      | -                        | -                         | -                           |

| Raw6                         | 6                      | (3)                                        | Y <sup>(4)</sup> | Y <sup>(4)</sup>       | -                        | -                         | -                           |

| Raw7                         | 7                      | (3)                                        | <b>Y</b> (4)     | (4)                    | Y                        | -                         | -                           |

| Raw8                         | 8                      | Y, 1                                       | Y                | Y                      | To 8 bpc                 | Υ                         | Y                           |

| Raw10                        | 10                     | Y, 1                                       | Y                | To 16 bpc              | To 8 bpc                 | -                         | -                           |

| Raw12                        | 12                     | Y, 1                                       | Y                | To 16 bpc              | To 8 bpc                 | -                         | -                           |

| Raw14                        | 14                     | Y,1                                        | Y                | To 16 bpc              | Y                        | -                         | -                           |

| Mono8                        | 8                      | Y, 1                                       | -                | Y                      | To 8 bpc                 | Y                         | Y                           |

| Mono10                       | 10                     | Y,1                                        | -                | To 16 bpc              | To 8 bpc                 | -                         | -                           |

| Mono12                       | 12                     | Y, 1                                       | -                | To 16 bpc              | To 8 bpc                 | -                         | -                           |

| Mono14                       | 14                     | Y,1                                        | -                | To 16 bpc              | To 8 bpc                 | -                         | -                           |

| RGB444                       | 12                     | (3)                                        | Y                | (3)                    | To 8 bpc                 | -                         | -                           |

| RGB555                       | 15                     | (3)                                        | Y                | (3)                    | To 8 bpc                 | -                         | -                           |

| RGB565                       | 16                     | Y, 1, 2                                    | Y                | Y                      | To 8 bpc                 | Y                         | Y                           |

| RGB666                       | 18                     | (3)                                        | Y                | (3)                    | To 8 bpc                 | -                         | -                           |

| RGB888 / YUV444              | 24                     | Y, 2, 3                                    | Y                | Y                      | Y                        | Υ                         | Y                           |

| xRGB888 / xYUV444            | 32                     | -                                          | -                | Y                      | -                        | Y                         | Y                           |

| RGBx888 / YUVx444            | 32                     | -                                          | -                | Y                      | -                        | Y                         | Y                           |

| YUV422-1 (YUYV)              | 16                     | Y, 1, 2                                    | Y                | Y                      | Y                        | Y                         | Y                           |

| YUV422-2                     | 16                     | -                                          | Y <sup>(4)</sup> | Y <sup>(4)</sup>       | Υ                        | Y                         | -                           |

AN6211 - Rev 1 page 18/55

| Pixel format             | ВРР | Parallel input<br>(clk/pix) <sup>(1)</sup> | CSI input        | Pipe0 output<br>(dump)  | Pipe1 and<br>Pipe2 input | Pipe1<br>output<br>(main) | Pipe2 output<br>(ancillary) |

|--------------------------|-----|--------------------------------------------|------------------|-------------------------|--------------------------|---------------------------|-----------------------------|

| YUV420-2 (NV21/<br>NV12) | 12  | -                                          | Y <sup>(4)</sup> | <b>Y</b> <sup>(4)</sup> | Y                        | Υ                         | -                           |

| YUV420-3 (YV12)          | 12  | -                                          | Y <sup>(4)</sup> | Y <sup>(4)</sup>        | Y                        | Y                         | -                           |

| YUV422 10 bpc20          | 20  | -                                          | Y <sup>(4)</sup> | Y <sup>(4)</sup>        | -                        | -                         | -                           |

| YUV420 10 bpc            | 15  | -                                          | Y <sup>(4)</sup> | Y <sup>(4)</sup>        | -                        | -                         | -                           |

| Any other CSI-2          | Any | -                                          | <b>Y</b> (4)     | Y <sup>(4)</sup>        | -                        | -                         | -                           |

- Index is used to link the input pixel format to the DCMIPP\_PRCR register. The index has a meaning only for camera connected with the parallel interface.

- 2. Pixel formats on 16 bpp (like RGB565 or YUV422-1) can be received either on an 8-bit interface (using 2 cycles), or on a 16-bit input interface (using one cycle). Pixel formats on 24 bpp (like RGB888) can be received either on an 8-bit interface (using three cycles), or on a 12-bit input interface (using two cycles).

- 3. On the parallel interface input, some sensor pixel formats are supported by the DCMIPP, by selecting a wider pixel format in DCMIPP, by mapping the sensor wires onto the MSB of the DCMIPP interface. On the missing input pins, it is recommended to replicate the sensor MSB pins onto the missing input LSB pins. This helps achieving full dynamic on the extended pixel format.

The workaround can be applied on the following formats (sensor output on left, mapping on DCMIPP format on right):

- Raw6: Raw8 with 1-cycle input, processed as an 8 bpp

- Raw7: Raw8 with 1-cycle input, processed as an 8 bpp

- RGB444: RGB565 with 1-cycle input, processed as a 16 bpp

- RGB555: RGB565 with 1-cycle input, processed as a 16 bpp

- RGB666: RGB888 with 3-cycle input, processed as a 24 bpp

- 4. The same bit mapping is used for the input RGB888 and YUV444, the input xRGB and xYUV, and similarly for the outputs. The difference between RGB and YUV is the color reference, set in the color conversion that occurs after the input or before the output.

## 2.9 AXI IP-Plug

The AXI IP-Plug is designed to manage data transfer from various pipes to memory using the AXI protocol. This module, shared by all pipes ensures efficient handling of data dumps from these pipes to memory.

The AXI IP-Plug is equipped with key features designed to optimize data transfer and memory management. It includes Pipe ID differentiation to identify data sources and manage quality of service (QoS) accordingly. The FIFO buffers are sized to handle up to 2 microseconds of latency. It supports burst lengths of 64 and 128 bytes. The IP-Plug can manage up to 16 outstanding transactions simultaneously, addressing high-bandwidth requirements effectively. A bandwidth limiter is included to prevent memory overload by controlling the bandwidth usage of each pipe. Additionally, the unique AXI-QOS mechanism ensures that all pipes meet their real-time constraints without differentiation.

### 2.9.1 IP-Plug configuration steps

The following steps outline the programming procedure for accessing idle registers.

1. Lock request

The CPU requests to lock the IP-Plug by writing 1 in the P\_START register flag.

2. Status polling

The CPU waits that the IDLE register flag is set to 1 by the IP-Plug.

AN6211 - Rev 1 page 19/55

### 3. Programming

The CPU writes all the required IP-Plug registers. This includes:

- Setting the MEMORYPAGE register for efficient DRAM handling.

- Identifying clients corresponding to each pipe or buffer.

- Configuring OTR (outstanding transactions) for each client.

- Setting FIFO size by configuring DPREGSTART and DPREGEND for each client based on their peak bandwidth requirements.

- Setting TRAFFIC (burst size) for each client.

- Allocating WLRU (bandwidth proportion) for each client.

- Setting SVC (system virtual channel) for each client.

### 4. Unlock

The CPU unlocks the IP-Plug by writing 0 in the P START register flag.

In the STM32N6x5/6x7, the DCMIPP includes three pipes (Pipe0, Pipe1, Pipe2), with Pipe1 supporting full planar capability through three buffers (Y, U, V).

Each client of the IP-Plug is allocated a proportion of the total FIFO size and the total outstanding available transactions based on their bandwidth requirements. The total FIFO size is 5 Kbytes (5120 bytes), which translates to 640 words (since AXI width is 64 bits). The allocation of the FIFO size among the clients is illustrated in the diagram below. The parameters used for allocation are DPREGSTART, which is the starting word of the FIFO for the client (for example, Client1 starts at word 0), and DPREGEND, which is the ending word of the FIFO for the client (that is, Client1 ends at word 95). The total number of words for each client is calculated based on their allocated proportion of the total FIFO size.

The capabilities of the DCMIPP are shared among the clients The total bandwidth proportion, when all pipes are used, is 12 with the following assumptions:

- Client1 for Pipe0: dump of raw Bayer pixels, padded to 16 bpp, BW = 2 / 12

- Client2 for Pipe1-Y: dump of ARGB pixels, on 32 bpp, BW = 4 / 12

- Client3 for Pipe1-UV: dump of UV components, on 8 bpp, BW = 1 / 12

- Client4 for Pipe1-V: dump of V component, on 4 bpp, BW = 1 / 12

- Client5 for Pipe2: dump of ARGB pixels, on 32 bpp, BW = 4 / 12

Figure 20. FIFO allocation among IP-Plug clients for STM32N6x5/6x7

Total FIFO size (5 Kbytes/640 words)

Client5 (Pipe2) - 224

words

Client4 (Pipe1- V) - 32

words

Client3 (Pipe1-UV) 64 words

Client2 (Pipe1-Y/

RGB) - 224 words

Client1 (Pipe0) - 96

words

T76330V1

AN6211 - Rev 1 page 20/55

Note:

If a client is assigned 1 KB of FIFO space, which corresponds to 128 words, and DPREGSTART is 0, then DPREGEND would be 127. This is calculated as follows:

FIFO size in words = 1 KB / 8 bytes per word = 128 words

DPREGEND = DPREGSTART + (FIFO size in words - 1)

AN6211 - Rev 1 page 21/55

DT76305V1

# 3 DCMIPP pipes description

This section describes the functional pipes of DCMIPP. For each element, it details the camera pipeline and the features used for pixel data processing.

## 3.1 Pipe0: Dump pipe

#### 3.1.1 Overview

Pipe0 acts as a dump pipe, extracting data from the camera sensor module and transferring it directly to the targeted memory with basic decimation and 2D cropping operations. It retrieves data via the 16-bit parallel interface or the CSI-2 interface, managed by the INSEL bit in the DCMIPP\_CMCR register. The flow selection determines the virtual channels and data types to be processed, while the frame controller handles the camera acquisition mode.

When valid input data is detected, 2D cropping and decimation can be configured by software. Dump counter and data limit ensure proper handling of data length within a frame. Pipe0 can be reconfigured periodically, with events triggering software reconfiguration routines. Shadow registers can be written during frame processing, with values loaded into physical registers at the start of the frame event.

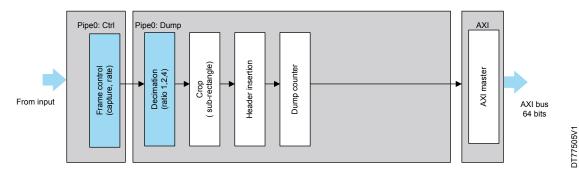

Pipe0: Ctrl Pipe0: Dump AXI Header insertion rate) (sub-rectangle) Dump counter Frame control **Decimation** (ratio 1,2,4) master Crop capture, ₹ From input AXI bus 64 bits

Figure 21. Data flow and processing modules in Pipe0

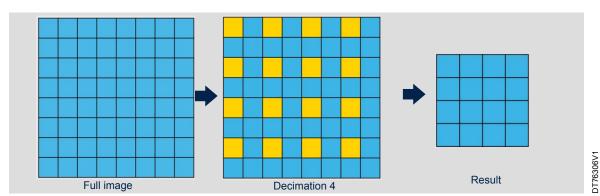

## 3.1.2 Decimation

Decimation is used to reduce image resolution while maintaining the field of view. A typical application involves using a lower resolution image for live view to reduce camera bandwidth and increase the frame rate. This also helps in providing smaller images for neural network processing. It is possible to downsize a frame by a factor 2x, 4x and 8x in both horizontal and vertical directions.

The figure below illustrates an example of an image with a resolution of 4096 x 2048. In 4 x 4 decimation mode, the output resolution is 1024 x 512.

Figure 22. Decimation module

AN6211 - Rev 1 page 22/55

### 3.1.3 Pixel 2D cropping

The crop operation extracts and forwards a rectangle of pixels. The dump pipe (Pipe0) can handle 2D crop processing. Vertical cropping is based on lines, facilitated by the HSYNC event.

However, the horizontal cropping is applied based on 32-bit wide data rather than individual pixels, as this pipe does not directly consider pixels. Instead, it manages the data flow with 32-bit granularity.

#### 3.1.4 Downsize

The downsize module implements a downsize based on box filtering, which allows ratios from 1x to 8x independently, in both X and Y directions.

#### 3.1.5 Header insertion

The header insertion module is designed works with dump pipes and can insert a header before the data of a former CSI packet. This header can either be a frame sync short packet or a header of a long data packet. It helps software interpret the following data payload:

- The frame sync short packet provides information about the frame type (SOF or EOF), frame number, and virtual channel ID.

- The header of the data long packet provides information about the number of bytes in the payload, data type ID, and virtual channel ID.

## 3.1.6 Dump counter

The DCMIPP offers the capability to count the number of 8-bit data dumped within a frame for input data format with unknown length (JPEG for instance). It avoids dumping greater number of data which would compromise memory integrity if the reserved area for the dump is smaller than the number of data under capture.

The limit is set by the software in the DCMIPP\_P0DCLMTR register. When this limit is reached, an interrupt may be generated to notify the software that any data beyond the limit is rejected, resulting in an incomplete frame acquisition. The counter continues to increment after the limit is crossed to indicate the amount of data that has been discarded, and it saturates at 0x03FF\_FFFF.

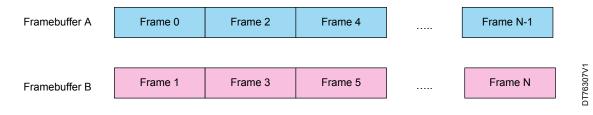

## 3.1.7 Double buffer mode

The dump pipe uses an AXI master interface to dump the data from the internal FIFO to the external memory. In the application, it is possible to handle frame data swapping memory area frame by frame as illustrated in Figure 23. The double buffer mode supports this function.

There are two memory address registers set to initialize the base addresses of these memories areas. Each start of captured frame event swaps the memory base address to handle double buffering mode.

Double buffer mode allosw postprocessing on a buffer (framebuffer) while the other buffer is read for display (display buffer) or used as input in the NPU.

Figure 23. Double buffer example

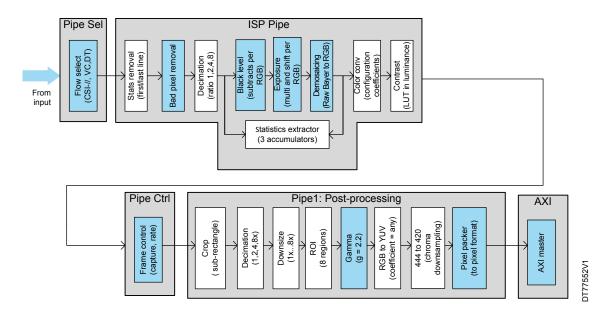

## 3.2 Pipe1: Main pipe, ISP part

Pipe1 is a pixel pipeline that integrates various image signal processing (ISP) and postprocessing functions to relieve the software from specific time and memory-consuming operations. Pipe1 is typically used for primary tasks such as video encoding, software analysis, and neural networks. It allows for input downsizing, color conversion, and dumping to multiple pixel formats, including multi-planar ones.

AN6211 - Rev 1 page 23/55

Pipe1 can adjust luminosity through gamma conversion, perform autoexposure, and calibrate black levels using the embedded image-processing functions. This capability is particularly useful for handling camera sensors without internal ISPs. Additionally, Pipe1 can convert raw Bayer data to RGB (demosaicing). Importantly, Pipe1 shares all its image-processing functions with Pipe2.

Figure 24. Data flow and processing modules in ISP, Pipe1, and Pipe2

DT76308V1

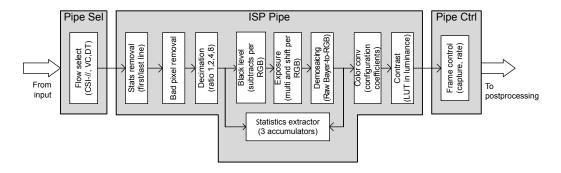

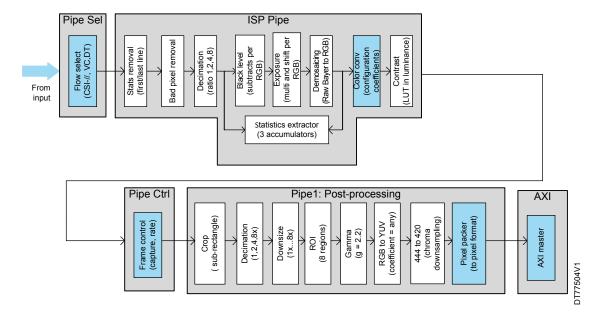

## 3.2.1 Pipe1 (ISP part)

This section details each module in the ISP part, which implements various functions as illustrated in Figure 25. These functions include: statistics removal within the data flow, bad pixel detection to automatically remove noisy pixels, and basic decimation to reduce high-resolution camera sensor data to fit within the image-processing maximum resolution tolerance. Additionally, the ISP performs auto exposure and statistics extraction based on pixel analysis. It employs a demosaicing algorithm to convert raw Bayer input pixels to RGB, and includes color conversion and contrast enhancement functions.

Figure 25. Data flow and processing modules in ISP Pipe

DT76309V1

## 3.2.1.1 Byte to pixel conversion

The module operates on pixel pipes by receiving 32-bit words from the input interfaces (parallel or CSI). It extracts pixels based on the provided pixel format and maps them into the triple-component pixel pipeline, which is 14 bits per component (bpc) at this stage and 8 bpc later downstream.

Note: YUV420 to YUV444 conversion is not supported. Pipe1 and Pipe2 cannot extract and process YUV420 pixels received from the CSI interface.

### 3.2.1.2 Statistics removal

The module is used to remove potential statistic data inserted by a sensor, prior to starting the demosaicing conversion that is multipixel and would be impacted by remaining statistics. It is typically used by sensors with a parallel interface that cannot distinguish between statistics and pixel data. CSI-2 sensors typically split these flows using different virtual channel IDs.

AN6211 - Rev 1 page 24/55

#### Features:

- Suppression of some of the first lines of the frame

- Suppression of the last lines of the frame, after a configured line N

#### 3.2.1.3 Bad pixel removal

This module aims at detecting and correcting artifacts generated by a bad pixel on the sensor array. It is based on a correlation extraction, and not on fixed locations.

### 3.2.1.4 Input decimation

The decimation is redundant with the downsize, that brings a higher quality (the decimation discards the data of the dropped pixels, while the downsize averages all pixels and does not lose information).

The decimation has two main usages:

- 1. Reduces the width of very high-resolution sensors to one accepted by the raw Bayer to RGB conversion. Indeed, the raw Bayer to RGB embeds a line buffer that limits the processed images to a maximum width of 2688 pixels. For instance, to plug a 12 megapixel sensor (4000 x 3000), decimate its width by a factor 2x to 2000 pixels wide, and have it converted to RGB.

- Complements the downsize (limited to ratio of 8 x 8), to have a combined downsizing ratio of 64 x 64. It is

recommended to have the largest ratio implemented in the downsize, and the decimation complement to that.

For instance, for a ratio 30x, it is recommended to have a ratio 4x in decimation, and a ratio 30 / 4 = 7.5 in the

downsize.

#### 3.2.1.5 Statistics extraction

This module extracts frame statistics to provide inputs for software image compensation algorithms. These algorithms then adjust hardware modules such as black level calibration, exposure compensation, white balance, and contrast enhancement based on the feedback.

Statistics are accumulated during a full frame and sampled at the end, allowing the software the entire next frame to read the accumulated data.

The module features three accumulators, enabling the extraction of three pieces of information per frame. It can focus on specific subscenes by extracting statistics from a designated subrectangle and can select specific components, such as R, G, B, or luminance.

Two types of statistics can be extracted: the average and the spectrum, which is split into 12 bins across the range of 0 to 255.

,

Note:

One limitation is that constructing a 12-bin spectrum with three data points per frame requires four frames, which reduces reactivity

# 3.2.1.6 Black level calibration

This module suppresses a potential positive black level offset, which happens when the sensor sends non-null pixels when capturing a black picture.

#### 3.2.1.7 Exposure and white balance

This module aims to compensate for bad exposure, whether too short and dark or too long and light, and corrects color balance to achieve a more neutral white.

The exposure and white balance operations are purely linear, ensuring no color distortion if performed correctly.

The module reduces the pixel dynamic range from 14 bits to 8 bits, lowering the implementation cost of downstream modules, which operate at 8 bits instead of 14.

It also recenters the RGB values towards a neutral white color scene. The module features linear amplification applied to the input component, which is then saturated to 8 bits, minimizing color distortions among R, G, and B.

It selects an 8-bit dynamic range from the 14-bit input: the eight most significant bits (MSB) for well-lit scenes, the eight least significant bits (LSB) for dark scenes, or any intermediate range for medium lighting.

The amplification is configurable via software to adapt to the scene, utilizing statistical extractions to compute the ideal amplification coefficient. Additionally, it differentiates between R, G, and B to recenter the colors to white.

## 3.2.1.8 Demosaicing

The module works on the pixel pipes and implements a mid-quality conversion from raw Bayer 8 bpp to an RGB 24 bpp, with no implicit half-sizing: the output RGB pixel rate is the same as the input component rate.

AN6211 - Rev 1 page 25/55

DT76310V

The conversion targets real-time but medium quality purposes, such as display or low-resolution software analysis. For higher-quality conversions, it is recommended to convert the raw Bayer in software, with higher-quality algorithms but limited to non-real-time, thus still-picture applications. The algorithm takes the surrounding 3 x 3 components in input, applies linear heuristics to determine the most likely missing components, and generates an output RGB888 pixel as illustrated in Figure 26.

To provide the  $3 \times 3$  input matrix to the algorithm, the demosaicing module embeds a double line-buffer,  $2 \times 2688$  components wide. As such, it limits the maximum width of a converted demosaicing buffer to 2688 components per pixels wide. Wider camera sensor resolution can be connected and goes through the first decimation stage in front of the demosaicing operation.

Figure 26. Demosaicing module

Note:

This demosaicing conversion algorithm can create some artifacts such as zipper. These artifacts are reduced by a later downsizing or even suppressed with a  $2 \times 2$  downsizing.

#### 3.2.1.9 Contrast enhancement

This module concludes the image-processing pipeline by enhancing the frame contrast through nonlinear emphasis of pixel luminance. It increases the number of luminance quantification steps in frequently used luminance ranges (typically central grays) while reducing steps in less used ranges (usually very dark and very light pixels). The purpose of this approach is to address parts of the scene that may be too dark or too light.

The contrast module nonlinearly amplifies the luminance of RGB pixels to improve visibility. It extracts pixel luminance based on local R, G, and B values and applies an amplification factor dependent on the luminance, interpolated from a table with nine entries. This process amplifies or reduces per-pixel luminance and proportionally adjusts the R, G, and B values.

#### 3.2.1.10 Color conversion

This module implements color conversion with flexible and fully programmable coefficients. The goal of this module is to perform color correction to compensate for ambient illumination (such as sunlight, incandescent, or fluorescent lighting) and sensor distortions. It also maps colors to a neutral RGB.

It also supports YUV sensors by converting YUV data to standard RGB.

The module features the multiplication of input R, G, B (or YUV) values by a 3 x 3 matrix and the addition of an offset. It is fully configurable via software and can be clamped to a reduced dynamic range if necessary.

AN6211 - Rev 1 page 26/55

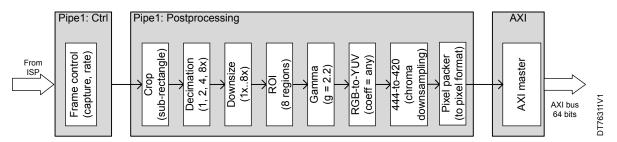

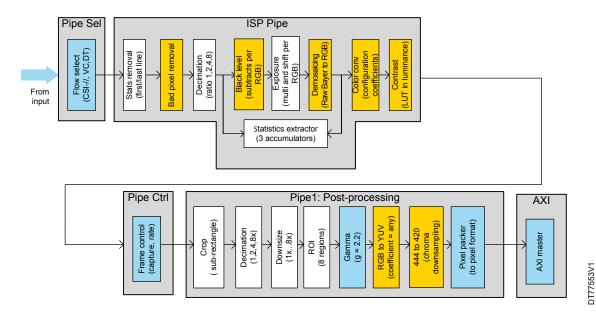

### 3.2.2 Pipe1: Main pipe, postprocessing part

The postprocessing Pipe1 (illustrated in Figure 27) is a pixel pipeline in which postprocessing functions are integrated. The input is from ISP pipe. The applicative Pipe1 is the most featured pixel pipeline, even if the image-processing functions can be shared with Pipe2.

Once the input source is chosen, the data enters Pipe1: Control, where the frame control module manages the capture rate. Then, the data proceeds to Pipe1 postprocessing, which includes several modules. After these processing steps, the data is passed to the pixel packer, which prepares it for transmission to the final output. The AXI master module then sends the processed data over a 64-bit AXI bus with a  $2 \mu s$  latency.

Pipe1 integrates postprocessing modules to relieve the software from time and memory-consuming operations. These functions include cropping to retain only the necessary part of the image for the targeted application, decimation as a cost-effective preprocessing step before downsizing, and downsizing to reduce image resolution.

Additionally, it handles ROI signaling that helps object detection applications, gamma correction before sending data to memory for display operations, and YUV conversion with optional down-sampling to optimize memory usage or match a YUV420 video encoder.

Figure 27. Data flow and processing modules in Pipe1

### 3.2.3 Pixel 2D cropping

The pixel 2D cropping aims at extracting and forwarding a rectangle of pixels. The cropping assigns an X and Y location to the input pixels, selects a configured rectangle among the pixels, and forwards the pixels of this rectangle farther in the pixel pipe. The pixels around the selected rectangle are discarded.

### 3.2.4 Regions of interest (ROI)

Pixel pipes can define up to eight different ROIs to highlight areas in a picture. The purpose of this feature is to draw one rectangle with user size defined for each enabled ROI.

There is no hardware processing within the defined area applied on the image.

As the aim is to draw rectangles on a display, the ROI is supposed to be used when the data flow is RGB at the output of the image-processing blocks.

## 3.2.5 Gamma conversion

This feature implements a gamma compression on each R, G, B component, using a static gamma exponent 2.2. It stores gamma-compressed pictures, as defined in IEC 61966-2-1.

#### 3.2.6 YUV conversion

This module converts the pixels to YUV for JPEG or video encoding applications.

## 3.2.7 Chroma-down sampling

The chroma-down sampling module reduces the chroma resolution from the YUV444 format (arriving) to the potential YUV420 output and sends them to a different channel.

## 3.2.8 Pixel packing

This module operates on the dump pipe (Pipe0) and pixel pipes (Pipe1 to N), organizing the incoming pixels into memory words.

It maps the RGB or YUV data pipeline to standard memory words, supporting various pixel formats. For RGB:

ARGB8888

AN6211 - Rev 1 page 27/55

- RGBA8888

- RGB888p

- RGB565

### For YUV:

- 8 bpp for monochrome

- 1-buffer (444, 422)

- 2-buffer (422, 420)

- 3-buffer (420)

Additionally, it offers the capability to swap R and B (and Cr and Cb) components for more flexibility.

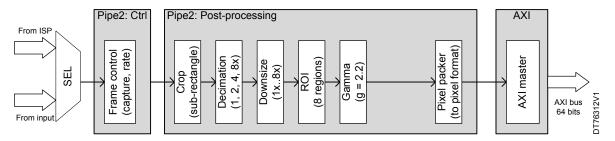

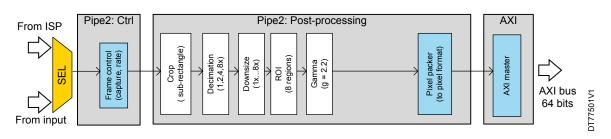

## 3.3 Pipe2: Postprocessing part

The main components of Pipe2, including the controller and general postprocessing functions, are almost identical to those of Pipe1. However, Pipe2 is a lighter pixel pipeline. It can operate in standalone mode or share image-processing functions with Pipe1. As illustrated in Figure 28, this pipeline manages the input and output flow within the image-processing system. The input can be selected from either the ISP (image signal processor) or a direct input virtual channel through a selector (SEL). The AXI master module then sends the processed data over a 64-bit AXI bus.

Figure 28. Data flow and processing modules in Pipe2

The set of postprocessing blocks is reduced compared to Pipe1, as neither the YUV conversion nor the down-sampling YUV444 to YUV420 are integrated in Pipe2. This pipe can have its own image crop area, dedicated downsizing, and it takes benefit of the gamma correction, similar to Pipe1.

AN6211 - Rev 1 page 28/55

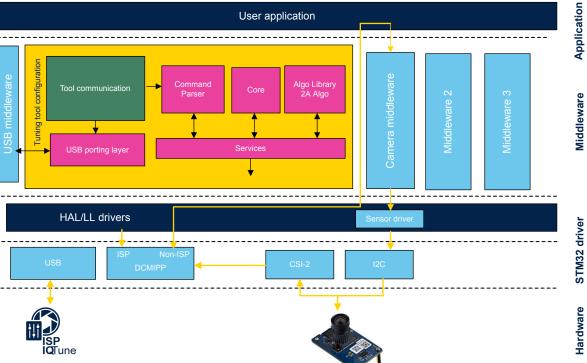

# 4 ISP calibration and IQTune tool

In contrast to a camera module that includes the lens, image sensor, and ISP, the raw sensor module only includes the lens and image sensor

The ISP processes the raw data from the sensor to produce a viewable image. It handles tasks such as white balance and color correction.

Figure 29. Raw sensor module integration

## 4.1 The STM32 ISP IQTune tool

The STM32 ISP IQTune is a comprehensive STM32 ISP tuning software application offering a wide range of features and services to STM32 embedded ISP users.

It consists of two components:

- A desktop application, running on a host computer (Linux® Ubuntu®, Windows® or macOS®).

- An embedded application, running on the STM32 device to be tuned.

$\mathsf{Linux}^{\mathsf{®}}$  is a registered trademark of Linus Torvalds.

Ubuntu® is a registered trademark of Canonical Ltd.

Windows is a trademark of the Microsoft group of companies.

Ubuntu<sup>®</sup> is a registered trademark of Canonical Ltd.

DT76328V

The embedded application architecture includes two middleware components to interface with USB and the IMX335 camera sensor. The user application, running on the target device, enables interaction between the STM32 ISP IQTune software (executed on the host) and the target device, allowing users to control and adjust ISP parameters.

Figure 30. ISP IQTune application architecture

User application Tool communication

STM32 ISP IQTune provides all the services for users to tune the STM32 ISP for an RGB raw Bayer sensor and its associated lens. It provides image quality analyzing capabilities to easily tune the STM32 ISP for any lighting conditions.

For a white-balance profile, the image quality analyzing services provide:

- The possibility to define the white-balance ISP gain.

- The possibility to define the color correction matrix.

- Information and metrics about the color accuracy according to the ISP configuration defined by the user.

AN6211 - Rev 1 page 30/55

## 4.2 ISP for a raw sensor

Illuminants, also called different light sources, have varying spectral distributions and color temperatures (measured in Kelvin) that can affect how the colors are captured by the camera sensor. The white balance adjustment (ISP gain) ensures that the whites are accurately represented, and the color adjustment (color correction matrix) ensures that the colors in the captured image closely match the actual scene.

ISP parameters for different lighting conditions must be tuned during the camera application development process. It ensures that the sensor and lens connected to the device can produce good image quality in terms of white balance and color accuracy under different lighting conditions, meeting user application needs. The results of the tuning procedure are a set of parameters programmed in the ISP and controlled by ISP algorithms.

Note:

For more details about how to tune ISP using the STM32 ISP IQTune, users can check How to tune ISP using the STM32 ISP IQTune wiki article.

The ISP needs to be tuned when used with an RGB raw sensor. With a monochrome raw sensor, the ISP does not need to be tuned.

AN6211 - Rev 1 page 31/55

DT76399V1

# 5 DCMIPP pipeline configuration for various sensor types

This section includes configurations for different types of sensors, including RGB, raw Bayer, monochrome (grayscale), YUV, and JPEG sensors. Each section provides specific instructions for setting up and capturing data from these sensors using the DCMIPP pipes of the STM32 microcontroller.

## 5.1 Configuration for RGB sensors

Incoming RGB pixels from the sensor can be captured by Pipe0, Pipe1, or Pipe2, depending on the DCMIPP capabilities of the STM32 microcontroller.

## Pipe0 configuration

The dump pipe supports more formats than the pixel pipe. One of these formats is the RGB data type. Before Pipe0 retrieves data through the 16-bit parallel interface or the CSI-2 interface connected to the RGB sensor module, the flow selection module must be configured to handle the choice of virtual channels, data, and the acquisition interface.

To correctly capture RGB pixels and write them to the memory using Pipe0, the sensor should be set to output in the adequate RGB format, and Pipe0 needs to be configured to capture frames. Additionally, 2D-cropping and decimation operations can be configured by the software if needed. A dump counter is available to handle unknown lengths of data or to limit the amount of data within a frame. The pixel packer stage packs the pixels into the desired format and buffer, which serves as the storage area for the data.

Frame control

(aspture, rate)

(aspture, rate)

(asub-rectangle)

(becimation

(ratio 1.2.4)

(asub-rectangle)

(asub-rectangle)

(asub-rectangle)

(becimation

(ratio 1.2.4)

(asub-rectangle)

(asub-rectangle)

(becimation

(ratio 1.2.4)

(continue)

(asub-rectangle)

(continue)

(contin

Figure 31. Capturing RGB pixels using Pipe0

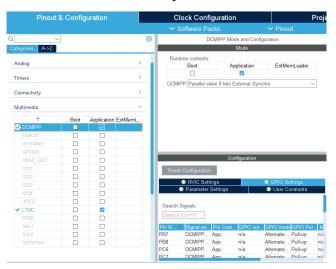

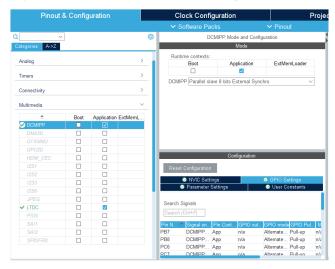

## Pipe1 configuration

The same applies to Pipe1. The flow selection module and frame control are replicated for each dump and pixel pipe, managing the same parameters (CSI-//, VC, DT) along with the capture mode (continuous, snapshot) and rate settings of frame control. The pixel packer module then works on the dump pipe (Pipe0) and pixel pipe (Pipe1), setting the arriving pixels into memory words.

AN6211 - Rev 1 page 32/55

To capture RGB pixels and write them to memory using Pipe1 (which additionally handles image processing (ISP) and post-processing alongside pixel dumping), the modules highlighted in Figure 32 should be enabled. The remaining modules, such as decimation and downsize, are optional and can be utilized for additional image-processing functions.

Figure 32. Capturing RGB pixels using Pipe1

## Pipe2 configuration

To capture RGB pixels and write them to memory using Pipe2, the user needs to configure the pixel packer registers with the following settings:

- Specify the pixel format

- Set the width of the image in pixels

- Define the line stride (pitch) in bytes, which is the number of bytes between the start of one line and the start of the next line (that is, 5760 bytes for RGB888 format)

- Set the height of the image in pixels

Figure 33. Capturing RGB pixels using Pipe2

AN6211 - Rev 1 page 33/55

DT77500V1

## 5.2 Configuration for raw Bayer sensors

This section focuses on capturing raw Bayer pixels from the sensor and transferring the processed data to the memory. The raw Bayer pixels must pass through the highlighted modules in Figure 34 to be converted into RGB pixels:

- 1. Bad pixel removal: enable this module to detect and correct artifacts from the sensor.

- 2. Black Level: this module adjusts the black level offset, which occurs when the sensor sends non-null pixels while capturing a black picture. R, G, and B component offsets are subtracted from the R, Gr, Gb, and B Bayer components.

- 3. Exposure: this module multiplies the R, G, and B components by a configurable gain such as to recenter the colors to more accurate white tones.

- 4. Demosaicing: this module implements a mid-quality conversion from raw Bayer 8 bpp to RGB 24 bpp. The output RGB pixel rate matches the input component rate.

- 5. Gamma: this module applies gamma correction to each R, G, and B color component as defined in the sRGB standard.

- 6. Pixel packer: once data is converted, this stage packs the processed pixels into the desired format. The remaining modules are optional and can be used for additional image-processing functions.

Figure 34. Capturing raw Bayer pixels using Pipe1

## 5.3 Configuration for monochrome (grayscale) sensors

To capture and process grayscale image data from a monochrome sensor, the user can utilize either the dump pipe or the pixel pipe (Pipe1) for further processing. For incoming grayscale pixels, it is necessary to enable the flow selection to direct the data flow through Pipe1. In this configuration, the following modules should be disabled: bad pixel removal, black level, demosaicing, color conversion and contrast.

AN6211 - Rev 1 page 34/55

Figure 35. Capturing monochrome pixels using Pipe1

# 5.4 Configuration for YUV sensors

To capture YUV pixels from YUV sensors and process them, either dump pipe (Pipe0) or pixel pipes (Pipe1, Pipe2) can be used. Dumping through Pipe0 is ideal for applications that require luminance and chrominance information. Alternatively, using Pipe1 to process YUV data and convert it to RGB using the ColorConv stage.

### Pipe0 and Pipe1 configuration