## Single channel pyrofuse driver

#### Introduction

The L9965P / L99BM2P is a single-channel pyrofuse driver that can quickly and reliably break a high-voltage battery line in the event of a short circuit or car crash.

To accomplish this function, the device integrates a dual FET output stage consisting of a high-side and a low-side power MOSFET. The stage is equipped with a closed-loop current feedback and can be configured to deliver controlled firing profiles by programming both current intensity and duration. Moreover, the power stage is able to perform a defined number of auto-retry attempts based on the success or failure of the deployment.

The device embeds a programmable firing logic allowing it to generate the fire trigger from two SPI commands or two digital inputs (FENH/FENL). The digital input triggers are compatible with both level and PWM encoding, supporting 16 kHz and 125 kHz encoded signals.

The device supports an external capacitor as an energy reserve (ER). An internal boost regulator can be used to control the ER cap voltage around a programmable setpoint.

A low-power operation strategy allows minimizing the idle consumption, keeping the device in an ultralow-power state while still performing all the diagnostic sweeps with a programmable periodicity. During such an ultralow-power state, the device is still sensitive to wake up sources to be ready to fire at any time.

Operation in conjunction with the L9965C/L99BM2C companion chip simplifies IC control loops, as many safety mechanisms are already implemented by the L9965C/L99BM2C.

# 1 Application scenarios

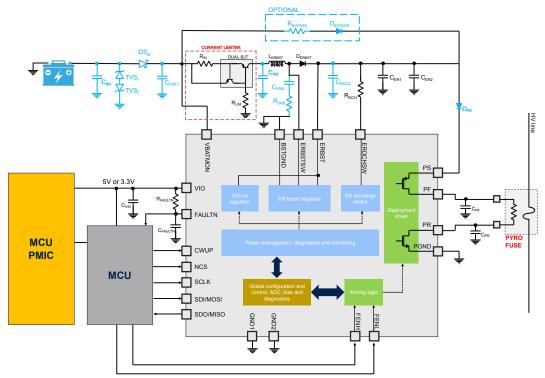

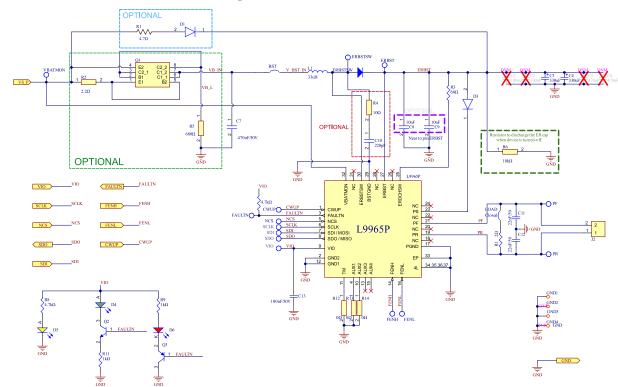

In case the IC is directly connected to the battery, it is recommended to implement the application circuits shown in Figure 1.

Figure 1. Application circuit with battery supply

The current limiter circuit has the aim to avoid uncontrolled inrush current from battery towards  $C_{ER}$  and could be removed in case the energy source is limited in alternative way. The presence of the feed forward path ( $D_{BYPASS}/R_{BYPASS}$ ) is only needed in case the device is expected to be able to deploy immediately after powerup, before the BOOST circuit charged the tank capacitor.

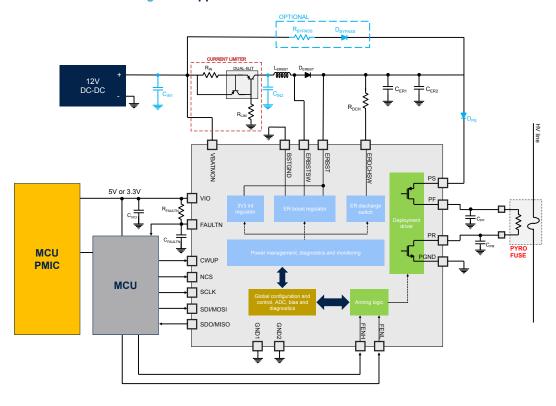

If the device is supplied by a DC-DC converter, it is recommended to use the fallowing circuit as shown in Figure 2.

AN6194 - Rev 2 page 2/34

Figure 2. Application circuit with DC-DC converter

In this scenario the current limiter circuit cannot be mounted if the DC-DC converter has got its own current limitation.

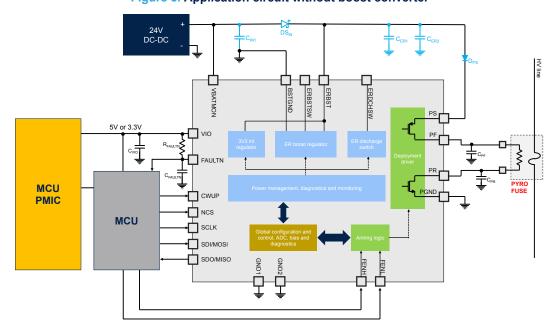

If the ERBST is not needed, the recommended application circuit is the Figure 3.

Figure 3. Application circuit without boost converter

AN6194 - Rev 2 page 3/34

## External components sizing

#### 2.1 **ERBST** components

The suggested inductor value for L<sub>FRBST</sub> is 33 μH ± 20 %, with a maximum DCR of 1.5 Ω. An example is the VLS4020CX-330M-H from TDK.

The diode for D<sub>FRBST</sub> shall be a Schottky diode and shall sustain a maximum current of 500 mA (input power limitation disabled), with a maximum forward voltage of 1.2 V. An example is the STPS1L40ZFY from STMicroelectronics.

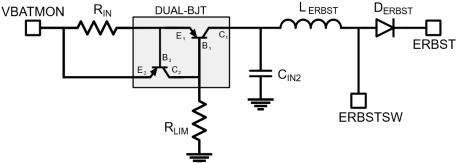

To limit the inrush current from the battery in the PS node during the system power-on and avoid an unwanted trigger of the ERBST overcurrent fault (ERBST OC bit in the ERBOOST register), a current limiter can be placed before the ERBST branch (LERBST and DERBST) and after the VBATMON. In this application can be used a double BJT, as example the ZXTP56060FDBQ.

These are the possible scenarios:

- In normal condition, the first PNP connected to the L<sub>FRBST</sub> is turned-on and the supply current flows through ERBST, instead, the second PNP turns off through the pull-down resistor.

- Once of target current limit is reached, the second PNP connected to RIIM is turned-on modulating the VBF at the first PNP which keeps the current near to the target.

Figure 4. Inrush current limit

L<sub>ERBST</sub> **DUAL-BJT**

To allow this behavior, it is needed to size RIN and RLIM according to the maximum current desired and the VBE.on of the chosen BJT.

The R<sub>IN</sub> is sized to avoid reaching the OC threshold, as example considering:

- $I_{ERBST\ PEAK\ LIM\ 0,min}$  = 330 mA  $\rightarrow$   $I_{CE,max}$  = -300 mA

- $V_{BF on} = -0.7 V$

- $R_{IN} = V_{BE,on} / I_{CE,max} = 2.33 \Omega$

The R<sub>LIM</sub> is sized to ensure that second BJT operates in the linear region even at minimum operating battery, as example for the ZXTP56060FDBQ:

- Current gain h<sub>FE.min</sub> = I<sub>C1</sub> / I<sub>B1</sub> = 50

- for  $I_{C1} \sim 300 \text{ mA} \rightarrow I_{B1,max} = 6 \text{ mA}$

- $V_{C2} = V_{B1} = R_{LIM} \times I_{B1,max}$

- and:  $V_{C2} = V_{bat,min} + V_{CE2,ON}$

considering:  $V_{CE2,ON}$  = - 2V;  $V_{bat,min}$  = 6 V;  $R_{LIM}$  = 667  $\Omega$

In case an immediate deploy ability is requested after the power up, a feed-forward branch composed of a R<sub>BYPASS</sub> and D<sub>BYPASS</sub> can be mounted. The diode is sized to sustain the maximum deployment current I<sub>DFPI OY</sub>.

The resistance R<sub>BYPASS</sub> can be sized considering the desired deploy current, as example:

- supposing: I<sub>DEPLOY</sub> = 1.5 A, V<sub>batt</sub> = 12 V

- V<sub>batt</sub> V<sub>batt,min</sub> V<sub>DBYPASS</sub> = I<sub>DEPLOY</sub> × R<sub>BYPASS</sub>

- $R_{BYPASS} = (V_{batt} V_{batt,min} V_{DBYPASS}) / I_{DEPLOY} = 3.5 \Omega$

AN6194 - Rev 2 page 4/34

To improve the EMC performance can be added a snubber circuit between the ERBSTSW pin and the BSTGND. The suggested values are:  $C_{SNB}$  = 220 pF and  $R_{SNB}$  = 10  $\Omega$ .

By the way, the values of this snubber, and the related cutoff frequency should be tuned according to the emission performance at the system level.

## 2.2 Energy reserve capacitor

The minimum value of the energy reserve capacitor must be sized considering the amount of charge that it has to provide during the deployment event.

According to this, the following parameters must be considered:

- Deployment current, I<sub>DEPLOY</sub>

- Deployment time, t<sub>DEPLOY</sub>

- Minimum PS voltage, set by the minimum ERBST wake-up threshold or by minimum IC operating voltage

- Voltage drop at tank capacitor terminals, ΔV<sub>DROP,max</sub>

Regarding the minimum PS voltage, it is considered under the condition of maximum ERBST regulated voltage and minimum ERBST wake-up threshold, to minimize power consumption as much as possible (ERBST switching activity reduced to a minimum).

The formula to size the value of the energy reserve capacitor is the following:

$$C_{min} = \frac{I_{DEPLOY}^* t_{DEPLOY}}{\Delta V_{DROP}} \tag{1}$$

The worst case is obtained considering:

- Minimum deployment current, I<sub>DEPLOY</sub> = 1.5 A

- Maximum deployment time, t<sub>DEPLOY</sub> = 1.05 ms

- Minimum PS voltage, V<sub>ER WKUP TH0</sub> = 16 V

- Minimum PS voltage, V<sub>PS,min</sub> = 6 V

- Maximum voltage drop, ΔV<sub>DROP,max</sub> = V<sub>ER\_WKUP\_TH0</sub> V<sub>PS,min</sub> = 16 V 6 V = 10 V

So, the minimum value of the energy reserve capacitor can be calculated as:

$$C_{min} = \frac{I_{DEPLOY,min}^* t_{DEPLOY,max}}{\Delta V_{DROP,max}} = \frac{1.5A^*1.05ms}{10V} \sim 200 \mu F$$

(2)

This value is calculated considering only the deployment current. If a battery loss scenario must also be considered, the IC consumption has to be included in the calculation. In any case, since I<sub>BASE\_NORM</sub> = 2.4 mA, the main contribution is due to deployment current. To allow multiple deployments, the tank capacitor must be sized accordingly.

For safety reasons, to account for ER capacitor degradation due to temperature and aging, it is recommended to mount two capacitors in parallel, either of the same value or with different sizes.

A typical value of the ER capacitors based on standard deployment profile could be 2 x 330  $\mu$ F. An example is the EEEFK1V331P capacitor from *Panasonic*.

When the system powers off, to avoid residual charge on the energy reserve capacitor, a passive pull-down path can optionally be mounted. A suggested value of about 1  $k\Omega$  is recommended to avoid significant consumption from battery when the system is off. Be careful with the resistor's power rating to avoid unwanted leakage occurring during lifetime.

### 2.3 Battery filter

Based on customer application, the following additional components may be useful (highlighted in light blue in Figure 1):

- TVS diode to clamp the input voltage (IC AMR is 40 V) and the reverse voltage (-14 V for 12 V system, -26 V for 24 V system)

- DS<sub>IN</sub> diode to prevent damage from reverse polarity. It is recommended to use a Schottky diode to keep the series voltage drop as low as possible on the battery line.

- Tank capacitors (C<sub>IN1</sub>, C<sub>IN2</sub>) after the supply and before the L<sub>ERBST</sub> to mitigate voltage drops due to current spike.

AN6194 - Rev 2 page 5/34

• A capacitor bank, C<sub>EMC1</sub> and C<sub>EMC2</sub>, serves as a filter stage useful for improving EMC performance by filtering noise from the battery and voltage spikes. In a typical application scenario, a range of different value capacitors can be mounted (1 μF, 100 nF, 1 nF).

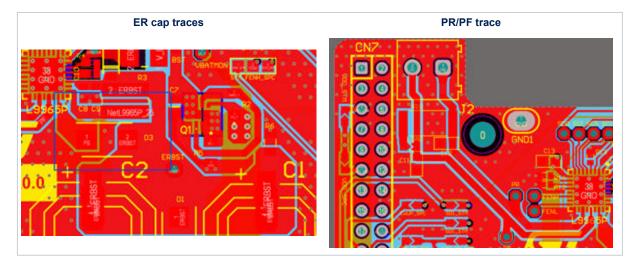

## 2.4 Power stage filter

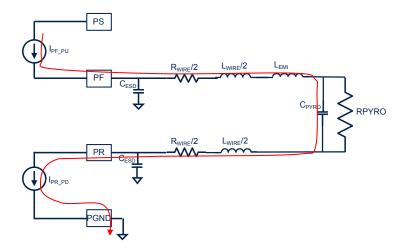

The power stage consists of two power MOSFETs (triggered by two independent paths) connected to the pyrofuse through the PF and PR pins.

In order to improve EMC performance, it is required to add the  $C_{PF}$  and  $C_{PR}$  capacitors (minimum value 13 nF) on the PF and PR pins.

In a typical application scenario:

- 100 pF and 1 nF capacitors are mounted near the PF and PR pins.

- A TVS diode can be optionally mounted near the PF and PR pins.

- A 100 nF capacitor is mounted near the connector of the pyrofuse element.

In case the system shall survive to PF and PR shorted to permanently supplied battery line with IC power off, D<sub>PS</sub> diode can be optionally mounted in series to PS pin to protect the device from back feeding towards the ERCAP.

AN6194 - Rev 2 page 6/34

## 3 Device configuration

#### 3.1 NVM configuration (write command)

The MCU shall write the following commands to configure the NVM:

- 1. Write 0x55 in the SPECIAL KEY register for partial unlock

- 2. Write 0x33 in the SPECIAL KEY register for full unlock

- 3. Write NVM configuration in CLIENT\_NVM\_REG\_x registers

- 4. Write 0x3 in the NVM\_OP\_CMD register to upload data into the NVM

- Write 0xAA in the SPECIAL\_KEY register for lock restoring, or wait for t<sub>CFG\_TIMEOUT</sub> expiration for automatic locking.

Every time the NVM is downloaded, the CLIENT CONFIG CRC bit field is internally written.

Every time the NVM is written, the NVM\_UPLOAD\_COUNT decreases by 1, starting from 0x1F.

## 3.2 ERBST configuration

By default, the ERBST is disabled.

Together with the enabled bit, there are other bitfields to be configured in the NVM:

- ERBST EN = 1 enables the ERBST regulator

- ERBST\_SET bitfield selects the regulated voltage between 18 V and 24 V

- VER WKUP bitfield selects the wake up threshold between 16 V and 22 V

- **PIN LIMIT** = 1 limits the peak input current to 440 mA.

## 3.3 Load thresholds configuration

When the pyro igniter resistance measurement diagnostic is executed, the result is compared with the low and high thresholds stored in the NVM.

The relationship between the low-resistance threshold and the  $V_{RES\ LOW\ TH}$  code is the following:

$$R_{LOW} = \frac{4*(VRES\_LOW\_TH)_{dec}*LSB_0}{I_{PF\_PU}}$$

(3)

Example:

$$R_{LOW} = \frac{4*(0xF)_{dec}*0.651mV}{40mA} = 1\Omega$$

The relationship between the high-resistance threshold and the  $V_{RES\ HIGH\ TH}$  code is the following:

$$R_{HIGH} = \frac{4*(VRES\_HIGH\_TH)_{dec}*LSB_0}{I_{PR\_PD}}$$

(4)

Example:

$$R_{HIGH} = \frac{4*(0x2E)_{dec}*0.651mV}{40mA} = 3\Omega$$

### 3.4 Energy reserve capacitor diagnostic

The diagnostic of an energy reserve capacitor is done by estimating its capacitance value and its ESR (equivalent series resistance) value by means of an external  $R_{\rm DCH}$  resistor.

The R<sub>DCH</sub> resistor limits the current that flows inside the IC and it is sized considering a typical diagnostic current of 0.5 A. The value used in simulations is 62  $\Omega$ , so the commercially suggested value is 68  $\Omega$ .

Considering a typical scenario with 2 x 330  $\mu$ F, the low capacitance threshold can be set to approximately 400  $\mu$ F (middle value between 1 x 330  $\mu$ F and 2 x 330  $\mu$ F).

The following formula can be used for ERCAP C THR:

$$C_{LOW}[\mu F] = \frac{("00"\&ERCAP\_C\_THR[7:0]\&"0000")_{dec}*LSB_C}{R_{ERDCHSW}}$$

(5)

AN6194 - Rev 2 page 7/34

$$Example: C = \frac{("00"\&0x40\&"0000")_{dec}*25.35\mu F^*\Omega}{68\Omega} = 381.74\mu F$$

Taking the EEEFK1V331P capacitor as a reference, the ESR value is 80 mΩ.

Considering a typical scenario with 2 x 330 μF, the high ESR threshold can be set near 160 mΩ.

The following formula can be used for **ERCAP ESR THR**:

$$ESR[m\Omega] = (ERCAP\_ESR\_THR[6:0]\&"0000")_{dec} * \frac{LSB_{ESR} * R_{ERDCHSW}}{1000}$$

$$Example: ESR = (0x4\&"0000")_{dec} * \frac{38.52\mu*68\Omega}{1000} = 167.64m\Omega$$

(6)

### 3.5 Deployment configuration

The deployment current is set through the I\_DEP\_CFG bitfield in the NVM:

- 1. *I DEP CFG* = 00 sets 1.50 A min

- 2. I DEP CFG = 01 sets 1.75 A min

- 3. I DEP CFG = 10 sets 2.00 A min

- 4. I DEP CFG = 11 sets 3.50 A min.

The deployment time is set through the *T DEP CFG* bitfield in the NVM.

The relationship between deployment time and **T DEP CFG** code is the following:

$$t_{DEPLOY} = (T_DEP_CFG)_{dec} * t_{DEPLOY\_RES}$$

$$Example: t_{DEPLOY} = (0x2F)_{dec} * 16\mu s = 752\mu s$$

$$(7)$$

The deployment timer resolution t<sub>DEPLOY</sub> RES is affected by an error of ±8.1 %.

The deployment time monitor is set through the **DEP MON THR** bitfield in the NVM.

The relationship between deployment timer threshold and DEP\_MON\_THR code is the following:

$$t_{DEP\_MON\_TH} = (DEP\_MON\_THR)_{dec} * t_{DEP\_MON\_TH\_RES}$$

$$Example: t_{DEP\_MON\_TH} = (0x16)_{dec} * 32\mu s = 704\mu s$$

(8)

The HS\_RET\_CFG bitfield sets the number of deploy retries (1, 2, 3 or 4).

The *HS\_RET\_DLY\_CFG* bitfield sets the delay between retries (0.5 ms, 1 ms, 1.5 ms, or 2 ms) in case of deployment by FENH/FENL.

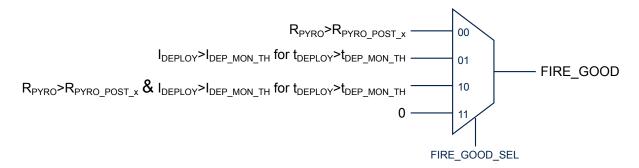

The FIRE\_GOOD\_SEL bitfield selects the source of the FIRE\_GOOD signal, as shown in Figure 5.

Figure 5. FIRE\_GOOD signal selection

AN6194 - Rev 2 page 8/34

## 3.6 FAULTN pin masking

It is possible to mask the effects of faults on the FAULTN pin. This is shown in Table 1.

Table 1. FAULTN pin masking summary

| Bit                        | Register          | FAULTN masking                                      |

|----------------------------|-------------------|-----------------------------------------------------|

| ERBST_OV_FAULTN_MSK        | CLIENT_NVM_REG_0  | ERBST_OV fault masked                               |

| PYRO_HIGH_RES_FAULTN_MSK   | CLIENT_NVM_REG_1  | PYRO_HIGH_RES fault masked                          |

| PYRO_LOW_RES_FAULTN_MSK    | CLIENT_NVM_REG_1  | PYRO_LOW_RES fault masked                           |

| ERBSTSW_OT_FAULTN_MSK      | CLIENT_NVM_REG_2  | ERBST_OT fault masked                               |

| ERBSTSW_OC_FAULTN_MSK      | CLIENT_NVM_REG_2  | ERBST_OC fault masked                               |

| ERBST_DLOSS_FAULTN_MSK     | CLIENT_NVM_REG_3  | ERBST_DLOSS fault masked                            |

| PF_FET_FAIL_FAULTN_MSK     | CLIENT_NVM_REG_5  | PF_FET_FAIL fault masked                            |

| PF_PR_STB_STG_FAULTN_MSK   | CLIENT_NVM_REG_6  | PF_STG, PF_STB, PR_STG and PR_STB faults masked     |

| ERCAP_FAULTN_MSK           | CLIENT_NVM_REG_6  | ERCAP faults masked                                 |

| LEAK_LOW_FAULTN_MSK        | CLIENT_NVM_REG_6  | VRCM_STB_FAIL and VRCM_STG_FAIL faults masked       |

| VRCM_HWSC_FAULTN_MSK       | CLIENT_NVM_REG_6  | VRCM_HWSC_FAIL fault masked                         |

| PF_PR_POST_HWSC_FAULTN_MSK | CLIENT_NVM_REG_6  | PF_PR_POST_HWSC_FAIL fault masked                   |

| PF_PR_PRE_HWSC_FAULTN_MSK  | CLIENT_NVM_REG_6  | PF_PR_PRE_HWSC_FAIL fault masked                    |

| PR_FET_FAIL_FAULTN_MSK     | CLIENT_NVM_REG_8  | PF_FET_STG and PF_FET_FAIL faults masked            |

| FENX_TIMEOUT_FAULTN_MSK    | CLIENT_NVM_REG_10 | FENx_PWM_TIMEOUT and FENx_LEV_TIMEOUT faults masked |

| FENX_LOW_FREQ_FAULTN_MSK   | CLIENT_NVM_REG_10 | FENx_LOW_FREQ fault masked                          |

| FENX_HIGH_FREQ_FAULTN_MSK  | CLIENT_NVM_REG_10 | FENx_HIGH_FREQ fault masked                         |

| PS_OV_FAULTN_MSK           | CLIENT_NVM_REG_11 | PS_OV fault masked                                  |

## 3.7 Deployment inhibition masking

It is possible to mask the effects of faults on the fire inhibition. This is shown in Table 2.

Table 2. Deployment inhibition masking summary

| Bit                  | Register           | Deployment inhibition masking                     |

|----------------------|--------------------|---------------------------------------------------|

| ERBST_OV_FIRE_MSK    | CLIENT_NVM_REG_0   | Inhibition from ERBST_OV masked                   |

| PF_FET_FAIL_FIRE_MSK | CLIENT_NVM_REG_7 q | Inhibition from PF_FET_STG and PF_FET_FAIL masked |

| PR_FET_FAIL_FIRE_MSK | CLIENT_NVM_REG_8   | Inhibition from PR_FET_STB and PR_FET_FAIL masked |

| GND_LOSS_BSTGND_MSK  | CLIENT_NVM_REG_9   | Inhibition from BSTGND_LOSS masked                |

| PS_OV_FIRE_MSK       | INTERNAL_CFG       | Inhibition from PS_OV masked                      |

AN6194 - Rev 2 page 9/34

## 3.8 Device configuration example

## 3.8.1 Example of non-volatile memory (NVM) configuration

An example of how the non-volatile memory can be configured is shown in Table 3. The following configuration is referred to the application scenario in Figure 1.

Table 3. NVM configuration example

| Register name     | Address | Data  | Notes                                                                                          |  |

|-------------------|---------|-------|------------------------------------------------------------------------------------------------|--|

| SPECIAL_KEY       | 0x30    | 0x055 | 0x55 = partial unlock                                                                          |  |

| SPECIAL_KEY       | 0x30    | 0x033 | 0x33 = full unlock                                                                             |  |

|                   |         |       | ERBST_OV_FIRE_MSK = 0 (no fire mask)                                                           |  |

|                   |         |       | ERBST_OV_FAULTN_MSK = 0 (no FAULTN mask)                                                       |  |

|                   |         |       | FENL_PU_PD = 0 (pull-up enabled)                                                               |  |

|                   |         |       | FENH_PU_PD = 1 (pull-down enabled)                                                             |  |

|                   |         |       | FENL_FREQ = 1 (16 kHz)                                                                         |  |

| CLIENT_NVM_REG_0  | 0x20    | 0x077 | FENH_FREQ = 1 (16 kHz)                                                                         |  |

|                   |         |       | FENL_LEVEL = 0 (deploy trigger: low level if FENL_MODE = 0, 25 % duty cycle if FENL_MODE = 1)  |  |

|                   |         |       | FENH_LEVEL = 1 (deploy trigger: high level if FENH_MODE = 0, 75 % duty cycle if FENH_MODE = 1) |  |

|                   |         |       | FENL_EN = 1 (FENL decoded enabled)                                                             |  |

|                   |         |       | FENH_EN = 1 (FENH decoded enabled)                                                             |  |

|                   |         |       | FENX_FAULT_PERIOD = 01 (8 periods filter if FENx_MODE = 1)                                     |  |

|                   |         |       | FENX_DEGLITCH = 11 (1280 us filter if FENx_MODE = 0)                                           |  |

| CLIENT_NVM_REG_1  | 0x21    | 0x1C5 | PYRO_HIGH_RES_FAULTN_MSK = 0 (no FAULTN mask)                                                  |  |

| CLIENT_NVIW_REG_T | UXZI    | 0.00  | PYRO_LOW_RES_FAULTN_MSK = 0 (no FAULTN mask)                                                   |  |

|                   |         |       | I_DEP_CFG = 01 (1.75 A deployment current)                                                     |  |

|                   |         |       | FENX_DLY_CFG = 01 (2 ms deploy trigger delay)                                                  |  |

|                   |         |       | ERBSTSW_OT_FAULTN_MSK = 0 (no FAULTN mask)                                                     |  |

| CLIENT_NVM_REG_2  | 0x22    | 0x00F | ERBSTSW_OC_FAULTN_MSK = 0 (no FAULTN mask)                                                     |  |

|                   |         |       | VRES_LOW_TH = $0xF$ (equivalent resistance = $1 \Omega$ )                                      |  |

|                   |         |       | HS_RET_CFG = 0x3 (4 deploy retries)                                                            |  |

| CLIENT_NVM_REG_3  | 0x23    | 0x35C | VRES_HIGH_TH = 0x2E (equivalent resistance = $3 \Omega$ )                                      |  |

|                   |         |       | ERBST_DLOSS_FAULTN_MSK = 0 (no FAULTN mask)                                                    |  |

|                   |         |       | VRES_THR_POST_SEL = 0 (pyrofuse resistance after deployment equal to 99 $\Omega$ )             |  |

|                   |         |       | PYRO_RES_EN = 1 (cyclic pyrofuse res meas enabled)                                             |  |

|                   |         |       | LEAK_EN = 1 (cyclic VRCM and leakage test enabled)                                             |  |

| CLIENT_NVM_REG_4  | 0x24    | 0x1F6 | ADC_HWSC_EN = 1 (cyclic HWSC enabled)                                                          |  |

|                   |         |       | FET_EN = 1 (cyclic FETs tests enabled)                                                         |  |

|                   |         |       | ER_CAP_EN = 1 (cyclic ER cap diag enabled)                                                     |  |

|                   |         |       | DIAG_ROUTINE_PERIOD = 01 (300 ms diagnostic period)                                            |  |

|                   |         |       | HS_RET_DLY_CFG = 10 (1.5 ms between deploy retries)                                            |  |

|                   |         |       | FET_NCYCLE = 10 (16 cycles as periodicity)                                                     |  |

| CLIENT_NVM_REG_5  | 0x25    | 0x216 | PYRO_RES_NCYCLE = 00 (1 cycle as periodicity)                                                  |  |

|                   |         |       | PF_FET_FAIL_FAULTN_MSK = 0 (no FAULTN mask)                                                    |  |

AN6194 - Rev 2 page 10/34

| Register name       | Address | Data  | Notes                                                                                                             |

|---------------------|---------|-------|-------------------------------------------------------------------------------------------------------------------|

|                     |         |       | DEP_MON_THR = $0x16$ ( $22*32 = 704$ us as deploy timer threshold for fire good signal)                           |

|                     |         |       | ER_CAP_NCYCLE = 11 (64 cycles as periodicity)                                                                     |

|                     |         |       | PF_PR_STB_STG_FAULTN_MSK = 0 (no FAULTN mask)                                                                     |

|                     |         |       | ERCAP_FAULTN_MSK = 0 (no FAULTN mask)                                                                             |

| CLIENT NVM DEC. 6   | 0x26    | 0x301 | LEAK_LOW_FAULTN_MSK = 0 (no FAULTN mask)                                                                          |

| CLIENT_NVM_REG_6    | 0x26    | 0x301 | VRCM_HWSC_FAULTN_MSK = 0 (no FAULTN mask)                                                                         |

|                     |         |       | PF_PR_POST_HWSC_FAULTN_MSK = 0 (no FAULTN mask)                                                                   |

|                     |         |       | PF_PR_PRE_HWSC_FAULTN_MSK = 0 (no FAULTN mask)                                                                    |

|                     |         |       | ADC_HWSC_NCYLE = 01 (4 cycles as periodicity)                                                                     |

|                     |         |       | PF_FET_FAIL_FIRE_MSK = 0 (no FAULTN mask)                                                                         |

| CLIENT_NVM_REG_7    | 0x27    | 0x02F | LEAK_NCYCLE = 00 (1 cycle as periodicity)                                                                         |

|                     |         |       | T_DEP_CFG = $0x2F$ ( $47*16 = 752$ us deployment time)                                                            |

|                     |         |       | VER_WKUP = 100 (20 V as wake-up threshold)                                                                        |

|                     |         |       | ERBST_SET = 110 (24 V as target threshold)                                                                        |

| CLIENT_NVM_REG_8    | 0x28    | 0x134 | PIN_LIMIT = 1 (input limitation enabled)                                                                          |

|                     |         |       | PR_FET_FAIL_FIRE_MSK = 0 (no fire mask)                                                                           |

|                     |         |       | PR_FET_FAIL_FAULTN_MSK = 0 (no FAULTN mask)                                                                       |

|                     |         |       | GND_LOSS_BSTGND_MSK = 0 (no FAULTN mask)                                                                          |

| CLIENT_NVM_REG_9    | 0x29    | 0x140 | ERBST_EN = 1 (ERBST enabled)                                                                                      |

|                     |         |       | ERCAP_C_THR = 0x40 (equivalent to 382 uF)                                                                         |

|                     |         |       | FENX_TIMEOUT_FAULTN_MSK = 0 (no FAULTN mask)                                                                      |

| CLIENT_NVM_REG_10   | 0x2A    | 0x004 | FENX_LOW_FREQ_FAULTN_MSK = 0 (no FAULTN mask)                                                                     |

| CEIEIT ITTIMENED TO | UNZA    | 0,004 | FENX_HIGH_FREQ_FAULTN_MSK = 0 (no FAULTN mask)                                                                    |

|                     |         |       | ERCAP_ESR_THR = $0x4$ (equivalent to $168 \text{ m}\Omega$ )                                                      |

|                     |         |       | NVM_UPLOAD_COUNT (read-only content)                                                                              |

|                     |         |       | FAULTN_DIS = 0 (FAULTN enabled)                                                                                   |

| CLIENT_NVM_REG_11   | 0x2B    | 0x004 | FIRE_GOOD_SEL = 01 (fire good set if deployment current exceeds threshold for longer than deploy timer threshold) |

|                     |         |       | PS_OV_FAULTN_MSK = 0 (no FAULTN mask)                                                                             |

| CLIENT_NVM_REG_12   | 0x2C    | -     | CLIENT_CONFIG_CRC (read-only content)                                                                             |

| NVM_OP_CMD          | 0x31    | 0x003 | NVM upload and download                                                                                           |

| SPECIAL_KEY         | 0x30    | 0x0AA | 0xAA = lock                                                                                                       |

AN6194 - Rev 2 page 11/34

## 3.8.2 Example of volatile memory configuration

An example of how the volatile memory can be configured is shown in Table 4.

Table 4. VM configuration example

| Register name      | Address   | Data   | Notes                                                                             |

|--------------------|-----------|--------|-----------------------------------------------------------------------------------|

| CRC                | 0x07      | 0x000  | NVM_CRC_FAIL_MSK = 0 (deploy inhibition and FAULTN assertion in case of NVM fail) |

|                    |           |        | CYC_CRC_DIS = 0 (cyclic CRC checks enabled)                                       |

|                    |           |        | OSC_SS_EN = 1 (spread spectrum enabled)                                           |

| INTERNAL_CFG       | 0x15      | 0x004  | PR_PD_DIS = 0 (pull-down on PR enabled)                                           |

|                    |           |        | PS_OV_FIRE_MSK = 0 (no fire mask)                                                 |

| LEVEL MODE (FENH_M | IODE = FE | NL_MO  | DE = 0)                                                                           |

| FENUL CONFIC       | 0.03      | 0,4000 | FENL_MODE = 0 (FENL level based decoding)                                         |

| FENH_L_CONFIG      | 0x03      | 0x000  | FENH_MODE = 0 (FENH level based decoding)                                         |

|                    | 0x02      | 0x00D  | FENL_INT_CHECK_EN = 1 (FENL integrity checks enabled when in level mode)          |

| EALILE DIAC CONFIC |           |        | FENH_INT_CHECK_EN = 1 (FENH integrity checks enabled when in level mode)          |

| FAULT_DIAG_CONFIG  |           |        | FAULTN_FORCE = 0 (FAULTN forced high)                                             |

|                    |           |        | FAULTN_CYCLIC_PULSE = 1 (FAULTN cyclic pulses enabled)                            |

| PWM MODE (FENH_MC  | DDE = FEN | L_MOD  | E = 1)                                                                            |

| FENUL CONFIC       | 0x03      | 0,,003 | FENL_MODE = 1 (FENL PWM based decoding)                                           |

| FENH_L_CONFIG      | UXUS      | 0x003  | FENH_MODE = 1 (FENH PWM based decoding)                                           |

|                    |           |        | FENL_INT_CHECK_EN = 0 (PWM mode)                                                  |

| EALILE DIAC CONFIC | 0x02      | 0x001  | FENH_INT_CHECK_EN = 0 (PWM mode)                                                  |

| FAULT_DIAG_CONFIG  |           |        | FAULTN_FORCE = 0 (FAULTN forced high)                                             |

|                    |           |        | FAULTN_CYCLIC_PULSE = 1 (FAULTN cyclic pulses enabled)                            |

AN6194 - Rev 2 page 12/34

## 4 Device check

The user shall check the status of the IC by reading the following registers:

- BMS\_ID, CHIP\_ID and SPI\_STATUS registers to check the integrity of SPI communication

- INTERNAL\_STATUS register to check wake-up source and internal fails

- ERBOOST register to check the status of the ERBST regulator

- TEMPERATURE register to read the internal temperature of the IC.

The formula to convert the TEMPERATURE\_CODE bitfield is the following:

$$T_{J}[^{\circ}C] = 1.74192*TEMPERATURE\_CODE - 89.988$$

$$Example: T_{J}[^{\circ}C] = 1.74192*(0x40)_{dec} - 89.988 = 21.49$$

The error associated with the temperature measurement is  $\pm 10~^{\circ}\text{C}$  (T<sub>J\_ERR</sub>).

AN6194 - Rev 2 page 13/34

## 5 Diagnostics

## 5.1 Available diagnostics

#### **5.1.1** ABIST

The ABIST checks the analog comparators. In cyclic diagnostics, it is not possible to disable the ABIST, so it runs at every cycle. In case of fault, then ABIST\_FAIL = 1.

#### 5.1.2 Hardware self-check (HSWC)

The HWSC checks the integrity of PF-PR pre-deployment path, PF-PR post-deployment path, and VRCM path. In case of fault, then respectively PF\_PR\_PRE\_HWSC\_FAIL = 1, PF\_PR\_POST\_HWSC\_FAIL = 1 and/or VRCM\_HWSC\_FAIL = 1.

#### 5.1.3 Voltage regulator current monitor (VRCM) check

The VRCM is checked in two steps:

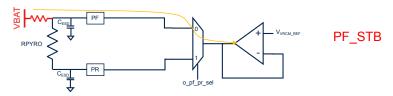

1. The I<sub>PF\_PU</sub> is enabled and the VRCM is connected to the PF pin. If the VRCM works properly, then VRCM\_STB\_FAIL = 0, otherwise VRCM\_STB\_FAIL = 1 (see Figure 6).

Figure 6. VRCM check: sink current

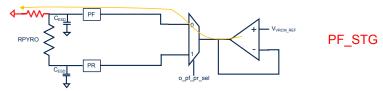

2. The I<sub>PR\_PD</sub> is enabled and the VRCM is connected to the PR pin. If the VRCM works properly, then VRCM\_STG\_FAIL = 0, otherwise VRCM\_STG\_FAIL = 1 (see Figure 7).

Figure 7. VRCM check: source current

The active pull-down connected to the PR pin (I<sub>ACT PD PR</sub>) is automatically disabled during this check.

AN6194 - Rev 2 page 14/34

### 5.1.4 Pyro outputs leakage test

The pyro outputs leakage test checks that no leakages are present on the PF and PR pins. It works in two steps:

- 1. The VRCM is connected to PF pin

- a. If there is a leakage to the battery, then PF\_STB = 1 (see Figure 8)

Figure 8. PF short to battery (PF STB)

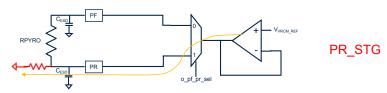

b. If there is a leakage to the ground, then PF\_STG = 1 (see Figure 9)

Figure 9. PF short to ground (PF STG)

- 2. The VRCM is connected to the PR pin.

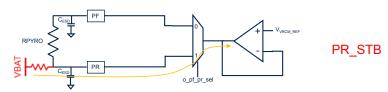

- a. If there is a leakage to the battery, then PR\_STB = 1 (see Figure 10)

Figure 10. PR short to battery (PR STB)

b. If there is a leakage to the ground, then PR\_STG = 1 (see Figure 11)

Figure 11. PR short to ground (PR STG)

The active pull-down connected to the PR pin (I<sub>ACT PD PR</sub>) is automatically disabled during this check.

AN6194 - Rev 2 page 15/34

#### 5.1.5 Pyro igniter resistance measurement

Both  $I_{PF\_PU}$  are enabled, and the  $I_{PF\_PU}$  current flows in the external load generating a differential voltage across the load that is measured by the internal ADC (see Figure 12).

Figure 12. Load resistance measurement

The result of the pre-deployment resistance measurement is stored in the RES\_MEAS\_PRE register and it is compared with the two thresholds stored in the  $V_{RES\ LOW\ TH}$  and  $V_{RES\ HIGH\ TH}$  bitfields.

- If the result is below the low threshold, then PYRO\_LOW\_RES = 1

- If the result is above the high threshold, then PYRO\_HIGH\_RES = 1.

Formula for the equivalent load resistance pre-deployment:

$$R_{MEAS\_PRE\_DEP} = \frac{0.651mV^*RES\_MEAS\_PRE}{40mA} \tag{10}$$

The result of the post-deployment resistance measurement is stored in the RES\_MEAS\_POST register and it is compared with the  $V_{RES\_THR\_POST}$  threshold, selectable between 99  $\Omega$  ( $V_{RES\_THR\_POST\_SEL}$  = 0) and 49  $\Omega$  ( $V_{RES\_THR\_POST\_SEL}$  = 1).

Formula for the equivalent load resistance post-deployment:

$$R_{MEAS\_POST\_DEP} = \frac{10.69mV*RES\_MEAS\_POST}{40mA} \tag{11}$$

The active pull-down connected to the PR pin (I<sub>ACT\_PD\_PR</sub>) is automatically disabled during this check.

The error associated with the resistance measurement is ±8 % (ERR<sub>TOT\_PRM</sub>) for both the pre-deployment and post-deployment measurements.

AN6194 - Rev 2 page 16/34

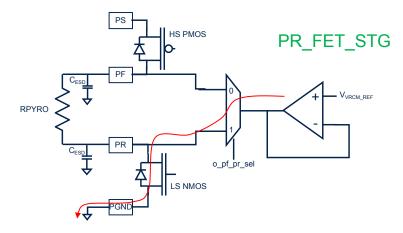

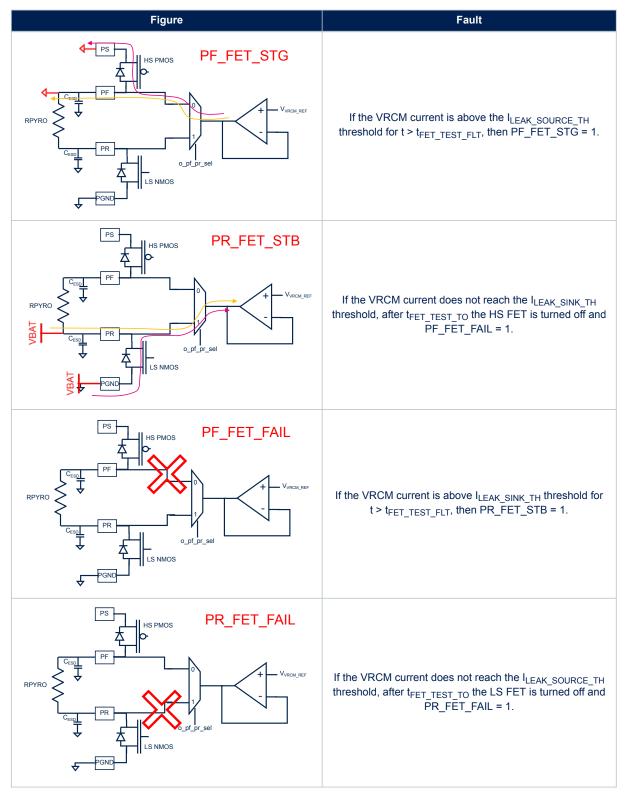

### 5.1.6 Pyro deployment FETs test

The pyro deployment FETs test checks the integrity of the power MOSFETs.  $\label{eq:mosFETs} % \begin{subarray}{ll} \end{subarray} \begi$

It works in two steps:

1. The VRCM is connected to the PF pin and the HS pMOS is turned-on. If all works correctly, then PF\_FET\_STB = 1.

PF\_FET\_STB

RPYRO

PF\_FET\_STB

VVRCM\_REF

LS NMOS

Figure 13. HS FET test

2. The VRCM is connected to the PR pin and the LS nMOS is turned-on. If all works correctly, then PR\_FET\_STG = 1.

Figure 14. LS FET test

The active pull-down connected to the PR pin ( $I_{ACT\_PD\_PR}$ ) is automatically disabled during this check. The Table 5 summarizes the possible faults.

AN6194 - Rev 2 page 17/34

Table 5. FETs test faults

AN6194 - Rev 2 page 18/34

#### 5.1.7 ER capacitor diagnostic

The ER capacitor diagnostic measures the capacitance and the ESR of the ER capacitor.

The value of capacitance is stored in ERCAP\_DIAG\_CAP\_READ\_0 (LSB) and ERCAP\_DIAG\_CAP\_READ\_1 (MSB) registers, instead the value of ESR is stored in ERCAP\_DIAG\_ESR\_READ\_0 (LSB) and ERCAP\_DIAG\_ESR\_READ\_1 (MSB) registers.

The formula to convert the CAP\_VALUE code in the capacitance value is the following:

$$C[\mu F] = \frac{(CAP\_VALUE\_MSB\&CAP\_VALUE\_LSB)_{dec}*LSB_C}{R_{ERDCHSW}}$$

(12)

$$Example: C = \frac{(0x180x23E)_{dec}*25.35\mu F*\Omega}{68\Omega} = 595.725\mu F$$

If the measured value stored in CAP\_VALUE is lower than the threshold set in ERCAP\_C\_THR, the ERCAP\_LOW\_C fault flag is set in the ERCAP register.

The formula to convert the ESR\_VALUE code in the ESR value is the following:

$$ESR[m\Omega] = (ESR\_VALUE\_MSB \& ESR\_VALUE\_LSB)_{dec} * \frac{LSB_{ESR} * R_{ERDCHSW}}{1000}$$

(13)

Example:

$$ESR = (0x4\&0x19)_{dec} * \frac{38.52\mu*68\Omega}{1000} = 49.768m\Omega$$

If the measured value in ESR\_VALUE is higher than the threshold set in ERCAP\_ESR\_THR bit field, the ERCAP\_HIGH\_ESR fault flag is set in the ERCAP register.

- The accuracy of capacitance measurement is ±15 %.

- The accuracy of ESR measurement is ±50 mΩ.

AN6194 - Rev 2 page 19/34

## 5.2 On-demand diagnostics

The diagnostics can be requested on-demand using the DIAG\_CMD register: there is a bit to enable each diagnostic (see Table 6), then the diagnostics start when the DIAG\_START bit is written to "1".

Table 6. On-demand diagnostic bits

| Diagnostic                                      | Enable bit     |

|-------------------------------------------------|----------------|

| Analog built-in self-test                       | ABIST          |

| Analog-to-digital converter hardware self-check | ADC_HWSC       |

| VRCM check and pyro output leakage test         | VRCM_LEAK_TEST |

| Pyro igniter resistance measurement             | PYRO_RES       |

| Pyro deployment FETs test                       | FET_TEST       |

| ER capacitor diagnostic                         | ER_CAP         |

If the on-demand diagnostic is running, then SPI\_DIAG\_RUNNING = 1. When the on-demand diagnostic is completed, then SPI\_DIAG\_END = 1.

If needed, the active pull-down connected to PR pin (I<sub>ACT\_PD\_PR</sub>) can be disabled by setting PR\_PD\_DIS = 1.

## 5.3 Cyclic diagnostics

The diagnostics can be run cyclically by setting the proper bitfields in thr NVM (see Table 7).

Table 7. Cyclic diagnostic configuration

| Diagnostic                             | Enable bit  | Periodicity bit field |

|----------------------------------------|-------------|-----------------------|

| ADC hardware self-check                | ADC_HWSC_EN | ADC_HWSC_NCYCLE       |

| VRCM check and pro output leakage test | LEAK_EN     | LEAK_NCYCLE           |

| Pyro igniter resistance measurement    | PYRO_RES_EN | PYRO_RES_NCYCLE       |

| Pyro deployment FETs test              | FET_EN      | FET_NCYCLE            |

| ER capacitor diagnostic                | ER_CAP_EN   | ER_CAP_NCYCLE         |

The period of a cyclic diagnostic routine is set by DIAG\_ROUTINE\_PERIOD bit field (between 100 ms, 300 ms, 500 ms and 700 ms).

When NCYCLE bitfield is different from 1, the diagnostic is executed with the periodicity set by the bitfield itself. For example, if NCYCLE = 4, the diagnostic runs at the fourth cycle.

If the cyclic diagnostic is running, then CYC\_DIAG\_RUNNING = 1. The number of cycles is reported in the CYC\_DIAG\_NCYCLE bitfield.

If needed, the active pull-down connected to the PR pin ( $I_{ACT\ PD\ PR}$ ) can be disabled by setting PR\_PD\_DIS = 1.

AN6194 - Rev 2 page 20/34

#### **Diagnostics routine sequence** 5.4

The routine sequence followed by diagnostics both in on-demand diagnostic and in cyclic diagnostic is shown in Figure 15.

3 5 1.25GS/s 5M points

1=ERBST, 2=PF

Figure 15. Diagnostics routine sequence

- 1. VRCM STB test:

- a. VRCM connected to PF

- b. I<sub>PF\_PU</sub> turned on

c. VRCM disconnected from PF

- 2. VRCM STB test:

- VRCM connected to PR

- b. I<sub>PF\_PU</sub> turned off

c. I<sub>PR\_PD</sub> turned on

3. LS leakage test:

- a. VRCM just connected to PR

b. I<sub>PR\_PD</sub> turned off

4. LS FET test:

- - a. VRCM just connected to PR

b. LS FET turned on fort<sub>FET\_TEST\_FLT</sub>

- HS leakage test:

- a. VRCM connected to PF

- HS FET test:

a. VRCM just connected to PF

- b. HS FET turned on fort<sub>FET\_TEST\_FLT</sub>

- 7. Resistance measurement:

a. VRCM disconnected from PF

- b. I<sub>PF\_PU</sub> turned on

c. I<sub>PR\_PD</sub> turned on

5.5 **Diagnostics check**

The status bits of diagnostics are summarized in Table 8.

Table 8. Diagnostics check

| Diagnostic   | Status bit           | Register             | Description                            |

|--------------|----------------------|----------------------|----------------------------------------|

| ABIST        | ABIST_FAIL           | INTERNAL_STATUS      | Fail of ABIST                          |

|              | PF_PR_PRE_HWSC_FAIL  | DEPLOY_DIAG_STATUS_1 | Fail of PF-PR pre-deployment ADC HWSC  |

| ADC HWSC     | PF_PR_POST_HWSC_FAIL | DEPLOY_DIAG_STATUS_1 | Fail of PF-PR post-deployment ADC HWSC |

|              | VRCM_HWSC_FAIL       | DEPLOY_DIAG_STATUS_1 | Fail of VRCM ADC HWSC                  |

| VRCM check   | VRCM_STB_FAIL        | DEPLOY_DIAG_STATUS_0 | Fail of STB check                      |

| VRCIVI CHECK | VRCM_STG_FAIL        | DEPLOY_DIAG_STATUS_0 | Fail of STG check                      |

|              | PF_STG               | DEPLOY_DIAG_STATUS_0 | PF leakage vs ground                   |

| Lookaga Toot | PF_STB               | DEPLOY_DIAG_STATUS_0 | PF leakage vs battery                  |

| Leakage Test | PR_STG               | DEPLOY_DIAG_STATUS_0 | PR leakage vs ground                   |

|              | PR_STB               | DEPLOY_DIAG_STATUS_0 | PR leakage vs battery                  |

| Res Meas     | PYRO_LOW_RES         | DEPLOY_DIAG_STATUS_1 | Low resistance value                   |

| Res ivieas   | PYRO_HIGH_RES        | DEPLOY_DIAG_STATUS_1 | High resistance value                  |

|              | PF_FET_STG           | DEPLOY_DIAG_STATUS_0 | HS FET shorted to ground               |

| FETs Test    | PF_FET_FAIL          | DEPLOY_DIAG_STATUS_0 | HS FET test fail (timeout)             |

| FE IS TEST   | PR_FET_STB           | DEPLOY_DIAG_STATUS_0 | LS FET shorted to battery              |

|              | PR_FET_FAIL          | DEPLOY_DIAG_STATUS_0 | LS FET test fail (timeout)             |

|              | ECAP_LOW_C           | ERCAP                | Low capacitance                        |

| ER Can Diag  | ERCAP_HIGH_ESR       | ERCAP                | High ESR                               |

| ER Cap Diag  | ERCAP_OUT_OF_RANGE   | ERCAP                | Cap or ESR out of range                |

|              | ERCAP_DIAG_END_TO    | ERCAP                | ER cap diag fail (timeout)             |

AN6194 - Rev 2 page 21/34

#### 5.6 FAULTN check

The FAULTN line shall be checked for safety reasons, and it can be done:

- Automatically:

- In low-power mode, at each CWUP low-to-high transition, the IC generates a pulse.

- In full-power mode, setting FAULTN\_CYCLIC\_PULSE = 1, the IC generates a pulse every tFAULT PERIOD.

- On-demand using FAULTN\_FORCE bit: FAULTN\_FORCE = 1 forces FAULTN low.

The MCU shall monitor the coherence between the FAULTN pin and its echo bit (FAULTN\_ECHO) in GSW of SPI. The FAULTN output can be disabled by setting **FAULTN DIS** = 1.

### 5.7 On-demand ADC request

When not used in diagnostics, the ADC can be used to measure main voltages on-demand.

According to the AMUX\_CONF setting, the following analog-to-digital voltage conversions can be requested from the IC: PS, PF, PR, PF-PR (pre-deployment), PF-PR (post-deployment), ERBST and VRCM.

To start the conversion process, the user shall set ADC\_CONV\_CMD = 1.

During the conversion, the IC sets ADC\_BUSY = 1 and then, once finished, ADC\_CONV\_RDY = 1.

The result is stored in the ADC\_CONVERSION bitfield of the ADC\_CONV\_RESULT register.

Based on the voltage conversion required, the input range and the related LSB change, three formulas are available:

1. Formula for PF-PR pre-deployment measurement:

$$V_{MEAS} = 0.651 mV^* (ADC_CONVERSION)_{dec}$$

(14)

2. Formula for PF-PR post-deployment and VRCM measurements:

$$V_{MEAS} = 10.69 mV^* (ADC_CONVERSION)_{dec}$$

(15)

3. Formula for PS, PF, PR and ERBST measurements:

$$V_{MEAS} = 55.27 mV^* (ADC_CONVERSION)_{dec}$$

(16)

The ADC result is affected by error gain (max ±2 %) and by offset (max ±5 LSB).

AN6194 - Rev 2 page 22/34

## 6 Deployment

### 6.1 Deployment via FENH and FENL

The FENx decoders shall be enabled in the NVM by setting FENL EN = 1 and FENH EN = 1.

The deployment can be triggered in two ways based on the FENx\_MODE bit selection:

- FENL\_MODE = FENH\_MODE = 0: level mode

Example: with FENL\_LEVEL = 0 and FENH\_LEVEL = 1, a low signal on FENL and a high signal on FENH

trigger the deployment.

- 2. FENL\_MODE = FENH\_MODE = 1: PWM mode

Example: **FENL\_LEVEL** = 0 and **FENH\_LEVEL** = 1, a PWM signal with 25 % duty cycle on FENL and a PWM signal with a 75 % duty cycle on FENH trigger the deployment.

FENL\_FREQ = FENH\_FREQ = 1 sets the PWM frequency to 16 kHz.

If FENx MODE = 0 (level mode):

- FENL\_PU\_PD and FENH\_PU\_PD bits shall be set accordingly

- FENX\_DEGLITCH sets the deglitch filter on FENH and FENL signals

- FENL\_INT\_CHECK\_EN = 1 and FENH\_INT\_CHECK\_EN = 1 enables the integrity check on FENL and FENH pins respectively.

Two cases are possible:

- CWUP always high (full-power mode).

Every t<sub>FAULTN\_PERIOD</sub> the IC generates a t<sub>FAULTN\_PULSE</sub> pulse on FAULTN pin and waits for a pulse on FENL and FENH pins before t<sub>FENX\_PERIOD</sub> expires.

- 2. Cyclic CWUP (low-power mode).

At each CWUP rising edge, the IC generates a  $t_{\text{FAULTN\_PULSE}}$  pulse on FAULTN pin and waits for a pulse on FENL and FENH pins before  $t_{\text{FENX\_PERIOD}}$  expires.

The FENX\_DLY\_CFG bitfield sets the delay between trigger signal and deployment start (no delay, 2 ms, 4 ms or 8 ms)

If FENx\_MODE = 1 (PWM mode):

- FENX\_FAULT\_PERIOD bitfield sets the number of filtered PWM pulses on FENH and FENL signals

- The integrity check on FENL and FENH in PWM mode is automatically enabled: the PWM signal is continuously monitored by an internal timer that measures the time between two rising edges, checking frequency and duty cycle.

When the integrity check is working, a fault is reported in the FENX\_INTEGRITY\_STATUS register:

- FENH\_HIGH\_FREQ and/or FENL\_HIGH\_FREQ if high-frequency error is detected

- FENH LOW FREQ and/or FENL LOW FREQ if low-frequency error is detected

- FENH PWM TIMEOUT and/or FENL PWM TIMEOUT if PWM timeout error is detected

- FENH LEV TIMEOUT and/or FENL LEV TIMEOUT if level timeout error is detected.

FENH\_ECHO and FENL\_ECHO are an echo of FENH and FENL pins respectively.

AN6194 - Rev 2 page 23/34

## 6.2 Deployment via SPI

The deployment can be triggered via the SPI by writing the proper code in the HS\_CMD and LS\_CMD registers:

- 0x155 in HS\_CMD register

- 0x2AA in LS\_CMD register.

## 6.3 Deployment status

In the DEPLOY STATUS register, it is possible to check the information reported in Table 9:

Table 9. Deployment status bits

| Bit field         | Description                                      |

|-------------------|--------------------------------------------------|

| FIRE_INHIBIT      | The status of the fire inhibit signal            |

| DEPLOY_CNT        | The number of performed deployments              |

| FIRE_RUNNING      | The status of deployment on-going                |

| FIRE_GOOD         | The status of right deployment sequence complete |

| FIRE_END_BY_FAULT | Deployment interrupted due to a fault            |

| FIRE_END          | End of deployment sequence                       |

| FENL_ARM          | FENL ARM condition                               |

| FENH_ARM          | FENH ARM condition                               |

The value of time during which the deployment current is above the threshold set in DEP\_MON\_THR bitfield is stored in the DEP\_CURR\_MON bitfield of the DEPLOY\_CURRENT\_MONITOR register.

The relationship between the deployment current monitor and the DEP\_CURR\_MON code is the following:

$$t_{DEP\_MON\_TH} = (DEP\_CURR\_MON)_{dec} * t_{DEP\_CUR\_MON}$$

$$Example: t_{DEP\_MON\_TH} = (0x5D)_{dec} * 8\mu s = 744\mu s$$

(17)

AN6194 - Rev 2 page 24/34

# 7 Layout suggestions

Referring to the schematic in Figure 16, some layout suggestions are presented in this chapter.

Figure 16. Reference schematic

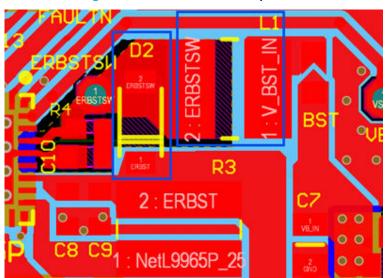

## 7.1 ERBST

Boost components (inductor L1 and diode D1) should be placed as near as possible to the IC to maximize efficiency (the fewer parasitic components, the smaller the loss) and reduce EMI, as shown in Figure 17. If needed, a snubber circuit (R4, C10) tie to the BSTGND can be added.

Figure 17. ERBST external components

AN6194 - Rev 2 page 25/34

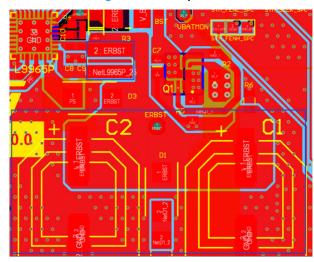

## 7.2 ER capacitor

Components involved in the ER capacitor diagnostic (capacitors C1 and C2, and resistor R3) should be placed as near as possible to the IC to minimize parasitics that can degrade the measurement of capacitance and ESR, as shown in Figure 18.

Note: Two capacitors for safety, to cover the fault case in which one cap will open.

Figure 18. ER capacitor

## 7.3 Deployment stage

ER capacitors (C1 and C2) should be placed near the PS pin in order to supply the deployment stage while minimizing parasitic components, as shown in Figure 19 (left). If necessary, can be added D3 as back feeding protection from the PS pin.

PF and PR traces shall be sized to sustain the desired deployment current profile. The IC is designed taking in consideration parasitics due to long wires.

C11 and C12 (typ. value 22 nF) shall be placed to protect both SF and SR pins from ESD spikes as shown in Figure 19 (right).

To improve EMC performance, it is suggested to place 100 pF + 1 nF near the IC pins, 100 nF near the pyrofuse connector.

Figure 19. Deployment stage

AN6194 - Rev 2 page 26/34

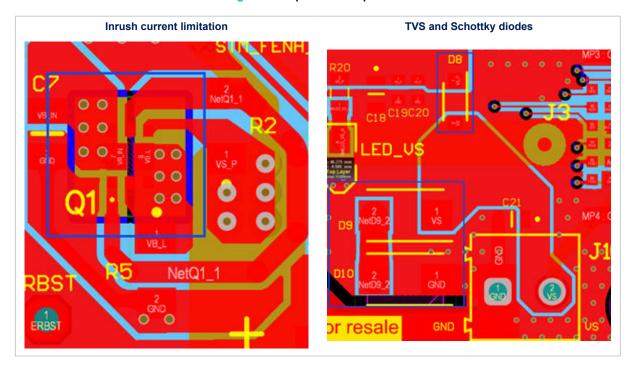

## 7.4 Optional components

The Q1 integrated circuit is used to limit the initial inrush current from VIN to the ER capacitors, in combination with resistors R2 and R5. To improve thermal performance, add an exposed pad on the bottom

The TVS diodes (D9 and D10) on VIN can be used to protect the device when spikes may exceed the AMR. The Schottky diode D8 may be added to add reverse battery protection.

Figure 20. Optional components

The battery filter stage (C18, C19, C20) and the input capacitor (C21) should be placed close to the input connector to filter noise from the battery and to avoid coupling around in the PCB (refer to Figure 21).

Filter stage

Supply input

The stage of th

Figure 21. Filter stage

AN6194 - Rev 2 page 27/34

## 7.5 PCB suggestions

The reference design is done on a 4-layer PCB in 2s2p configuration, with GND and Power (VS) as external layers (TOP and BOTTOM). All GND planes should be tied together using an adequate number of vias (as much as possible). Reserve inner layers for sensing and communication lines.

To improve EMC robustness:

- Place all ERBST components as close as possible to the IC, minimizing parasitic effects. The PBC area under the boost coil should be free of metal layers/metal strips.

- Place protection components as close as possible to the relevant external connector: TVS diode, input filter stage, and ESD capacitors.

AN6194 - Rev 2 page 28/34

## **Revision history**

Table 10. Document revision history

| Date        | Revision | Changes                                                                                                                                    |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 01-Oct-2025 | 1        | Initial release.                                                                                                                           |

| 05-Dec-2025 | 2        | Added L99BM2P and L99BM2C part numbers.  Updated Section 1, Section 2 and all sub-sections, Section 3.8.1, Section 7 and all sub-sections. |

|             |          | Added Section 5.1.7.                                                                                                                       |

AN6194 - Rev 2 page 29/34

## **Contents**

| 1 Application scenarios |                      |                                      |                                                    |    |  |  |  |  |

|-------------------------|----------------------|--------------------------------------|----------------------------------------------------|----|--|--|--|--|

| 2                       | Exte                 | ernal co                             | mponents sizing                                    | 4  |  |  |  |  |

|                         | 2.1                  | ERBS                                 | T components                                       | 4  |  |  |  |  |

|                         | 2.2                  | Energ                                | y reserve capacitor                                | 5  |  |  |  |  |

|                         | 2.3                  | Batter                               | y filter                                           | 5  |  |  |  |  |

|                         | 2.4                  | Powe                                 | er stage filter                                    | 6  |  |  |  |  |

| 3                       | Device configuration |                                      |                                                    |    |  |  |  |  |

|                         | 3.1                  | NVM configuration (write command)    |                                                    |    |  |  |  |  |

|                         | 3.2                  | ERBS                                 | T configuration                                    | 7  |  |  |  |  |

|                         | 3.3                  | Load thresholds configuration        |                                                    |    |  |  |  |  |

|                         | 3.4                  | Energy reserve capacitor diagnostic7 |                                                    |    |  |  |  |  |

|                         | 3.5                  |                                      | yment configuration                                |    |  |  |  |  |

|                         | 3.6                  | FAUL1                                | ·<br>ΓN pin masking                                | 9  |  |  |  |  |

|                         | 3.7                  | Deploy                               | yment inhibition masking                           | 9  |  |  |  |  |

|                         | 3.8                  | Device                               | e configuration example                            | 10 |  |  |  |  |

|                         |                      | 3.8.1                                | Example of non-volatile memory (NVM) configuration | 10 |  |  |  |  |

|                         |                      | 3.8.2                                | Example of volatile memory configuration           | 12 |  |  |  |  |

| 4                       | Dev                  | ice che                              | ck                                                 |    |  |  |  |  |

| 5                       | Diag                 | nostics                              | S                                                  |    |  |  |  |  |

|                         | 5.1                  |                                      | ble diagnostics                                    |    |  |  |  |  |

|                         |                      | 5.1.1                                | ABIST                                              | 14 |  |  |  |  |

|                         |                      | 5.1.2                                | Hardware self-check (HSWC)                         | 14 |  |  |  |  |

|                         |                      | 5.1.3                                | Voltage regulator current monitor (VRCM) check     | 14 |  |  |  |  |

|                         |                      | 5.1.4                                | Pyro outputs leakage test                          | 15 |  |  |  |  |

|                         |                      | 5.1.5                                | Pyro igniter resistance measurement                | 16 |  |  |  |  |

|                         |                      | 5.1.6                                | Pyro deployment FETs test                          | 17 |  |  |  |  |

|                         |                      | 5.1.7                                | ER capacitor diagnostic                            | 19 |  |  |  |  |

|                         | 5.2                  | On-demand diagnostics                |                                                    |    |  |  |  |  |

|                         | 5.3                  | Cyclic diagnostics                   |                                                    |    |  |  |  |  |

|                         | 5.4                  | Diagnostics routine sequence         |                                                    |    |  |  |  |  |

|                         | 5.5                  | Diagnostics check                    |                                                    |    |  |  |  |  |

|                         | 5.6                  | FAULTN check                         |                                                    |    |  |  |  |  |

|                         | 5.7                  | On-de                                | emand ADC request                                  |    |  |  |  |  |

|                         |                      |                                      | t                                                  |    |  |  |  |  |

|     | 6.1   | Deployment via FENH and FENL | 23 |

|-----|-------|------------------------------|----|

|     | 6.2   | Deployment via SPI           | 24 |

|     | 6.3   | Deployment status            | 24 |

| 7   | Layo  | out suggestions              | 25 |

|     | 7.1   | ERBST                        | 25 |

|     | 7.2   | ER capacitor                 | 26 |

|     | 7.3   | Deployment stage             | 26 |

|     | 7.4   | Optional components          | 27 |

|     | 7.5   | PCB suggestions              | 28 |

| Roy | ision | history                      | 29 |

## **List of tables**

| Table 1.  | FAULTN pin masking summary            | 9 |

|-----------|---------------------------------------|---|

|           | Deployment inhibition masking summary |   |

| Table 3.  | NVM configuration example             | 0 |

| Table 4.  | VM configuration example              | 2 |

| Table 5.  | FETs test faults                      | 8 |

| Table 6.  | On-demand diagnostic bits             | 0 |

| Table 7.  | Cyclic diagnostic configuration       | 0 |

| Table 8.  | Diagnostics check                     | 1 |

| Table 9.  | Deployment status bits                | 4 |

| Table 10. | Document revision history             | 9 |

# **List of figures**

| Figure 1.  | Application circuit with battery supply     | . 2 |

|------------|---------------------------------------------|-----|

| Figure 2.  | Application circuit with DC-DC converter    | . 3 |

| Figure 3.  | Application circuit without boost converter | . 3 |

| Figure 4.  | Inrush current limit                        | . 4 |

| Figure 5.  | FIRE_GOOD signal selection                  | . 8 |

| Figure 6.  | VRCM check: sink current                    | 14  |

| Figure 7.  | VRCM check: source current                  | 14  |

| Figure 8.  | PF short to battery (PF STB)                | 15  |

| Figure 9.  | PF short to ground (PF STG)                 | 15  |

| Figure 10. | PR short to battery (PR STB)                | 15  |

| Figure 11. | PR short to ground (PR STG)                 | 15  |

| Figure 12. | Load resistance measurement                 | 16  |

| Figure 13. | HS FET test                                 | 17  |

| Figure 14. | LS FET test                                 | 17  |

| Figure 15. | Diagnostics routine sequence                | 21  |

| Figure 16. | Reference schematic                         | 25  |

| Figure 17. | ERBST external components                   | 25  |

| Figure 18. | ER capacitor                                | 26  |

| Figure 19. | Deployment stage                            | 26  |

| Figure 20. | Optional components                         | 27  |

| Figure 21. | Filter stage                                | 27  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice.

In the event of any conflict between the provisions of this document and the provisions of any contractual arrangement in force between the purchasers and ST, the provisions of such contractual arrangement shall prevail.

The purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

The purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of the purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

If the purchasers identify an ST product that meets their functional and performance requirements but that is not designated for the purchasers' market segment, the purchasers shall contact ST for more information.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics - All rights reserved

AN6194 - Rev 2 page 34/34