# Migrating from the STM32WBA5xxx to the STM32WBA6xxx MCUs

#### Introduction

The designers of STM32 microcontroller applications must have the possibility to replace one microcontroller type easily by another from the same product family or by products from a different family. The reasons for migrating an application to a different microcontroller can be for example:

- To meet higher product requirements, extra demands on memory size, or an increased number of I/Os.

- To meet cost reduction constraints that require switching to smaller components and shrink the PCB area.

This application note details the steps required to migrate from a design based on an STM32WBA5xxx device to an application based on one of the STM32WBA6xxx MCUs.

This document provides guidelines for hardware and peripheral migration. To understand the information inside this application note better, the user must be familiar with the STM32 microcontroller family.

For additional information, refer to the product datasheets and reference manuals available on www.st.com.

#### Reference documents

This application note must be read with the following documents:

| [1] | STM32WBA6xxx reference manual (RM0515)                                         |

|-----|--------------------------------------------------------------------------------|

| [2] | STM32WBA6xxx datasheet (DS14736)                                               |

| [3] | STM32WBA5xxx datasheet (DS14127)                                               |

| [4] | STM32 microcontroller system memory boot mode (AN2606)                         |

| [5] | STM32 Cortex <sup>®</sup> -M33 MCUs programming manual (PM0264)                |

| [6] | Cortex®-M33 processor technical reference manual, available on the Arm website |

## 1 STM32WBA6xxx MCUs

The STM32WBA6xxx devices are ultra-low-power and wireless MCUs with enhanced efficiency, performance, and memory size as follows:

Up to 2 Mbytes of dual-bank flash memory with ECC accelerated by instruction/data caches and up to 512 Kbytes of embedded SRAM with optional parity.

These devices reuse the same embedded 32-bit Arm<sup>®</sup> Cortex<sup>®</sup>-M33 core as the STM32WBA5xxx devices. This core runs at 100 MHz for both devices. It provides improved security features due to the presence of the ultra-low-power Arm<sup>®</sup> TrustZone<sup>®</sup> for Armv8-M.

Note:

The Arm word and logo are trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. All rights reserved.

Arm and TrustZone are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

The STM32WBA6xxx devices includes a larger set of peripherals with more advanced features compared to the STM32WBA5xxx devices. These features include:

- Power consumption:

- New low-power Stop 2 mode.

- Interfaces:

- Voltage reference buffer for ADC: VREFBUF<sup>(1)</sup>

- Additional GPIOs and secondary V<sub>DDIO2</sub> supply

- Additional touch sense channels: TSC

- Improved random number generator: RNG

- Additional 32-bit general-purpose timer: TIM4

- Two additional I<sup>2</sup>C interfaces: I2C2<sup>(2)</sup> and I2C4<sup>(2)</sup>

- One additional SPI: SPI2<sup>(2)</sup>

- One additional USART: USART3<sup>(2)</sup>

- Support for debug: ETM<sup>(1)</sup>

- USB on-the-go high-speed (OTG) peripheral with embedded PHY and OTG 2.0 full-speed controller

- 1. Feature only available on the STM32WBA62/65 devices.

- 2. Feature only available on the STM32WBA62/64/65 devices.

Both the STM32WBA5xxx and STM32WBA6xxx MCUs embed high-speed memories and an extensive range of enhanced I/Os.

Table 1. Overview of the STM32WBA5xxx and STM32WBA6xxx

| Package              | Memory size  |            | Device       |              |  |

|----------------------|--------------|------------|--------------|--------------|--|

| rackaye              | Flash memory | SRAM       | STM32WBA5xxx | STM32WBA6xxx |  |

|                      | 1 Mbyte      | 120 Khyton | STM32WBA52KG |              |  |

| LICOEDNISS           | 1 Mbyte      | 128 Kbytes | STM32WBA54KG | N/A          |  |

| UFQFPN32             | 512 Kbytes   | 06 Khytoo  | STM32WBA52KE | N/A          |  |

|                      | 512 Kbytes   | 96 Kbytes  | STM32WBA54KE |              |  |

| Thin WLCSP41 SMPS    | 1 Mbyte      | 128 Kbytes | STM32WBA55HG | N/A          |  |

| TIIII WLCSF41 SIVIFS | 512 Kbytes   | 96 Kbytes  | STM32WBA55HE | N/A          |  |

|                      | 1 Mbyte      | 128 Kbytes | STM32WBA52CG |              |  |

| UFQFPN48             | 1 Mbyte      | 120 Kbytes | STM32WBA54CG | N/A          |  |

|                      | 512 Kbytes   | 96 Kbytes  | STM32WBA52CE |              |  |

AN6159 - Rev 1 page 2/57

| Dankana              | Memory       | size       | Device       |                            |  |

|----------------------|--------------|------------|--------------|----------------------------|--|

| Package              | Flash memory | SRAM       | STM32WBA5xxx | STM32WBA6xxx               |  |

| UFQFPN48             | 512 Kbytes   | 96 Kbytes  | STM32WBA54CE | N/A                        |  |

|                      | 2 Mbytes     | 512 Kbytes | N/A          | STM32WBA63CI               |  |

| LIEGERNAG GMDG       | 4.845.45     | 256 Kbytes | N/A          | STM32WBA63CG               |  |

| UFQFPN48 SMPS        | 1 Mbyte      | 128 Kbytes | STM32WBA55CG | N/A                        |  |

|                      | 512 Kbytes   | 96 Kbytes  | STM32WBA55CE | - N/A                      |  |

| LIEOEDNAO LIOD       | 2 Mbytes     | 512 Kbytes | N/A          | STM32WBA64CI, STM32WBA62CI |  |

| UFQFPN48 USB         | 1 Mbyte      | 256 Kbytes | N/A          | STM32WBA64CG, STM32WBA62CG |  |

| LIFOEDNIAG OMDO LIOD | 2 Mbytes     | 512 Kbytes | N/A          | STM32WBA65CI               |  |

| UFQFPN48 SMPS USB    | 1 Mbyte      | 256 Kbytes | N/A          | STM32WBA65CG               |  |

| LIEDOAEO OMBO        | 1 Mbyte      | 128 Kbytes | STM32WBA55UG | N/A                        |  |

| UFBGA59 SMPS         | 512 Kbytes   | 96 Kbytes  | STM32WBA55UE | - N/A                      |  |

| VECEDNO CMDC HCD     | 2 Mbytes     | 512 Kbytes | N/A          | STM32WBA65RI               |  |

| VFQFPN68 SMPS USB    | 1 Mbyte      | 256 Kbytes | N/A          | STM32WBA65RG               |  |

| Thin WLCSP88         | 2 Mbytes     | 512 Kbytes | N/A          | STM32WBA62MI               |  |

| Thin WLCSP88         | 1 Mbyte      | 256 Kbytes | N/A          | STM32WBA62MG               |  |

| This IAN CODES CARDS | 2 Mbytes     | 512 Kbytes | N/A          | STM32WBA65MI               |  |

| Thin WLCSP88 SMPS    | 1 Mbyte      | 256 Kbytes | N/A          | STM32WBA65MG               |  |

| LIEDCA404            | 2 Mbytes     | 512 Kbytes | N/A          | STM32WBA62PI               |  |

| UFBGA121             | 1 Mbyte      | 256 Kbytes | N/A          | STM32WBA62PG               |  |

| UFBGA121 SMPS        | 2 Mbytes     | 512 Kbytes | N/A          | STM32WBA65PI               |  |

| UFBGATZT SIVIPS      | 1 Mbyte      | 256 Kbytes | N/A          | STM32WBA65PG               |  |

# 1.1 Memory availability

The STM32WBA6xxx MCUs embed more memory than the STM32WBA5xxx as shown in the table below.

Table 2. Memory size on the STM32WBA5xxx and STM32WBA6xxx

| Product      | Flash memory   |        | SRAM1            | SRAM2     |  |

|--------------|----------------|--------|------------------|-----------|--|

| Floudet      | Size           | Bank   | SKAWII           | SKAWIZ    |  |

| STM32WBA6xxx | Up to 2 Mbytes | Dual   | Up to 448 Kbytes | 64 Khyton |  |

| STM32WBA5xxx | Up to 1 Mbyte  | Single | Up to 64 Kbytes  | 64 Kbytes |  |

# 1.2 System architecture differences between the STM32WBA5xxx and STM32WBA6xxx MCUs

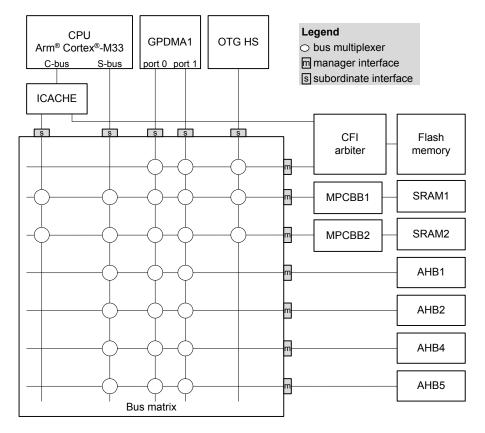

Both the STM32WBA5xxx and STM32WBA6xxx MCUs embed:

- High-speed memories

- An extensive range of enhanced I/Os and peripherals connected to:

- APB buses

- AHB buses

- A 32-bit multi-AHB bus matrix

The bus matrix provides access from a manager to a subordinate, enabling concurrent access and efficient operation when several high-speed peripherals work simultaneously.

AN6159 - Rev 1 page 3/57

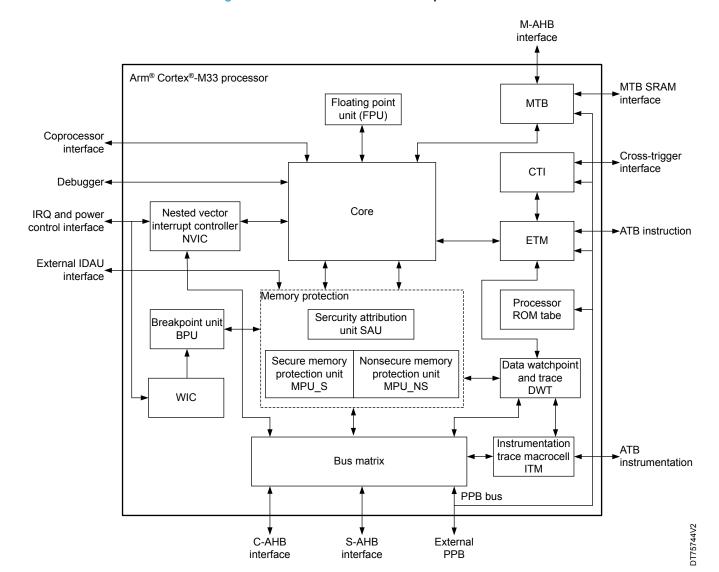

In addition, the STM32WBA6xxx MCUs connect more managers to the bus matrix than the STM32WBA5xxx. The STM32WBA6xxx MCUs also embed more peripherals on internal buses.

The figures below detail the system architectures of the STM32WBA5xxx and STM32WBA6xxx MCUs.

CPU Legend GPDMA1 Arm® Cortex®-M33 bus multiplexer S-bus port 0 port 1 m manager interface s subordinate interface **ICACHE** S S CFI Flash arbiter memory MPCBB1 SRAM1 MPCBB2 SRAM2 AHB1 AHB2 AHB4 AHB5 Bus matrix

Figure 1. STM32WBA5xxx system architecture

F75742V1

page 4/57

Figure 2. STM32WBA6xxx system architecture

DT75743V1

# 2 Migrating the hardware

The STM32WBA6xxx MCUs offer:

- Several 48-pin packages with three versions of pinout:

- Without an internal switched-mode power supply (SMPS) but with OTG: the 48-pin packages differ by nine pins. This difference is due to the presence of the internal OTG.

- With an internal SMPS but without OTG: the package is then fully compatible with the 48-pin package of the STM32WBA5xxx MCUs.

- With internal SMPS and with OTG: the 48-pin packages differ by nine pins. This difference is due to the presence of the internal OTG.

- 68-pin and 121-pin packages. Not available in the STM32WBA5xxx MCUs.

Note: OTG is available only on the STM32WBA62, STM32WBA64, and STM32WBA65 devices.

The SMPS is available only on the STM32WBA63 and STM32WBA65 devices.

The table below compares the packages with no SMPS available for the STM32WBA6xxx MCUs to those available for the STM32WBA5xxx MCUs. It lists the pinout compatibility and differences between these packages.

| Table 3. Packages without SMPS on the S | STM32WBA5xxx and STM32WBA6xxx MCUs |

|-----------------------------------------|------------------------------------|

|-----------------------------------------|------------------------------------|

| Package (size in | STM32WBA6xxx versus                                               | Pinout differences (pin name) |              |                     |  |

|------------------|-------------------------------------------------------------------|-------------------------------|--------------|---------------------|--|

| mm × mm)         | STM32WBA5xxx                                                      | Pin number                    | STM32WBA5xxx | STM32WBA6xxx<br>USB |  |

|                  |                                                                   | 13                            | PA0          | VDDUSB              |  |

|                  |                                                                   | 14                            | PB9          | PD9                 |  |

|                  | Compatible with nine differences                                  | 15                            | PB8          | PD8                 |  |

|                  | on pins 13 to 21 (the other pins                                  | 16                            | PC15         | PD7                 |  |

| UFQFPN48 (7 × 7) | <ul><li>are the same)</li><li>No PA0, PB9, and PB[7:5].</li></ul> | 17                            | PC14         | PD6                 |  |

|                  | PB8 and PC[15:13] have different                                  | 18                            | PC13         | PB8                 |  |

|                  | pin positions.                                                    | 19                            | PB7          | PC15                |  |

|                  |                                                                   | 20                            | PB6          | PC14                |  |

|                  |                                                                   | 21                            | PB5          | PC13                |  |

| UFBGA121 (6 × 6) | Package not available for the STM32WBA5xxx MCUs.                  | -                             | -            | -                   |  |

<sup>1.</sup> Available only for the STM32WBA62/64 devices.

AN6159 - Rev 1 page 6/57

<sup>2.</sup> Available only for the STM32WBA62 devices.

The table below compares the packages with SMPS available for the STM32WBA6xxx MCUs to those available for the STM32WBA5xxx MCUs. It lists the pinout compatibility and differences between these packages.

Table 4. Packages with SMPS on the STM32WBA5xxx and STM32WBA6xxx MCUs

| Dookage (size in                 | STM22MD A Sway your up                                                                                                                                     | Pinout differences (pin name) |                      |                          |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|----------------------|--------------------------|--|

| Package (size in<br>mm × mm)     | STM32WBA6xxx versus<br>STM32WBA5xxx                                                                                                                        | Pin number                    | STM32WBA5xxx<br>SMPS | STM32WBA6xxx<br>SMPS USB |  |

| UFQFPN48 (7 × 7) (1) without OTG | Pin-to-pin compatible with the STM32WBA5xxx MCUs                                                                                                           | -                             | -                    | -                        |  |

|                                  |                                                                                                                                                            | 13                            | PA0                  | VDDUSB                   |  |

|                                  |                                                                                                                                                            | 14                            | PB9                  | PD9                      |  |

|                                  | Compatible with nine differences on pins 13 to 21 (the other pins are the same):  No PA0, PB9, and PB[7:5]  PB8 and PC[15:13] have different pin positions | 15                            | PB8                  | PD8                      |  |

|                                  |                                                                                                                                                            | 16                            | PC15                 | PD7                      |  |

| UFQFPN48 (7 × 7) (2) with OTG    |                                                                                                                                                            | 17                            | PC14                 | PD6                      |  |

|                                  |                                                                                                                                                            | 18                            | PC13                 | PB8                      |  |

|                                  |                                                                                                                                                            | 19                            | PB7                  | PC15                     |  |

|                                  |                                                                                                                                                            | 20                            | PB6                  | PC14                     |  |

|                                  |                                                                                                                                                            | 21                            | PB5                  | PC13                     |  |

| VFQFPN68 (8 × 8)                 | Package not available for the STM32WBA5xxx MCUs.                                                                                                           | -                             | -                    | -                        |  |

| UFBGA121 (6 × 6)                 | Package not available for the STM32WBA5xxx MCUs.                                                                                                           | -                             | -                    | -                        |  |

<sup>1.</sup> Available only for the STM32WBA63 devices.

AN6159 - Rev 1 page 7/57

<sup>2.</sup> Available only for the STM32WBA65 devices.

# 3 Boot mode compatibility

#### 3.1 Boot mode selection

For the STM32WBA5xxx and STM32WBA6xxx MCUs, the BOOT0 input pin can come from the PH3-BOOT0 pin or from an option bit, depending on the value of a user option bit to free the GPIO pad if needed.

The bootloader is located in the system memory. It is used to reprogram the flash memory by using USART, I<sup>2</sup>C, SPI, or OTG in device mode through a DFU (device firmware upgrade).

Note: OTG is only available on the STM32WBA62/64/65 devices.

The STM32WBA5xxx and STM32WBA6xxx MCUs have compatible boot modes when TrustZone<sup>®</sup> is disabled or enabled (see the tables below). Refer to [1] for more details.

Table 5. Boot modes when TrustZone® is disabled (TZEN = 0) on the STM32WBA5xxx and STM32WBA6xxx MCUs

| NBOOT0             | воото   | NSWBOOT0       | Besterne                                                            | ST-p                  | programmed defaul | t value      |

|--------------------|---------|----------------|---------------------------------------------------------------------|-----------------------|-------------------|--------------|

| FLASH_<br>OPTR[27] | pin PH3 | FLASH_OPTR[26] | Boot area                                                           | Area                  | STM32WBA5xxx      | STM32WBA6xxx |

| -                  | 0       | 1              | Boot address defined through the user option bytes NSBOOTADD0[24:0] | User flash<br>memory: | 0x0800 0000       |              |

| -                  | 1       | 1              | Boot address defined through the user option bytes NSBOOTADD1[24:0] | Bootloader:           | 0x0BF8 8000       | 0x0BF9 0000  |

| 1                  | -       | 0              | Boot address defined through the user option bytes NSBOOTADD0[24:0] | User flash<br>memory: | 0x0800 0000       |              |

| 0                  | -       | 0              | Boot address defined through the user option bytes NSBOOTADD1[24:0] | Bootloader:           | 0x0BF8 8000       | 0x0BF9 0000  |

Table 6. Boot modes when TrustZone® is enabled (TZEN = 1)

| BOOT_<br>LOCK | nBOOT0<br>FLASH_OPTR[27] | BOOT0<br>pin PH3                                                            | nSWBOOT0<br>FLASH_OPTR[26] | RSS<br>command                   | Boot area                                                                   | ST-programmed default value      |

|---------------|--------------------------|-----------------------------------------------------------------------------|----------------------------|----------------------------------|-----------------------------------------------------------------------------|----------------------------------|

|               | -                        | Secure boot address defined through the user option bytes SECBOOTADD0[24:0] |                            | User flash memory:<br>0x0C000000 |                                                                             |                                  |

|               | -                        | 1                                                                           | 1                          | 0                                | RSS:                                                                        | 0x0BF80000                       |

| 0             | 1                        | -                                                                           | 0                          | 0                                | Secure boot address defined through the user option bytes SECBOOTADD0[24:0] | User flash memory:<br>0x0C000000 |

|               | 0                        | -                                                                           | 0                          | 0                                | RSS:                                                                        | 0x0BF80000                       |

|               | -                        | -                                                                           | -                          | ≠0                               | N33.                                                                        | 0X0BI 80000                      |

| 1             | -                        | -                                                                           | -                          | -                                | Secure boot address defined through the user option bytes SECBOOTADD0[24:0] | User flash memory:<br>0x0C000000 |

AN6159 - Rev 1 page 8/57

## 3.2 Embedded bootloader

ST programs the embedded bootloader located in the system memory during production. This bootloader allows the user to program the flash memory, using one of the serial interfaces listed in the table below.

Table 7. Bootloader interface on the STM32WBA5xxx and STM32WBA6xxx MCUs

| Peripheral | Pin name (number) | STM32WBA5xxx  | STM32WBA6xxx |                  |  |

|------------|-------------------|---------------|--------------|------------------|--|

| Peripheral | Pin name (number) | STW32VVDA3XXX | STM32WBA63   | STM32WBA62/64/65 |  |

| OTG        | USB_DM (PD7)      | N/A           | N/A          | X                |  |

| OIG        | USB_DP (PD6)      | IN/A          | IN/A         | X                |  |

| USART1     | USART1_TX(PB12)   | X             |              | X                |  |

| USARTI     | USART1_RX(PA8)    | X             |              | X                |  |

| USART2     | USART2_TX(PA12)   | X             |              | X                |  |

| USARTZ     | USART2_RX(PA11)   | X             |              | X                |  |

| I2C1       | I2C1_SCL(PB2)     | X             | X            |                  |  |

| 1201       | I2C1_SDA (PB1)    | X             | X            |                  |  |

| I2C3       | I2C3_SCL(PA6)     | X             | X            |                  |  |

| 1203       | I2C3_SDA (PA7)    | X             |              | X                |  |

|            | SPI2_NSS (PA10)   |               |              | X                |  |

| SPI2       | SPI2_SCK (PA9)    | N/A           | N/A          | X                |  |

| SP12       | SPI2_MISO (PB0)   | IN/A          | N/A          | X                |  |

|            | SPI2_MOSI (PB14)  |               |              | X                |  |

|            | SPI3_NSS (PA5)    | X             |              | X                |  |

| SPI3       | SPI3_SCK (PA0)    | X             | X            |                  |  |

| SFIS       | SPI3_MISO (PB9)   | X             | Х            |                  |  |

|            | SPI3_MOSI (PB8)   | X             |              | X                |  |

For more details on the bootloader, refer to [4].

AN6159 - Rev 1 page 9/57

# 4 Migrating the peripherals

#### 4.1 STM32 product cross-compatibility

The STM32 microcontrollers embed a set of peripherals that can be classified into the following groups:

- Group 1: peripherals. By definition, common to all products.

Those peripherals are identical, so they have the same structure, registers, and control bits. There is no need to perform any firmware change to keep the same functionality at application level after migration. All the features and the behavior remain the same.

- Group 2: peripherals shared by all products but with only minor differences (in general to support new features).

- The migration from one product to another is very easy and does not need any significant new development effort.

- Group 3: peripherals that have considerable changes from one product to another (new architecture or new features for example).

- For this group of peripherals, the migration requires a new development at the application level.

The security architecture of the STM32WBA6xxx and STM32WBA5xxx MCUs is based on the Arm<sup>®</sup> TrustZone<sup>®</sup> technology with the Armv8-M mainline extension. Each GPIO or peripheral, DMA channel, clock configuration register, ICACHE, or small part of flash memory or SRAM can be configured as trusted or untrusted.

The innovative features of the STM32WBA6xxx MCUs include a new Stop 2 mode architecture, allowing wake-up for a reduced set of peripherals down to Stop 2 mode.

The table below summarizes the available peripherals or features in the STM32WBA5xxx and STM32WBA6xxx MCUs as well as their compatibility.

Table 8. STM32 peripheral/feature compatibility between STM32WBA5xxx and STM32WBA6xxx MCUs

| Peripheral o                       | r feature                    | STM32WBA5xxx                               | STM32WBA63                | STM32WBA65      | STM32WBA62 | STM32WBA64 |  |

|------------------------------------|------------------------------|--------------------------------------------|---------------------------|-----------------|------------|------------|--|

| Core Cortex®-M33 TZ, MPU, DFU, DSP |                              |                                            |                           |                 |            |            |  |

| Maximum CPU                        | aximum CPU frequency 100 MHz |                                            |                           |                 |            |            |  |

| Caches                             | ICACHE                       |                                            |                           | 1× ICACHE       |            |            |  |

|                                    | Power supply                 |                                            |                           | 1.71 V to 3.6 V |            |            |  |

|                                    | LDO                          |                                            |                           | Available       |            |            |  |

| PWR/regulators                     | SMPS                         | SMPS                                       | S/LDO on-the-fly selec    | tion            | N/A        | N/A        |  |

|                                    | VOS range                    |                                            |                           | Range 1         |            |            |  |

|                                    | vos range                    | Range 2                                    |                           |                 |            |            |  |

|                                    |                              | Stop 0                                     |                           |                 |            |            |  |

| Low-power                          | modes                        | Stop 1                                     |                           |                 |            |            |  |

|                                    |                              | N/A                                        | N/A Stop 2                |                 |            |            |  |

|                                    | Size                         | Up to 1 Mbyte                              |                           | Up to 2         | Mbytes     |            |  |

| Flash memory                       | Bank                         | Single-bank with<br>TrustZone <sup>®</sup> | Dual-bank with TrustZone® |                 |            |            |  |

| SRAMs                              | SRAM1                        | Up to 64 Kbytes                            |                           | Up to 44        | 8 Kbytes   |            |  |

| SKAIVIS                            | SRAM2                        | M2 64 Kbytes with parity                   |                           |                 |            |            |  |

| DMA                                | 4                            | GPDMA (8 channels each)                    |                           |                 |            |            |  |

| PLL                                |                              | PLL (main)                                 |                           |                 |            |            |  |

| PLL                                |                              | N/A                                        |                           |                 |            |            |  |

AN6159 - Rev 1 page 10/57

| ### Canal Trust Stane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Peripheral o  | r feature        | STM32WBA5xxx                                                 | STM32WBA63           | STM32WBA65             | STM32WBA62             | STM32WBA64     |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|--------------------------------------------------------------|----------------------|------------------------|------------------------|----------------|--|--|

| Secure and nonsecure access supported for the privileged and unprivileged parts of the TZSC.   Set of registers to define product security settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |                  |                                                              |                      |                        |                        |                |  |  |

| Secure and nonsecure access supported for the privileged and unprivileged parts of the TZSC.   Set of registers to define product security settings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |               |                  |                                                              |                      |                        |                        |                |  |  |

| Antitamper detection   Six tamper input bruty tips. 128-byte backup registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | control       | ler)             | Secure and none                                              | secure access suppor | ted for the privileged | and unprivileged parts | s of the TZSC. |  |  |

| CRC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |                  |                                                              | Set of registers     | to define product sec  | urity settings.        |                |  |  |

| High-speed low-voltage (HSLV) mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Antitamper of | letection        |                                                              | Six tamper input/o   | utput pins, 128-byte b | ackup registers.       |                |  |  |

| No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | CRC           | ;                |                                                              |                      | 1× CRC                 |                        |                |  |  |

| Port A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                  | N/A                                                          | N/A                  | HSLV r                 | mode <sup>(1)</sup>    | N/A            |  |  |

| Port A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | VDDIC         | D2               | N/A                                                          | N/A                  | PG[                    | 15:2]                  | N/A            |  |  |

| Port A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                  |                                                              | '                    | PA[15:5, 2:1]          |                        |                |  |  |

| PA[3]   N/A   PA[4]   PA[  |               | Dowt A           | PA[4]                                                        | N/A                  | PA                     | [4]                    | N/A            |  |  |

| Port B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               | ΡοπΑ             | PA[3]                                                        | N/A                  |                        | PA[3]                  |                |  |  |

| Port B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                  |                                                              | PA[(                 | )]                     |                        | N/A            |  |  |

| PB[9, 7:5]   N/A   N/A   PC[12:0]   N/A   N/A   PC[12:0]   N/A   N/A   PC[12:0]   N/A   N/A   PD[15:10, 4:0]   N |               |                  |                                                              | F                    | PB[15:14, 12, 8, 4:0]  |                        |                |  |  |

| Port C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               | Port B           | PB[13, 11:10]                                                | N/A                  |                        | PB[13]                 |                |  |  |

| Port C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                  |                                                              | PB[9,                | 7:5]                   |                        | N/A            |  |  |

| N/A   N/A   PC[12:0]   N/A   PC[12:0]   N/A   PD[15:10, 4:0]   N/A | GPIO          | <b>5</b>         |                                                              |                      | PC[15:13]              |                        |                |  |  |

| Port D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               | Port C           | N/A                                                          | N/A                  | PC[ <sup>2</sup>       | 12:0]                  | N/A            |  |  |

| Port E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               | Port D           |                                                              | N/A N/A              | PD[15:                 | 10, 4:0]               | N/A            |  |  |

| Port G                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |                  | N/A                                                          |                      |                        | PD[9:5]                |                |  |  |

| Port H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               | Port E           | N/A                                                          | N/A                  | PE[                    | 6:0]                   | N/A            |  |  |

| Advanced control   TIM1 (16-bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               | Port G           | N/A                                                          | N/A                  | PG[ <sup>2</sup>       | 15:2]                  | N/A            |  |  |

| Control   General-purpose   TIM2 (32-bit) + TIM3 (16-bit)   TIM2/4 (32-bit) + TIM3 (16-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | Port H           | PH[3]                                                        |                      |                        |                        |                |  |  |