# SR5 E1 line - FCCU fault sources and reaction

# Introduction

This application note describes the input fault sources of the fault collection and control unit (FCCU). Furthermore, for each of them, it describes how to verify the integrity of the error reaction path and the recommended methods to inject each fault.

Before reading this document, the reader should have a clear understanding about the usage of FCCU module itself. Refer to the SR5E1 microcontroller reference manual for further details on each module (see the Appendix A: Reference documents). A reference code is available.

This application note applies to the devices listed in the following table.

**Table 1. Device summary**

| Series | Part number               |

|--------|---------------------------|

| SR5E1x | SR5E1E3, SR5E1E5, SR5E1E7 |

# 1 General information

This document applies to Arm® - based devices of SR5 E1 line, Stellar electrification MCUs - 32-bit Arm® Cortex® M7 architecture microcontroller for electrical vehicle applications.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

# 1.1 Acronyms

Table 2. Acronyms

| Acronym | Name                                                     |  |

|---------|----------------------------------------------------------|--|

| AHB     | Advanced High-performance Bus                            |  |

| AXI     | Advance Extensible Interface                             |  |

| BIST    | Built In Self-Test                                       |  |

| CBIST   | Comparator Built-In Self Test                            |  |

| CEM     | Comparator Built-In Self Test  Combined Error Management |  |

| CMU     | Clock Monitoring Unit                                    |  |

| CPU     | Central Processing Unit                                  |  |

| DCF     | Device Configuration Format                              |  |

| DMA     | Direct Memory Access                                     |  |

| EDC/ECC | Error Detection Code/Error Correction Code               |  |

| EOUT    | Error Out                                                |  |

| FCCU    | Fault Collection and Control Unit                        |  |

| FOSU    | FCCU output supervision unit                             |  |

| HVD     | High Voltage Detector                                    |  |

| IMA     | Indirect Memory Access                                   |  |

| IRCOSC  | Internal 16 MHz RC oscillator                            |  |

| IRQ     | Interrupt Request                                        |  |

| IP      | Intellectual Propriety                                   |  |

| JTAG    | Joint Test Action Group                                  |  |

| LBIST   | Logic Built-in self-test                                 |  |

| LVD     | Low Voltage Detector                                     |  |

| MCU     | Microcontroller Unit                                     |  |

| NMI     | Non-maskable interrupts                                  |  |

| NVM     | Non-volatile Memory                                      |  |

| NVIC    | Nested vectored interrupt controller                     |  |

| NPC     | Nexus debug port                                         |  |

| OTA     | Over The Air                                             |  |

| PBRIDGE | Peripheral Bridge                                        |  |

| PFLASHC | Platform FLASH Controller                                |  |

| PLL     | Phase Lock Loop                                          |  |

| PMC     | Power Management Control                                 |  |

| PMC_DIG | Power Management Controller Digital Interface            |  |

| PRAM    | Platform RAM Controller                                  |  |

AN6042 - Rev 1 page 2/62

| Acronym | Name                                   |  |

|---------|----------------------------------------|--|

| POR     | Power On Reset                         |  |

| RCC     | Reset and Clock Control Module         |  |

| RCCU    | Redundancy Control Checker Unit        |  |

| RM      | Reference Manual                       |  |

| SMPU    | System Memory Protection Unit          |  |

| SoC     | System On Chip                         |  |

| SRAM    | System RAM                             |  |

| SSCM    | System status and configuration module |  |

| STCU3   | Self-Test Control Unit                 |  |

| TCU     | Test Control Unit                      |  |

| XBAR    | CrossBAR                               |  |

| XBIC    | CrossBAR integrity checker             |  |

| XOSC    | External oscillator/crystal            |  |

AN6042 - Rev 1 page 3/62

# 2 Overview

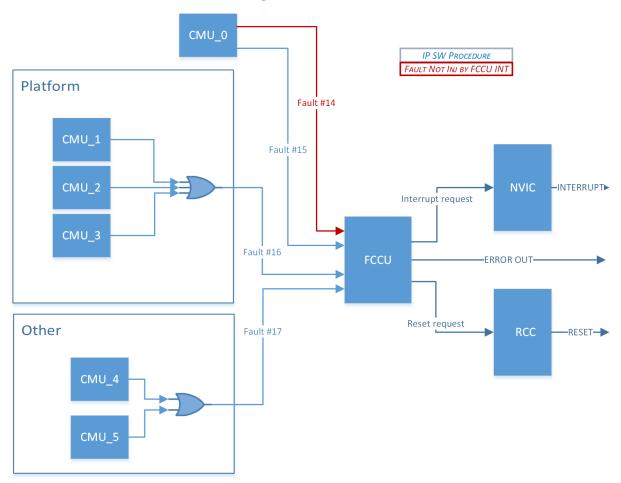

The FCCU is a key element of the functional safety concept of SR5 E1 line devices. This module is responsible for collecting and reacting to failure notifications coming from different modules indicated as "monitors". Examples of monitors are CMU, MEMU2 and so forth.

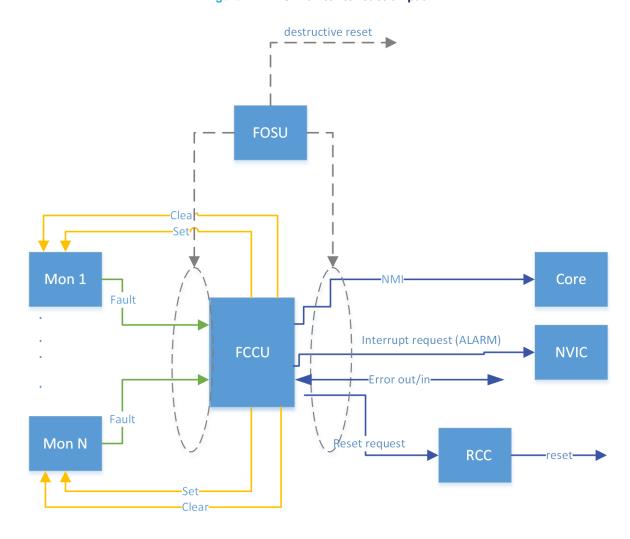

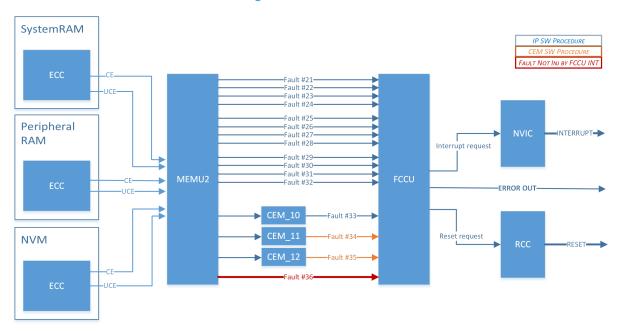

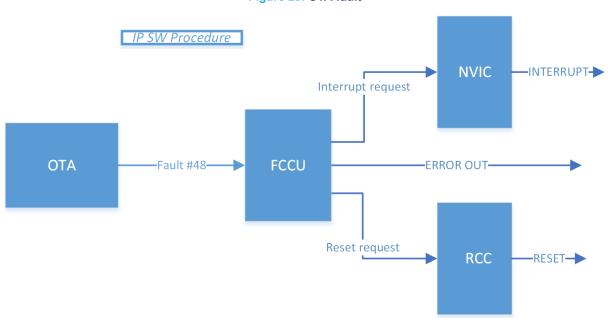

Figure 1. FCCU monitor to reaction path

The Figure 1 shows how the FCCU is connected to the other blocks. The reader shall consider this figure (and all other figures in this document) as a logic schema that not exactly reflects the physical implementation in the silicon.

If a fault occurs the FCCU can move the device into the safe state (the safety manual defines the safe states, requirement SM MCU 1 9) without any CORE intervention.

Note:

Since the FCCU and the whole error reaction path are prone to latent failures, the safety manual requires the execution of a software test to verify the integrity of the error reaction path (requirement SM\_MCU\_3\_31). The user shall run this software test at least once per trip time (the safety analysis assumes a trip time of 12 hours).

This document goes through the list of the faults reported to the FCCU. For each of them it describes how to test the error reaction path to fulfill the previous requirement. Note that the user cannot test the error reaction path for certain monitors (refer to "FCCU fake fault" in the Figure 2).

The Table 3 lists and describes all FCCU input fault sources present on SR5 E1 line MCUs. It provides the recommended method for injecting each fault and for determinating the verification and feasibility of the error reaction path.

AN6042 - Rev 1 page 4/62

Table 3. FCCU failure inputs

| FCCU<br>channel | CEM<br>instance | Source  | Failure description                                    | Error injection mechanism                | Error path verification |

|-----------------|-----------------|---------|--------------------------------------------------------|------------------------------------------|-------------------------|

| 0               | -               | PMC DIG | Temperature detector                                   | FCCU fake fault injection <sup>(1)</sup> | NO                      |

| 1               | -               | PMC DIG | Voltage out of range from LVDs (non-destructive reset) | FCCU fake fault injection <sup>(1)</sup> | NO                      |

| 2               | -               | PMC DIG | Voltage out of range from LVDs (non-destructive reset) | FCCU fake fault injection <sup>(1)</sup> | NO                      |

| 3               | -               | PMC DIG | Digital PMC DCF safety error                           | FCCU fake fault injection <sup>(1)</sup> | NO                      |

| 4               | -               | PMC DIG | Digital PMC voltage detector BIST                      | FCCU fake fault injection <sup>(1)</sup> | YES                     |

| 5               | -               | Flash   | Flash memory initialization error                      | FCCU fake fault injection <sup>(1)</sup> | NO                      |

| 6               | -               | Flash   | Flash reset error                                      | FCCU fake fault injection <sup>(1)</sup> | NO                      |

| 7               | -               | Flash   | FLASH read reference error                             | FCCU fake fault injection <sup>(1)</sup> | NO                      |

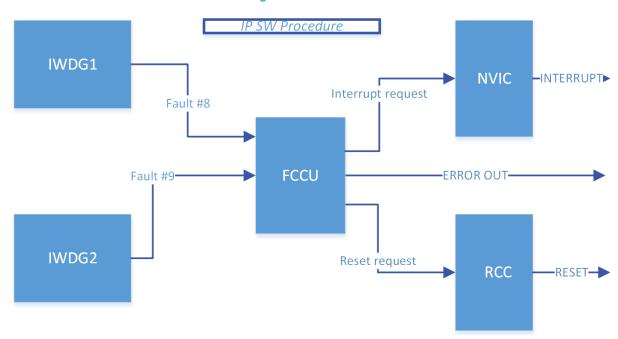

| 8               | -               | IWDG1   | Independent WDG1 reset request                         | Software procedure <sup>(2)</sup>        | YES                     |

| 9               | -               | IWDG2   | Independent WDG2 reset request                         | Software procedure <sup>(2)</sup>        | YES                     |

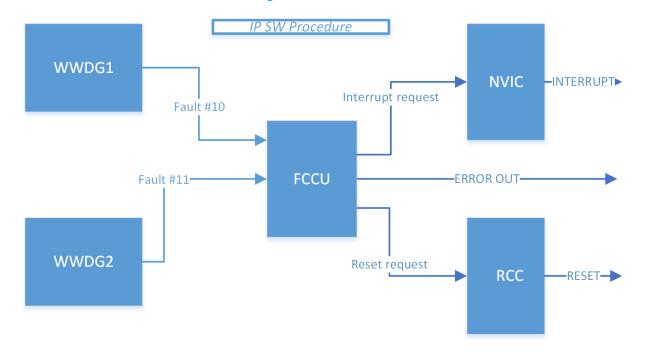

| 10              | -               | WWDG1   | Window watchdog1 reset request                         | Software procedure <sup>(2)</sup>        | YES                     |

| 11              | -               | WWDG2   | Window watchdog2 reset request                         | Software procedure <sup>(2)</sup>        | YES                     |

| 12              | -               | PLL DIG | PLL0 Loss of Lock (Interrupt)                          | Software procedure <sup>(2)</sup>        | YES                     |

| 13              | -               | PLL DIG | PLL1 Loss of Lock (Interrupt)                          | Software procedure <sup>(2)</sup>        | YES                     |

| 14              | -               | CMU     | XOSC less than IRC                                     | FCCU fake fault injection <sup>(1)</sup> | NO                      |

| 15              | -               | CMU     | PLL0 out of frequency                                  | Software procedure <sup>(2)</sup>        | YES                     |

| 16              | -               | CMU     | Sysclk frequency out of range (including HRTIM clock)  | Software procedure <sup>(2)</sup>        | YES                     |

| 17              | -               | CMU     | Monitoring other internal clocks                       | Software procedure <sup>(2)</sup>        | YES                     |

| 18              | -               | -       | -                                                      | -                                        | -                       |

| 19              | -               | STCU3   | BIST result - wrong signature (STCU recoverable fault) | FCCU fake fault injection <sup>(1)</sup> | YES                     |

| 20              | -               | -       | -                                                      | -                                        | -                       |

| 21              | -               | MEMU2   | The fault TRIG_0 from SYS_RAM table                    | Software procedure <sup>(2)</sup>        | YES                     |

| 22              | -               | MEMU2   | The fault TRIG_1 from SYS_RAM table                    | Software procedure <sup>(2)</sup>        | YES                     |

| 23              | -               | MEMU2   | The fault TRIG_2 from SYS_RAM table                    | Software procedure <sup>(2)</sup>        | YES                     |

AN6042 - Rev 1 page 5/62

| FCCU<br>channel | CEM<br>instance | Source                             | Failure description                        | Error injection mechanism             | Error path verification |

|-----------------|-----------------|------------------------------------|--------------------------------------------|---------------------------------------|-------------------------|

| 24              | -               | MEMU2                              | The fault TRIG_3 from SYS_RAM table        | Software procedure <sup>(2)</sup>     | YES                     |

| 25              | -               | MEMU2                              | The fault TRIG_0 from PERIPH_RAM table     | Software procedure <sup>(2)</sup>     | YES                     |

| 26              | -               | MEMU2                              | The fault TRIG_1 from PERIPH_RAM table     | Software procedure <sup>(2)</sup>     | YES                     |

| 27              | -               | MEMU2                              | The fault TRIG_2 from PERIPH_RAM table     | Software procedure <sup>(2)</sup>     | YES                     |

| 28              | -               | MEMU2                              | The fault TRIG_3 from PERIPH_RAM table     | Software procedure <sup>(2)</sup>     | YES                     |

| 29              | -               | MEMU2                              | The fault TRIG_0 from NVM_RAM table        | Software procedure <sup>(2)</sup>     | YES                     |

| 30              | -               | MEMU2                              | The fault TRIG_1 from NVM_RAM table        | Software procedure <sup>(2)</sup>     | YES                     |

| 31              | -               | MEMU2                              | The fault TRIG_2 from NVM_RAM table        | Software procedure <sup>(2)</sup>     | YES                     |

| 32              | -               | MEMU2                              | The fault TRIG_3 from NVM_RAM table        | Software procedure <sup>(2)</sup>     | YES                     |

|                 |                 | CEM_10 MEMU2                       | Sys RAM single bit error table overflow    |                                       | YES                     |

|                 |                 |                                    | Sys RAM uncorrectable error table overflow | CEM software procedure <sup>(3)</sup> |                         |

|                 |                 |                                    | Periph RAM single bit error table overflow |                                       |                         |

| 33              | CEM_10          |                                    | Periph uncorrectable error table overflow  |                                       |                         |

|                 |                 |                                    | NVM single bit error table overflow        |                                       |                         |

|                 |                 |                                    | NVM uncorrectable error table overflow     |                                       |                         |

|                 |                 |                                    | NVM double correctable table overflow      |                                       |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_0                     |                                       |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_1                     |                                       |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_2                     | 1                                     |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_3                     |                                       |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_4                     |                                       |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_5                     |                                       |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_6                     | _                                     |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_7                     | -                                     |                         |

| 34              | CEM_11          | SYS RAM FIFOs to<br>MEMU2 overflow | SYS_RAM_OVRFLOW_FIF0_8                     | CEM software procedure <sup>(3)</sup> | NO                      |

|                 |                 | MEMOZ OVERNOW                      | SYS_RAM_OVRFLOW_FIF0_32                    | procedure                             |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_33                    | 1                                     |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_34                    | 1                                     |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_35                    | -                                     |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_36                    |                                       |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_37                    | 1                                     |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_38                    |                                       |                         |

|                 |                 |                                    | SYS_RAM_OVRFLOW_FIF0_39                    |                                       |                         |

AN6042 - Rev 1 page 6/62

| FCCU<br>channel | CEM<br>instance | Source                                            | Failure description                                                               | Error injection mechanism                | Error path verification |

|-----------------|-----------------|---------------------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------|-------------------------|

|                 |                 |                                                   | SYS_RAM_OVRFLOW_FIF0_40                                                           |                                          |                         |

|                 |                 | 1 SYS RAM FIFOs to MEMU2 overflow                 | SYS_RAM_OVRFLOW_FIF0_41                                                           |                                          |                         |

| 34              | CEM_11          |                                                   | SYS_RAM_OVRFLOW_FIF0_42                                                           | CEM software procedure <sup>(3)</sup>    | NO                      |

|                 |                 |                                                   | SYS_RAM_OVRFLOW_FIF0_43                                                           |                                          |                         |

|                 |                 |                                                   | SYS_RAM_OVRFLOW_FIF0_44                                                           |                                          |                         |

|                 |                 |                                                   | PERIPH_RAM_OVRFLOW_FI F0_0                                                        |                                          |                         |

|                 |                 |                                                   | PERIPH_RAM_OVRFLOW_FI F0_1                                                        |                                          |                         |

|                 |                 |                                                   | PERIPH_RAM_OVRFLOW_FI F0_2                                                        |                                          |                         |

|                 |                 |                                                   | PERIPH_RAM_OVRFLOW_FI F0_32                                                       |                                          |                         |

| 35              | CEM_12          | PERIPH RAM FIFOs to<br>MEMU2 overflow             | PERIPH_RAM_OVRFLOW_FI F0_33                                                       | CEM software procedure <sup>(3)</sup>    | NO                      |

|                 |                 |                                                   | PERIPH_RAM_OVRFLOW_FI F0_34                                                       | procedure                                |                         |

|                 |                 |                                                   | PERIPH_RAM_OVRFLOW_FI F0_35                                                       |                                          |                         |

|                 |                 |                                                   | PERIPH_RAM_OVRFLOW_FI F0_36                                                       |                                          |                         |

|                 |                 |                                                   | PERIPH_RAM_OVRFLOW_FI F0_37                                                       |                                          |                         |

| 36              | -               | MEMU2                                             | MEMU2 FLASH FIFO to MEMU2 overflow                                                | FCCU fake fault injection <sup>(1)</sup> | NO                      |

|                 |                 | CEM_9 Boot errors                                 | SSCM transfer error                                                               |                                          | NO                      |

|                 |                 |                                                   | Memory repair safety error                                                        |                                          |                         |

| 37              | CEM_9           |                                                   | TDM DCF safety error                                                              | CEM software procedure <sup>(3)</sup>    |                         |

|                 |                 |                                                   | RCC DCFs + security miscellaneous DCF                                             |                                          |                         |

| 38              | -               | ERRIN1                                            | Error from unidirectional input error signal (External failure to MCU)            | Software procedure <sup>(2)</sup>        | YES                     |

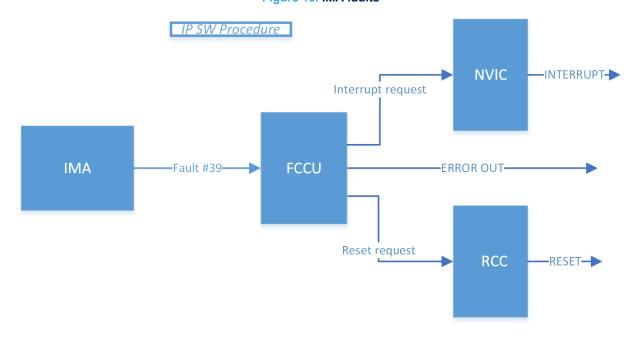

| 39              | -               | IMA                                               | IMA SoC active                                                                    | Software procedure <sup>(2)</sup>        | YES                     |

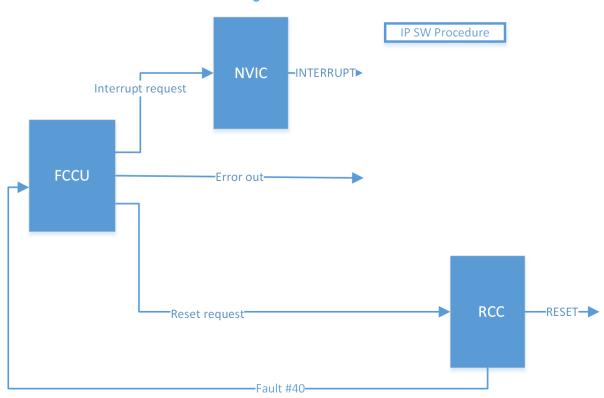

| 40              | -               | RCC                                               | Transition to RCOSC in case of critical faults on clock sources                   | Software procedure <sup>(2)</sup>        | YES                     |

|                 |                 |                                                   | Unexpected activation of JTAG or debug signals                                    |                                          |                         |

| 41              | CEM_13          | SPURIOUS activation of boot/reset functionalities | Unexpected activation of SSCM CS to DCF clients during runtime                    | CEM software procedure <sup>(3)</sup>    | NO                      |

|                 |                 | ranotionalities                                   | Unexpected activation of STCU3 during runtime                                     |                                          |                         |

| 42              | -               | TCU                                               | Test circuitry group spurious activation                                          | FCCU fake fault injection <sup>(1)</sup> | NO                      |

| 43              | -               | -                                                 | -                                                                                 | -                                        | -                       |

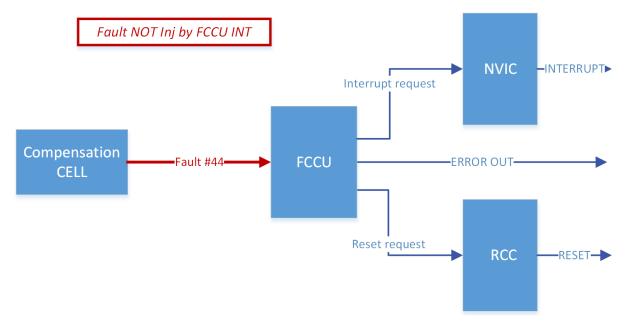

| 44              | -               | COMPENSATION CELLS                                | Pad compensation disabled                                                         | FCCU fake fault injection <sup>(1)</sup> | NO                      |

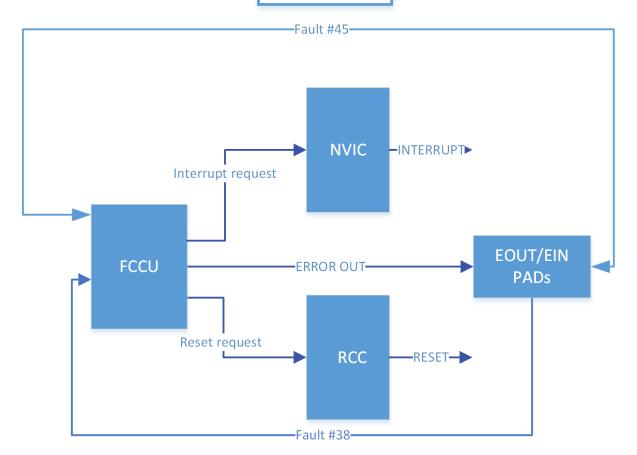

| 45              | -               | ERRIN0                                            | Error from bidirectional input error signal (External or internal failure to MCU) | Software procedure <sup>(2)</sup>        | YES                     |

| 46              | -               | CORE LOCK ALARM                                   | Core lock/split change state alarm                                                | FCCU fake fault injection <sup>(1)</sup> | YES                     |

| 47              | -               | DMA LOCK ALARM                                    | Dma lock/split change state alarm                                                 | FCCU fake fault injection <sup>(1)</sup> | YES                     |

| 48              | -               | OTA ALARM                                         | OTA-X1 swap error                                                                 | Software procedure <sup>(2)</sup>        | NO                      |

AN6042 - Rev 1 page 7/62

| FCCU<br>channel | CEM<br>instance | Source        | Failure description                                                | Error injection mechanism                | Error path verification |

|-----------------|-----------------|---------------|--------------------------------------------------------------------|------------------------------------------|-------------------------|

| 49              | -               | SMPU          | SMPU region violation                                              | Software procedure <sup>(2)</sup>        | YES                     |

| 50              | -               | SMPU          | SMPU monitors that no signal is altered by the SMPU logic          | FCCU fake fault injection <sup>(1)</sup> | YES                     |

| 51              | -               | NVMC1         | EDC after ECC for code NVMC1                                       | Software procedure <sup>(2)</sup>        | YES                     |

| 52              | -               | NVMC1         | EDC after ECC for data NVMC1                                       | Software procedure <sup>(2)</sup>        | YES                     |

| 53              | -               | NVMC1         | Flash encoding errors                                              | Software procedure <sup>(2)</sup>        | YES                     |

| 54              | -               | NVMC1         | PFlashC address feedback error                                     | Software procedure <sup>(2)</sup>        | YES                     |

| 55              | -               | NVMC2         | EDC after ECC for code NVMC2                                       | Software procedure <sup>(2)</sup>        | YES                     |

| 56              | -               | -             | -                                                                  | -                                        | -                       |

| 57              | -               | NVMC2         | Flash encoding error                                               | Software procedure <sup>(2)</sup>        | YES                     |

| 58              | -               | NVMC2         | PFlashC address feedback error                                     | Software procedure <sup>(2)</sup>        | YES                     |

| 59              | -               | NVMC1         | Protocol error on the 2 ports of NVMC1                             | FCCU fake fault injection <sup>(1)</sup> | NO                      |

| 60              | -               | NVMC2         | Protocol error on the 2 ports of NVMC2                             | FCCU fake fault injection <sup>(1)</sup> | NO                      |

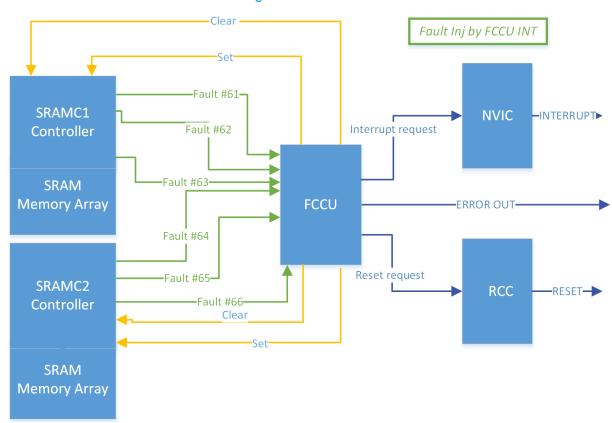

| 61              | -               | SRAMC1        | EDC after ECC PFlashC address feedback error                       | FCCU fake fault injection <sup>(1)</sup> | YES                     |

| 62              | -               | SRAMC1        | PRAMC memory feedback error                                        | FCCU fake fault injection <sup>(1)</sup> | YES                     |

| 63              | -               | SRAMC1        | Address/Control EDC/Parity check<br>PFlashC address feedback error | FCCU fake fault injection <sup>(1)</sup> | YES                     |

| 64              | -               | SRAMC2        | EDC after ECC PRAMC memory feedback error                          | FCCU fake fault injection <sup>(1)</sup> | YES                     |

| 65              | -               | SRAMC2        | PFlashC address feedback error                                     | FCCU fake fault injection <sup>(1)</sup> | YES                     |

| 66              | -               | SRAMC2        | Address/Control EDC/Parity check FCCU alarm                        | FCCU fake fault injection <sup>(1)</sup> | YES                     |

|                 |                 | Core1 - AXIM  | e2eECC data correctable error Core1<br>AXIM                        |                                          |                         |

|                 |                 | Core1 - AHBM  | e2eECC data correctable error Core1<br>AHBM                        | -                                        |                         |

|                 |                 | Core2 - AXIM  | e2eECC data correctable error Core2<br>AXIM                        |                                          | NO                      |

| 67              | CEM_0           | Core2 - AHBM  | e2eECC data correctable error Core2<br>AHBM                        | CEM software procedure <sup>(3)</sup>    |                         |

|                 |                 | HSM - AHB     | e2eECC data correctable error HSM<br>AHB                           |                                          |                         |

|                 |                 | DMA1 - AHBMem | e2eECC data correctable error DMA1<br>AHB memory                   | -                                        |                         |

|                 |                 | DMA1 - AHBPer | e2eECCData correctable error DMA1<br>AHB peripheral                |                                          |                         |

AN6042 - Rev 1 page 8/62

| FCCU<br>channel | CEM<br>instance | Source                            | Failure description                                    | Error injection mechanism                | Error path verification |

|-----------------|-----------------|-----------------------------------|--------------------------------------------------------|------------------------------------------|-------------------------|

| 67              | CEM 0           | DMA2 - AHBMem                     | e2eECCData correctable error DMA2<br>AHB memory        | CEM software                             | NO                      |

| 01              | 07              | DMA2 - AHBPer                     | e2eECC data correctable error DMA2<br>AHB peripheral   | procedure <sup>(3)</sup>                 | NO                      |

|                 |                 | Core1 - AXIM                      | e2eECC data uncorrectable error Core1<br>AXIM          |                                          |                         |

|                 |                 | Core1 - AHBM                      | e2eECC data uncorrectable error Core1<br>AHBM          | _                                        |                         |

|                 |                 | Core2 - AXIM                      | e2eECC data uncorrectable error Core2<br>AXIM          |                                          |                         |

|                 |                 | Core2 - AHBM                      | e2eECC data uncorrectable error Core2<br>AHBM          |                                          |                         |

| 68              | CEM_1           | HSM - AHB                         | e2eECC data uncorrectable error HSM AHB                | CEM software procedure <sup>(3)</sup>    | NO                      |

|                 |                 | DMA1 - AHBMem                     | e2eECC data uncorrectable error DMA1 AHB memory        |                                          |                         |

|                 |                 | DMA1 - AHBPer                     | e2eECCData uncorrectable error DMA1<br>AHB peripheral  |                                          |                         |

|                 |                 | DMA2 - AHBMem                     | e2eECCData uncorrectable error DMA2<br>AHB memory      |                                          |                         |

|                 |                 | DMA2 - AHBPer                     | e2eECC data uncorrectable error DMA2<br>AHB peripheral |                                          |                         |

|                 |                 | Core1 - AXIM                      | e2eECC protocol error Core1 AXIM                       |                                          | NO                      |

|                 |                 | Core1 - AHBM                      | e2eECCProtocol error Core1 AHBM                        |                                          |                         |

|                 |                 | Core2 - AXIM                      | e2eECC protocol error Core2 AXIM                       | -                                        |                         |

|                 |                 | Core2 - AHBM                      | e2eECC protocol error Core2 AHBM                       | CEM software procedure <sup>(3)</sup>    |                         |

|                 |                 | HSM - AHB                         | e2eECC protocol error HSM AHB                          |                                          |                         |

| 69              | CEM_2           | DMA1 - AHBMem                     | e2eECC protocol error DMA1 AHB memory                  |                                          |                         |

|                 |                 | DMA1 - AHBPer                     | e2eECC protocol error DMA1 AHB peripheral              |                                          |                         |

|                 |                 | DMA2 - AHBMem                     | e2eECC protocol error DMA2 AHB memory                  |                                          |                         |

|                 |                 | DMA2 - AHBPer                     | e2eECC protocol error DMA2 AHB peripheral              |                                          |                         |

| 70              | -               | AXI watchdog                      | -                                                      | FCCU fake fault injection <sup>(1)</sup> | NO                      |

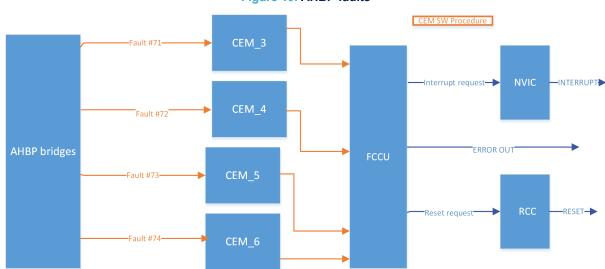

|                 |                 | Completer port to<br>Cores AHBP   | e2eECC data correctable error Cores<br>AHBP            |                                          |                         |

|                 |                 | Completer port to<br>Cores AHB1   | e2eECC data correctable error AHB1                     | CEM software procedure <sup>(3)</sup>    |                         |

|                 |                 | Completer port to<br>Cores AHB2   | e2eECC data correctable error AHB2                     |                                          |                         |

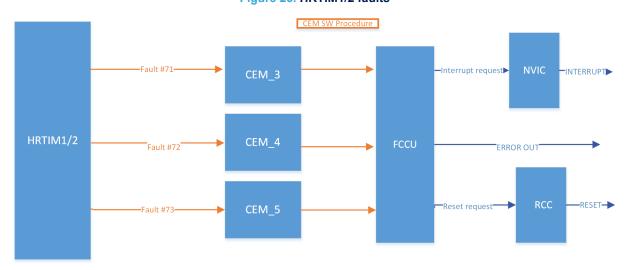

| 71              | CEM_3           | Completer port to<br>Cores APB1   | e2eECC data correctable error APB1                     |                                          | NO                      |

|                 |                 | Completer port to<br>Cores APB2   | e2eECC data correctable error APB2                     |                                          |                         |

|                 |                 | Completer port to<br>Cores HRTIM1 | e2eECC data correctable error HRTIM1<br>AXI            |                                          |                         |

AN6042 - Rev 1 page 9/62

| FCCU<br>channel | CEM<br>instance | Source                            | Failure description                           | Error injection mechanism                | Error path verification |

|-----------------|-----------------|-----------------------------------|-----------------------------------------------|------------------------------------------|-------------------------|

| 71              | CEM_3           | Completer port to<br>Cores HRTIM2 | e2eECC data correctable error HRTIM2<br>AXI   | CEM software procedure <sup>(3)</sup>    | NO                      |

|                 |                 | Completer port to<br>Cores AHBP   | e2eECC data uncorrectable error AHBP          |                                          |                         |

|                 |                 | Completer port to Cores AHB1      | e2eECC data uncorrectable error AHB1          | _                                        |                         |

|                 |                 | Completer port to<br>Cores AHB2   | e2eECC data uncorrectable error AHB2          | CEM software procedure <sup>(3)</sup>    |                         |

| 72              | CEM_4           | Completer port to<br>Cores APB1   | e2eECC data uncorrectable error APB1          |                                          | NO                      |

|                 |                 | Completer port to<br>Cores APB2   | e2eECC data uncorrectable error APB2          |                                          |                         |

|                 |                 | Completer port to<br>Cores HRTIM1 | e2eECC data uncorrectable error<br>HRTIM1 AXI |                                          |                         |

|                 |                 | Completer port to<br>Cores HRTIM2 | e2eECC data uncorrectable error<br>HRTIM2 AXI |                                          |                         |

|                 |                 | Completer port to<br>Cores AHBP   | e2eECC protocol error AHBP                    |                                          |                         |

|                 |                 | Completer port to<br>Cores AHB1   | e2eECC protocol error AHB1                    | CEM software procedure <sup>(3)</sup>    |                         |

|                 |                 | Completer port to<br>Cores AHB2   | e2eECC protocol error AHB2                    |                                          |                         |

| 73              | CEM_5           | Completer port to<br>Cores APB1   | e2eECC protocol error APB1                    |                                          | NO                      |

|                 |                 | Completer port to<br>Cores APB2   | e2eECC protocol error APB2                    |                                          |                         |

|                 |                 | Completer port to<br>Cores HRTIM1 | e2eECC protocol error HRTIM1 AXI              |                                          |                         |

|                 |                 | Completer port to<br>Cores HRTIM2 | e2eECC protocol error HRTIM2 AXI              |                                          |                         |

|                 |                 | Bridge protection -<br>AHB1       |                                               |                                          |                         |

| 74              | CEM 6           | Bridge protection -<br>AHB2       |                                               | CEM software                             | NO                      |

| 74              | CEM_6           | Bridge protection - APB1          |                                               | procedure <sup>(3)</sup>                 | NO                      |

|                 |                 | Bridge protection -<br>APB2       |                                               |                                          |                         |

| 75              | -               | RCCU Core                         | RCCUS for Cores lockstep                      | FCCU fake fault injection <sup>(1)</sup> | YES                     |

| 76              | -               | RCCU DMA                          | RCCUS for DMA lockstep                        | FCCU fake fault injection <sup>(1)</sup> | YES                     |

|                 |                 | RCCU vs. AHB1 subordinators       |                                               |                                          |                         |

|                 |                 | RCCU vs. AHB2 subordinators       | from RCCUSs for subordinators CEM soft        | CEM software                             |                         |

| 77              | CEM_7           | RCCU vs. APB1 subordinators       | dataless duplication lockstep                 | procedure <sup>(3)</sup>                 | NO                      |

|                 |                 | RCCU vs. APB2 subordinators       |                                               |                                          |                         |

AN6042 - Rev 1 page 10/62

| FCCU<br>channel | CEM<br>instance | Source                         | Failure description                                         | Error injection mechanism                | Error path verification |

|-----------------|-----------------|--------------------------------|-------------------------------------------------------------|------------------------------------------|-------------------------|

|                 |                 | RCCU vs. AHBS subordinators    |                                                             |                                          |                         |

|                 |                 | RCCU vs. HRTIM1 subordinators  |                                                             |                                          |                         |

|                 |                 | RCCU vs. HRTIM2 subordinators  |                                                             |                                          |                         |

| 77              | CEM_7           | RCCU vs.<br>NVMC1subordinators | from RCCUSs for subordinators dataless duplication lockstep | CEM software procedure <sup>(3)</sup>    | NO                      |

|                 |                 | RCCU vs. NVMC2 subordinators   |                                                             |                                          |                         |

|                 |                 | RCCU vs. RAMC1 subordinators   |                                                             |                                          |                         |

|                 |                 | RCCU vs. RAMC2 subordinators   |                                                             |                                          |                         |

| 78              | -               | Core1                          | Core1 lockup error                                          | FCCU fake fault injection <sup>(1)</sup> | NO                      |

| 79              | -               | Core2                          | Core2 lockup error                                          | FCCU fake fault injection <sup>(1)</sup> | NO                      |

|                 |                 | Core1 I-TCM                    | I-TCM Core1 address feedback err                            |                                          |                         |

|                 |                 | Core1 D0-TCM                   | D0-TCM Core1 address feedback err                           |                                          |                         |

|                 | CEM_8           | Core1 D1-TCM                   | D1-TCM Core1 address feedback err                           |                                          |                         |

|                 |                 | Core1 I-TCM                    | I-TCM Core1 EDC after ECC                                   |                                          |                         |

|                 |                 | Core1 D0-TCM                   | D0-TCM Core1 EDC after ECC                                  |                                          |                         |

| 80              |                 | Core1 D1-TCM                   | D1-TCM Core1 EDC after ECC                                  | CEM software                             | NO                      |

| 80              | CEIVI_6         | Core2 I-TCM                    | I-TCM Core2 address feedback err                            | procedure <sup>(3)</sup>                 | NO                      |

|                 |                 | Core2 D0-TCM                   | D0-TCM Core2 address feedback err                           |                                          |                         |

|                 |                 | Core2 D1-TCM                   | D1-TCM Core2 address feedback err                           |                                          |                         |

|                 |                 | Core2 I-TCM                    | I-TCM Core2 EDC after ECC                                   |                                          |                         |

|                 |                 | Core2 D0-TCM                   | D0-TCM Core2 EDC after ECC                                  |                                          |                         |

|                 |                 | Core2 D1-TCM                   | D1-TCM Core2 EDC after ECC                                  |                                          |                         |

|                 |                 | Upsizer error - Core1<br>AHB   |                                                             |                                          |                         |

|                 |                 | Upsizer error - Core2<br>AHB   |                                                             |                                          |                         |

|                 |                 | Upsizer error - HSM            |                                                             |                                          |                         |

| 81              | CEM_14          | Upsizer error - DMA1<br>AHBP   | Error response on the bus                                   | CEM software procedure <sup>(3)</sup>    | NO                      |

|                 |                 | Upsizer error - DMA1<br>AHBM   |                                                             |                                          |                         |

|                 |                 | Upsizer error - DMA2<br>AHBP   |                                                             |                                          |                         |

|                 |                 | Upsizer error - DMA2<br>AHBM   |                                                             |                                          |                         |

- 1. Faults injectable by using the FCCU fake fault interface.

- 2. Faults injectable by using a software procedure to stimulate the fault.

- 3. Faults injectable by using the CEM interface.

AN6042 - Rev 1 page 11/62

Before the safety application starts, the user must configure a proper reaction for each FCCU failure input source. See the "FCCU registers reset values" paragraph in the SR5E1x reference manual for the device default configuration.

#### Possible fault reactions are:

- Internal reactions (the user can configure separately the internal reactions for each FCCU input):

- No reset reaction (default)

- IRQ (NMI or alarm)

- Short functional reset

- Long functional reset

- External reaction:

- Error out (EOUT) signaling the status of the MCU

The FCCU controls the EOUT pins without any CORE intervention.

The correctness of FCCU behavior is checked by the FCCU output supervision unit (FOSU). This module monitors the integrity of the FCCU itself, by waiting for any reaction of the FCCU in a fixed time window after an error arrives. The FOSU triggers a destructive reset if its internal counter reaches a timeout before the FCCU takes a reaction to an incoming, and enabled fault. The FOSU does not require any configuration done by the user. A functional reset has no impact on the FCCU.

AN6042 - Rev 1 page 12/62

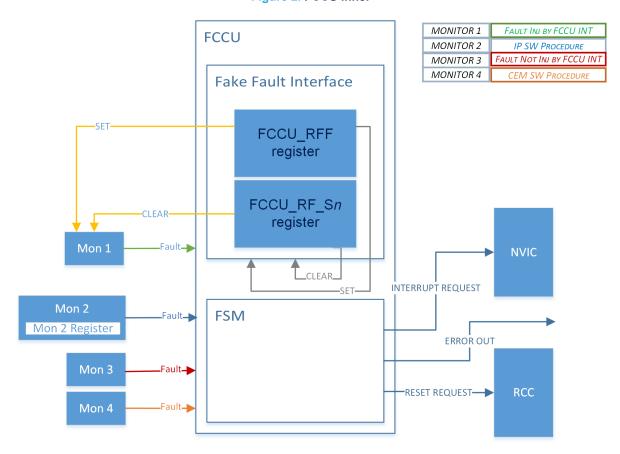

# FCCU fault injection, clearing and fake fault interface

The application can use the fault injection mechanism to diagnose physical defects affecting the connections between the hardware monitors and the FCCU. The procedure to inject a fault depends on the specific monitor. We can distinguish among four different sets of error path, see the table below:

| Monitor type | Fault injection mechanism                  | Error path verification           | Error path test interface                           |

|--------------|--------------------------------------------|-----------------------------------|-----------------------------------------------------|

| MON 1        | Fault injectable by FCCU interface         | YES                               | FCCU fake fault                                     |

| MON 2        | Fault injectable by software procedure     | YES                               | Software procedure (for example, PLL0 loss of lock) |

| MON 3        | Fault NOT injectable by FCCU interface     | NO                                | FCCU fake fault                                     |

| MON 4        | Fault injectable by CEM software procedure | NO/YES (see the dedicate section) | CEM software procedure                              |

Table 4. FCCU error path and monitors

Figure 2. FCCU inner

FCCU fake fault interface can inject faults to verify the entire error path and reaction. (Refer to the Table 3) When the error path is not testable directly by FCCU interface (see Mon 4 – Mon 2) the error injection is still available by programming the interface of some monitors.

AN6042 - Rev 1 page 13/62

Referring to the Figure 2:

To generate the FCCU fake fault event in the Mon 1, an optional signal is available (SET signal in the Figure 2, yellow arrow). The fake fault injection is executed by a write operation into the FCCU\_RFF register, and the corresponding reaction is not maskable. When available, the fake fault injection method is suggested in the following sections.

Note: Some monitors miss the SET signal. In this case (SET signal in the Figure 2, grey arrow) the write operation into the FCCU\_RFF register does not affect the monitor but only the FCCU reaction.

To clear a fault directly in the Mon 1, an optional signal is available (CLEAR signal in the Figure 2, yellow arrow). The de-assertion of the FCCU\_RF\_Sn status bit indicates that the software has properly cleared the fault.

Note: Some monitors miss the CLEAR signal. In this case (CLEAR signal in the Figure 2, grey arrow) the fault can be cleared by a write operation into a specific register of the monitor.

CEM interface provides an injection procedure in Mon 4 (see in the Figure 2), orange arrow. Refers to the Section 3.1: CEM module.

Depending on the type of monitor, fault indication can either be a pulse (edge-triggered) or a constant value (level-triggered).

The fault management shall consider that the user can configure a fault input channel in the FCCU as:

- Hardware recoverable fault, that is, the fault status within the FCCU remains asserted until the monitor keeps the fault indication asserted. As soon as the monitor clears the fault indication, it also clears the fault status within the FCCU.

- Software recoverable fault, that is, the fault status within the FCCU remains asserted until the software clears it even if the monitor de-asserts the fault indication.

The generic recommendation is to configure all faults as software recoverable. In such a way, the FCCU clears the respective status flag only after an explicit request from the software. In case of hardware recoverable, the status flag automatically clears, and the application may not react properly to the incoming fault.

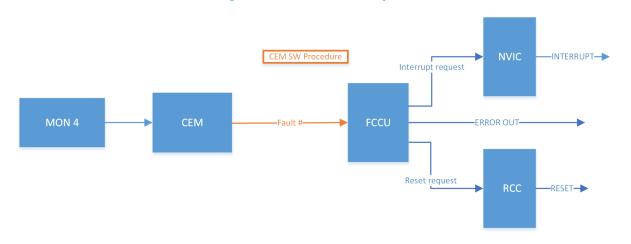

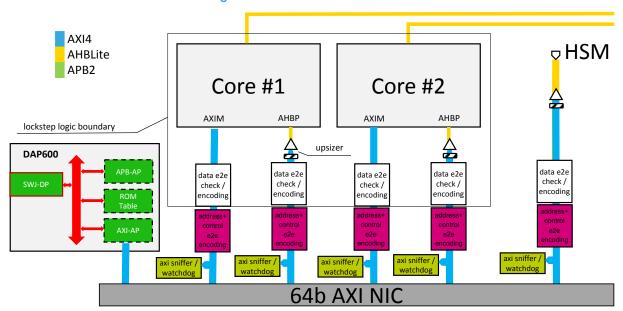

## 3.1 CEM module

The collective error manager (CEM) module contains registers dedicated to control and status reporting of errors from safety monitors to FCCU module. The error signals connected to a CEM module are OR-ed together to generate one FCCU trigger. The module contains internal registers (per error group) for controlling and capturing status of errors from safety monitors, as well as fake fault injection, and IPS programmable registers for accessing internal registers.

IPS programmable registers (32-bit) are used to control and capture error status of the CEM internal registers. Refer to device SR5E1 Reference Manual for further details on the CEM module.

Note: The SR5E1x contains 15 CEM instances (CEM0 to CEM14). Each instance has only one error group (Group0).

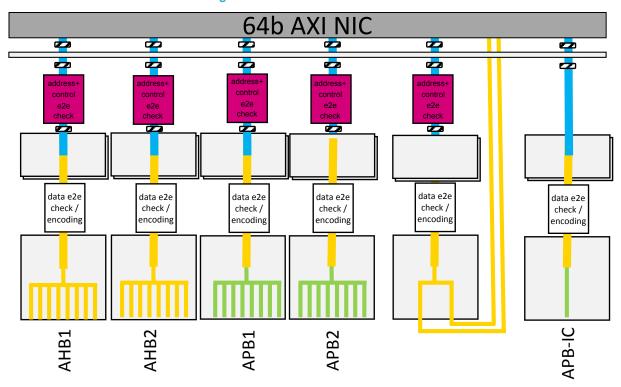

Figure 3. CEM error reaction path

AN6042 - Rev 1 page 14/62

The fake fault mechanism inside CEM module is available to verify the error reaction path by a software procedure: CEM channel must be enabled (default is already enabled), the fault must be injected through the CEM CMD register.

The user can inject this type of fault by:

- 1. Enabling fault (CMD[KEY] = 0xA5A5, CMD[CMD] = 0x1, CMD[FAULT\_OR\_GRP\_NUM] = Fault number or group number

- 2. Injecting a CEM fault((CMD[KEY] = 0xA5A5, CMD[CMD] = 0x3,CMD[FAULT\_OR\_GRP\_NUM] = Fault number or group number)

The FCCU error reaction path is verified if the FCCU\_RF\_Sx[RFSyy] status bit is set after step (2) The user can clear the fault by:

- Clearing the injection mechanism at CEM level((CMD[KEY] = 0xA5A5, CMD[CMD] = 0x4, CMD[FAULT\_OR\_GRP\_NUM] = Fault number or group number)

- 2. Clearing the relevant FCCU\_RF\_Sx[RFSyy] bit

AN6042 - Rev 1 page 15/62

# 4 Faults description

The following sections describe all the faults incoming to FCCU for SR5E1 device and how, if possible, to inject them for checking the integrity of the relevant reaction path.

The following color convention is adopted in the following figures:

- The GREEN arrow marks the faults injectable inside the safety monitor (MON 1) by the FCCU fake fault interface.

- The **BLUE** arrow marks the faults injectable inside the safety monitor (MON 2) by a software procedure that stimulates the error path.

- The RED arrow marks the faults that cannot be directly injectable (MON3).

There is no direct connection to stimulate the error path between safety monitor and FCCU. Only the fake fault, internally to FCCU module, can be injected (GREY arrows in the Figure 2).

- The ORANGE arrow marks the faults injectable inside the safety monitor (MON 4) by a software procedure using the CEM interface.

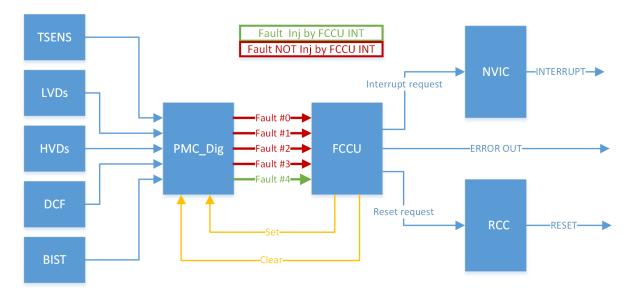

# 4.1 PMC\_DIG faults

PMC\_DIG is the source of five different FCCU input faults. Refer to device SR5E1 microcontroller reference manual for further details on PMC\_DIG.

Figure 4. PMC\_DIG faults

# 4.1.1 Temperature detector out of range (Fault #0)

The temperature detector, inside PMC\_DIG module, detects if the temperature exceeds the defined thresholds (there are three thresholds: TS0, TS1 and TS2: temperature detector thresholds are trimmed at testing phase and cannot be configured by the user) and the PMC\_DIG forwards this fault to the FCCU.

The error injection mechanism is only available within the FCCU fake fault interface (MON3). The error path between safety monitor and FCCU is not stimulated.

The user injects the fake fault by setting the error code 0x00 in the FCCU\_RFF[FRFC] field. The FCCU error reaction is verified if the FCCU\_RF\_S0[RFS0] is set.

The fault clear mechanism requires that the status FCCU\_RF\_S0[RFS0] bit be reset.

Note: For TS0, TS1, TS2 value refer to the datasheet.

AN6042 - Rev 1 page 16/62

### 4.1.2 Voltage out of range from LVDs (Fault #1)

Each LVD detects a voltage that drops below the defined threshold and the PMC\_DIG forwards this fault to the FCCU. The MCU embeds some LVDs (see SR5E1 reference manual for further details on LVDs) and their output signals are OR-ed before arriving at the FCCU failure input #1.

The error injection mechanism is only available within the FCCU fake fault interface (MON3). The error path between safety monitor and FCCU is not stimulated.

The user injects the fake fault by setting the error code 0x01 in the FCCU\_RFF[FRFC] field. The FCCU error reaction is verified if the FCCU\_RF\_S0[RFS1] is set.

The fault clear mechanism requires that the status FCCU RF S0[RFS1] bit be reset.

#### 4.1.3 Voltage out of range from HVDs (Fault #2)

Each HVD detects a voltage that rises above the defined threshold and the PMC\_DIG forwards this fault to the FCCU. The MCU embeds some HVDs (see SR5E1 reference manual for further details on HVDs) and their output signals are OR-ed before arriving at the FCCU failure input #2.

The error injection mechanism is only available within the FCCU fake fault interface (MON3). The error path between safety monitor and FCCU is not stimulated.

The user injects the fake fault by setting the error code 0x02 in the FCCU\_RFF[FRFC] field. The FCCU error reaction is verified if the FCCU\_RF\_S0[RFS2] is set.

The fault clear mechanism requires that the status FCCU RF S0[RFS2] bit be reset.

#### 4.1.4 Digital PMC initialization error during DCF data load (Fault #3)

DCF records are used to configure certain registers in the device during system boot. If an error occurs while the SSCM loads the values into the PMC registers, the PMC DIG forwards this fault to the FCCU.

The error injection mechanism is only available within the FCCU fake fault interface (MON3). The error path between safety monitor and FCCU is not stimulated.

The user injects the fake fault by setting the error code 0x03 in the FCCU\_RFF[FRFC] field. The FCCU error reaction is verified if the FCCU\_RF\_S0[RFS3] is set.

The fault clear mechanism requires that the status FCCU RF S0[RFS3] bit be reset.

# 4.1.5 Digital PMC voltage detector BIST (Fault #4)

The voltage detector BIST verifies the integrity of all the voltage monitors. In case the BIST fails, the PMC\_DIG forwards this fault to the FCCU.

The user can inject this fault by the FCCU fake fault interface. The error path between safety monitor and FCCU is stimulated.

The user must set the PMC\_DIG\_BIST\_CTRL[NCFEN] bit to enable a user BIST not critical fault indication to the FCCU and inject a fake fault by setting the FCCU\_RFF[FRFC] field to the value 0x04. The FCCU error reaction path is verified if both the FCCU\_RF\_S0[RFS4] and the PMC\_DIG\_BIST\_CTRL[NCFST] status bits are set.

The PMC\_DIG\_BIST\_CTRL [NCFST] status bit indicates a BIST fail on completion of BIST sequence. The fault clear mechanism requires that the status FCCU RF S0[RFS4] bit be reset.

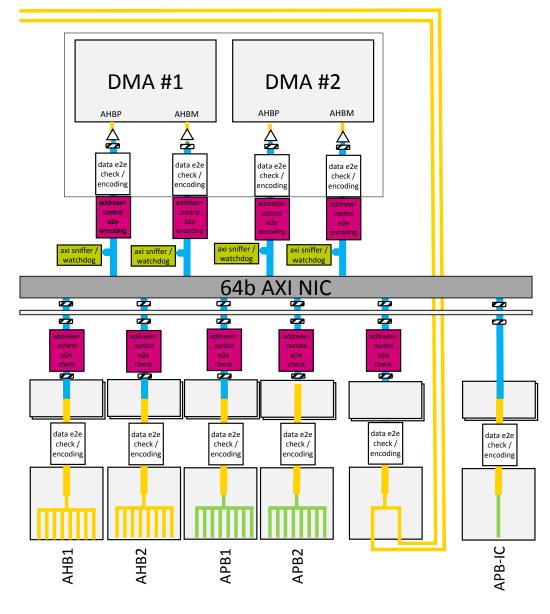

# 4.2 FLASH/PFLASHC faults

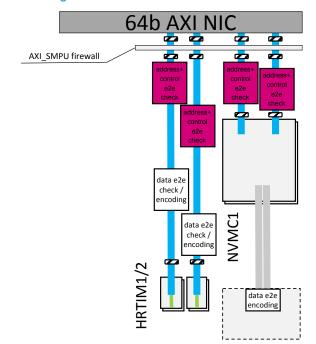

Throughout the document, both flash and nonvolatile memory (NVM) are used indistinctly because SR5E1x uses flash memory as a type of NVM. Note that for flash memory controller PFLASHC and NVMC are used indistinctly in the document as well. The flash memory controllers (NVMPC1, NVMPC2) manage CPU AXI accesses to the flash memory. They implement the erase and program flash memory operations and the read and write protection mechanisms. Refer to device SR5E1x reference manual for further details on FLASH and PFLASHC.

AN6042 - Rev 1 page 17/62

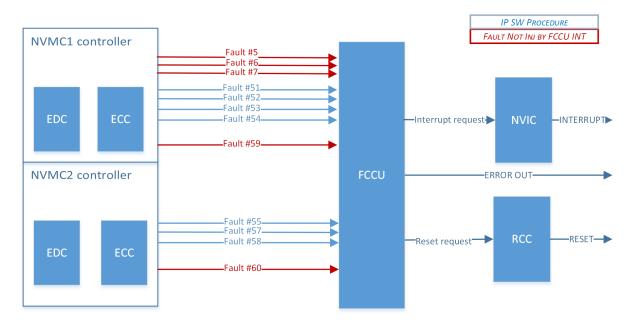

Figure 5. FLASH/PFLASHC faults

# 4.2.1 Flash fatal error (Fault #5)

An unexpected condition, for example, ECC double-bit detections on the reset reads, can occur within the FLASH memory during its initial configuration and the FLASH memory forwards this fault to the FCCU.

The error injection mechanism is only available within the FCCU fake fault interface (MON3). The error path between safety monitor and FCCU is not stimulated.

The user injects the fake fault by setting the error code 0x05 in the FCCU\_RFF[FRFC] field. The FCCU error reaction is verified if the FCCU\_RF\_S0[RFS5] is set.

The fault clear mechanism requires that the status FCCU\_RF\_S0[RFS5] bit be reset.

## 4.2.2 Flash reset error (Fault #6)

FLASH forwards this fault to the FCCU in case one of the following unrecoverable errors occurs:

- ECC errors on FLASH internal reads during configuration loading (startup);

- ECC errors on FLASH internal reads during firmware copy (startup);

- Double ECC errors on KRAM (RAM not visible to the user) during an internal self-check routine (always running).

The error injection mechanism is only available within the FCCU fake fault interface (MON3). The error path between safety monitor and FCCU is not stimulated.

The user injects the fake fault by setting the error code 0x06 in the FCCU\_RFF[FRFC] field. The FCCU error reaction is verified if the FCCU\_RF\_S0[RFS6] is set.

The fault clear mechanism requires that the status FCCU\_RF\_S0[RFS6] bit be reset.

# 4.2.3 Flash read reference error (Fault #7)

The FLASH monitors its internal current and voltage references. In case one of these values is out of the allowed range, FLASH forwards this fault to the FCCU.

The error injection mechanism is only available within the FCCU fake fault interface (MON3). The error path between safety monitor and FCCU is not stimulated.

The user injects the fake fault by setting the error code 0x07 in the FCCU\_RFF[FRFC] field. The FCCU error reaction is verified if the FCCU\_RF\_S0[RFS7] is set.

The fault clear mechanism requires that the status FCCU RF S0[RFS7] bit be reset.

AN6042 - Rev 1 page 18/62

### 4.2.4 NVMC1 EDC after ECC for code FLASH (Fault #51)

The EDC after ECC logic inside the NVMC1 detects a hardware fault in the ECC logic resulting in a corrupted ECC correction for the code flash array and the NVMC1 forwards this fault to the FCCU.

#### The user can inject this fault by:

- 1. Enabling the error forwarding to FCCU (FLTENA[NVM FLTENA NVMCEDC] = 0x1, of NVM1 module)

- 2. Forcing the error latching to check the error reporting path (FLTFRC[NVM\_FLTFRC\_NVMCEDC] = 0x1) The FCCU error reaction path is verified if the FCCU\_RF\_S1[RFS19] status bit is set after step (2).

#### The user can clear the fault by:

- 1. Clearing the fault source error (FLTSCR[NVM FLTFRC NVMCEDC] = 0x1)

- 2. Clearing the relevant FCCU\_RF\_S1[RFS19] bit

#### 4.2.5 NVMC1 EDC after ECC for data FLASH (Fault #52)

The EDC after ECC logic inside the NVMC1 detects a hardware fault in the ECC logic resulting in a corrupted ECC correction for the data flash and the NVMC1 forwards this fault to the FCCU.

## The user can inject this fault by:

- 1. Enabling the error forwarding to FCCU (FLTENA[NVM\_FLTENA\_NVMDEDC] = 0x1, of NVM1 module)

- 2. Forcing the error latching to check the error reporting path (FLTFRC[NVM\_FLTENA\_NVMDEDC] = 0x1) The FCCU error reaction path is verified if the FCCU RF S1[RFS20] status bit is set after step (2).

#### The user can clear the fault by:

- 1. Clearing the fault source error (FLTSCR[NVM FLTENA NVMDEDC] = 0x1)

- 2. Clearing the relevant FCCU RF S1[RFS20] bit

#### 4.2.6 NVMC1 FLASH memory access fault (Fault #53)

The NVMC1 detects faults resulting in a corrupted FLASH memory access and it forwards this fault to FCCU.

#### The user can inject this fault by:

- 1. Enabling the error forwarding to FCCU (FLTENA[NVM FLTENA NVMENCE] = 0x1, of NVM1 module)

- 2. Forcing the error latching to check the error reporting path (FLTFRC[NVM\_FLTENA\_NVMENCE] = 0x1) The FCCU error reaction path is verified if the FCCU\_RF\_S1[RFS21] status bit is set after step (2).

#### The user can clear the fault by:

- 1. Clearing the fault source error (FLTSCR[NVM FLTENA NVMENCE] = 0x1)

- 2. Clearing the relevant FCCU RF S1[RFS21] bit

#### 4.2.7 NVMC1 address feedback error (Fault #54)

The NVMC1 flash controller detects a transaction monitor mismatch when compared with the flash safety feedback outputs and it forwards this fault to FCCU.

#### The user can inject this fault by:

- 1. Enabling the error forwarding to FCCU (FLTENA[NVM FLTENA NVMPCENC] = 0x1, of NVM1 module)

- 2. Forcing the error latching to check the error reporting path (FLTFRC[NVM\_FLTENA\_NVMPCENC] = 0x1) The FCCU error reaction path is verified if the FCCU RF S1[RFS22] status bit is set after step (2).

#### The user can clear the fault by:

- 1. Clearing the fault source error (FLTSCR[NVM FLTENA NVMPCENC] = 0x1)

- 2. Clearing the relevant FCCU\_RF\_S1[RFS22] bit

#### 4.2.8 NVMC2 EDC after ECC for code FLASH (Fault #55)

The EDC after ECC logic inside the NVMC2 detects a hardware fault in the ECC logic resulting in a corrupted ECC correction for the code flash array and the NVMC2 forwards this fault to the FCCU.

#### The user can inject this fault by:

- 1. Enabling the error forwarding to FCCU (FLTENA[NVM FLTENA NVMCEDC] = 0x1, of NVM2 module)

- 2. Forcing the error latching to check the error reporting path (FLTFRC[NVM\_FLTFRC\_NVMCEDC] = 0x1) The FCCU error reaction path is verified if the FCCU RF S1[RFS23] status bit is set after step (2).

The user can clear the fault by:

AN6042 - Rev 1 page 19/62

- 1. Clearing the fault source error (FLTSCR[NVM\_FLTFRC\_NVMCEDC] = 0x1)

- 2. Clearing the relevant FCCU RF S1[RFS23] bit

#### 4.2.9 NVMC2 FLASH memory access fault (Fault #57)

The NVMC2 detects faults resulting in a corrupted FLASH memory access and it forwards this fault to FCCU.

#### The user can inject this fault by:

- 1. Enabling the error forwarding to FCCU (FLTENA[NVM\_FLTENA\_NVMENCE] = 0x1, of NVM2 module)

- 2. Forcing the error latching to check the error reporting path (FLTFRC[NVM\_FLTENA\_NVMENCE] = 0x1)

The FCCU error reaction path is verified if the FCCU RF S1[RFS24] status bit is set after step (2).

#### The user can clear the fault by:

- 1. Clearing the fault source error (FLTSCR[NVM\_FLTENA\_NVMENCE] = 0x1)

- 2. Clearing the relevant FCCU\_RF\_S1[RFS24] bit

## 4.2.10 NVMC2 address feedback error (Fault #58)

The NVMC2 flash controller detects a transaction monitor mismatch when compared with the flash safety feedback outputs and it forwards this fault to FCCU.

#### The user can inject this fault by:

- 1. Enabling the error forwarding to FCCU (FLTENA[NVM FLTENA NVMPCENC] = 0x1, of NVM2 module)

- 2. Forcing the error latching to check the error reporting path (FLTFRC[NVM\_FLTENA\_NVMPCENC] = 0x1, of NVM2 module)

The FCCU error reaction path is verified if the FCCU RF S1[RFS25] status bit is set after step (2).

#### The user can clear the fault by:

- 1. Clearing the fault source error (FLTSCR[NVM FLTENA NVMPCENC] = 0x1)

- 2. Clearing the relevant FCCU RF S1[RFS25] bit

#### 4.2.11 e2eECC NVMC1 protocol error (Fault #59)

The ECC logic detects protocol bits error and forwards this fault to FCCU.

The error injection mechanism is only available within the FCCU fake fault interface (MON3). The error path between safety monitor and FCCU is not stimulated.

The user injects the fake fault by setting the error code 0x3B in the FCCU\_RFF[FRFC] field. The FCCU error reaction is verified if the FCCU\_RF\_S1[RFS27] is set.

The fault clear mechanism requires that the status FCCU RF S1[RFS27] bit be reset.

#### 4.2.12 e2eECC NVMC2 protocol error (Fault #60)

The ECC logic detects protocol bits error and forwards this fault to FCCU.

The error injection mechanism is only available within the FCCU fake fault interface (MON3). The error path between safety monitor and FCCU is not stimulated.

The user injects the fake fault by setting the error code 0x3C in the FCCU\_RFF[FRFC] field. The FCCU error reaction is verified if the FCCU\_RF\_S1[RFS28] is set.

The fault clear mechanism requires that the status FCCU RF S1[RFS28] bit be reset.

## 4.3 STCU3 faults

The STCU3 is a comprehensive programmable hardware module that controls the execution of the self-test, that runs a specific logic built in self-test (CBIST) and a memory built-in self-test (MBIST). The STCU3 is the source of one FCCU input faults. Refer to device SR5E1x microcontroller reference manual for further details on STCU3.

AN6042 - Rev 1 page 20/62

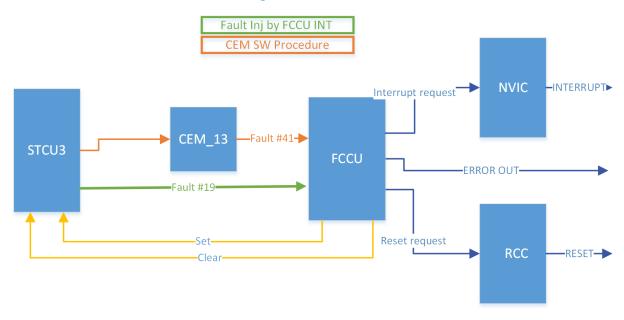

Figure 6. STCU3 faults

#### 4.3.1 BIST result - wrong signature (STCU3 recoverable fault), (Fault #19)

If the BIST detects a fault that is configured as recoverable fault, the STCU3 forwards this fault to the FCCU. Although BIST can detect permanent faults, this fault can also be triggered in case of transient faults. The STCU3 can trigger this fault only during BIST execution (SR5E1x device only supports offline BIST. For more details, refer to device SR5E1 reference manual).

The user can inject this fault by the FCCU fake fault interface. The error path between safety monitor and FCCU is stimulated.

The user injects the fake fault by setting the error code 0x13 in the FCCU\_RFF[FRFC] field. The FCCU error reaction is verified if the FCCU\_RF\_S0[RFS19] is set.

The fault clear mechanism requires that the status FCCU\_RF\_S0[RFS19] bit be reset.

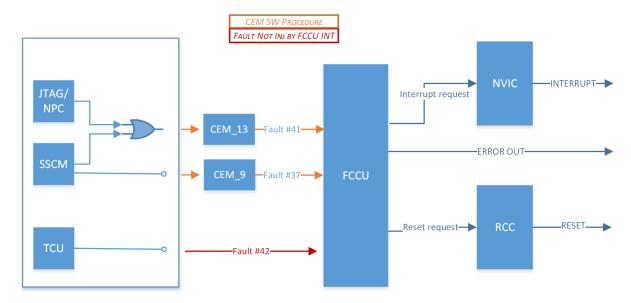

## 4.3.2 SPURIOUS STCU3 activation (Fault #41, CEM 13, bit#2)

Unexpected activation of STCU3 during the application execution can interfere with the application. If this event occurs, a dedicated glue logic forwards this fault to the FCCU.

This error signal is collected by CEM 13, before arriving to the FCCU failure input #41.

The user can inject a fake fault by a software procedure that sets CEM functionality: the fault must be injected through the CEM CMD register. For more details see the Section 3.1: CEM module.

Table 5. CEM reg bit # for spurious STCU3 activation

| CEM reg bit # | Failure                   | CMD[FAULT_OR_GRP_NUM] value |

|---------------|---------------------------|-----------------------------|

| 2             | SPURIOUS STCU3 ACTIVATION | 0x2                         |

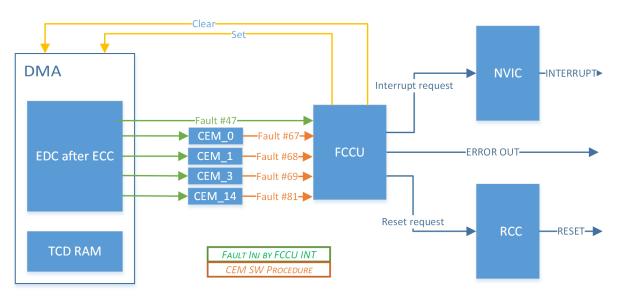

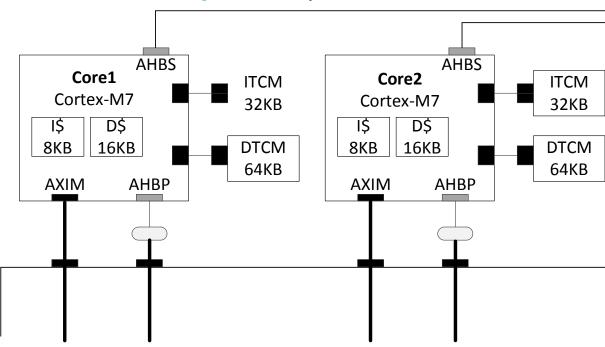

## 4.4 DMA faults

Direct memory access (DMA) provides high-speed data transfer between peripherals and memory and between memory and memory. Data can be quickly moved by DMA without any CPU action. Refer to device SR5E1x reference manual for further details on the DMA.

AN6042 - Rev 1 page 21/62

AN6042 - Rev 1 page 22/62

Figure 8. DMA e2eECC schematic

## 4.4.1 DMA lock/split change state alarm (Fault #47)

Each DMA instance has a replica that can be enabled in lockstep to reach a high level of safety.

The DMA controllers can work in lock or split mode, an involuntary change in mode triggers to FCCU an error.

The user can inject this fault by the FCCU fake fault interface. The error path between safety monitor and FCCU is stimulated.

The user must set the FCCU\_RFF[FRFC] field to the value 0x2F. The FCCU error reaction is verified if the FCCU\_RF\_S1[RFS15] status bit is set.

The fault clear mechanism requires that the status FCCU\_RF\_S1[RFS15] bit be reset.

# 4.4.2 e2eECC data correctable error DMA1/2 AHB Memory/Peripheral (Fault #67, CEM \_0)

The ECC logic detects data correctable error bits. This error signal is collected by CEM\_0, before arriving to the FCCU failure input #67.

The user can inject a fake fault by a software procedure that sets CEM functionality: the fault must be injected through the CEM CMD register. For more details see the Section 3.1: CEM module.

AN6042 - Rev 1 page 23/62

Table 6. CEM reg bit # for DMA correctable error

| CEM reg bit # | Failure                                           | CMD[FAULT_OR_GRP_NUM] value |

|---------------|---------------------------------------------------|-----------------------------|

| 5             | e2eECC data correctable error DMA1 AHB memory     | 0x5                         |

| 6             | e2eECC data correctable error DMA1 AHB peripheral | 0x6                         |

| 7             | e2eECC data correctable error DMA2 AHB memory     | 0x7                         |

| 8             | e2eECC data correctable error DMA2 AHB peripheral | 0x8                         |

## 4.4.3 e2eECC data uncorrectable error DMA1/2 AHB memory/peripheral (Fault #68, CEM\_1)

The ECC logic detects data uncorrectable error bits. This error signal is collected by CEM\_1, before arriving to the FCCU failure input #68.

The user can inject a fake fault by a software procedure that sets CEM functionality: the fault must be injected through the CEM CMD register. For more details see the Section 3.1: CEM module.

Table 7. CEM reg bit # for DMA uncorrectable error

| CEM reg bit # | Failure                                             | CMD[FAULT_OR_GRP_NUM] value |

|---------------|-----------------------------------------------------|-----------------------------|

| 5             | e2eECC data uncorrectable error DMA1 AHB memory     | 0x5                         |

| 6             | e2eECC data uncorrectable error DMA1 AHB peripheral | 0x6                         |

| 7             | e2eECC data uncorrectable error DMA2 AHB memory     | 0x7                         |

| 8             | e2eECC data uncorrectable error DMA2 AHB peripheral | 0x8                         |

## 4.4.4 e2eECC protocol error DMA1/2 AHB memory/peripheral (Fault #69, CEM\_3)

The ECC logic detects protocol error bits. This error signal is collected by CEM\_3, before arriving to the FCCU failure input #69.

The user can inject a fake fault by a software procedure that sets CEM functionality: the fault must be injected through the CEM CMD register. For more details see the Section 3.1: CEM module.

Table 8. CEM reg bit # for DMA protocol error

| CEM reg bit # | Failure                                   | CMD[FAULT_OR_GRP_NUM] value |

|---------------|-------------------------------------------|-----------------------------|

| 5             | e2eECC protocol error DMA1 AHB memory     | 0x5                         |

| 6             | e2eECC protocol error DMA1 AHB peripheral | 0x6                         |

| 7             | e2eECC protocol error DMA2 AHB memory     | 0x7                         |

| 8             | e2eECC protocol error DMA2 AHB peripheral | 0x8                         |

## 4.4.5 e2eECC upsizer error DMA1/2 AHB memory/peripheral (Fault #81, CEM\_14)

When a decode error response is seen on the bus DMA1 AHB peripheral, DMA1 AHB memory, DMA2 AHB peripheral, DMA2 AHB memory a fault is detected. This error signals is collected by CEM\_14, before arriving to the FCCU failure input #81.

The user can inject a fake fault by a software procedure that sets CEM functionality: the fault must be injected through the CEM CMD register. For more details see the section Section 3.1: CEM module.

Table 9. CEM reg bit # for DMA upsizer

| CEM reg bit # | Failure                   | CMD[FAULT_OR_GRP_NUM] value |

|---------------|---------------------------|-----------------------------|

| 3             | Upsizer error - DMA1 AHBP | 0x3                         |

| 4             | Upsizer error - DMA1 AHBM | 0x4                         |

| 5             | Upsizer error - DMA1 AHBP | 0x5                         |

| 6             | Upsizer error - DMA1 AHBM | 0x6                         |

AN6042 - Rev 1 page 24/62

### 4.5 MEMU2 faults

The MEMU2 is responsible for collecting and reporting error events to the fault collection and control unit (FCCU) associated with faults detected by memory BISTs as well as ECC (error correction code) logic, used on system-accessible RAM, peripheral local RAM, non-volatile memory (NVM).

When any of the following events occurs, the MEMU2 receives an error signal that causes an event to be recorded. When multiple errors are indicated from various sources at the same instant, an overflow can be indicated by the MEMU2 to the FCCU. Overflow can also be indicated if the reporting table entries are full, and a new unique error is reported by the system. The corresponding error flags are set and reported to FCCU. Refer to device SR5E1 reference manual for further details on the MEMU2.

Figure 9. MEMU2 faults

## 4.5.1 MEMU2 SYS Trigger fault

The user must address the correctable and uncorrectable ECC error trigger.

The user can choose the SYS\_RAM\_TRIG\_0, SYS\_RAM\_TRIG\_1, SYS\_RAM\_TRIG\_2, SYS\_RAM\_TRIG\_3.