Application note

## L9788 variable reluctance sensor (VRS)

#### Introduction

This application note is intended to integrate the information provided in the L9788 product datasheet to facilitate the usage.

### 1 VRS interface detailed explanation

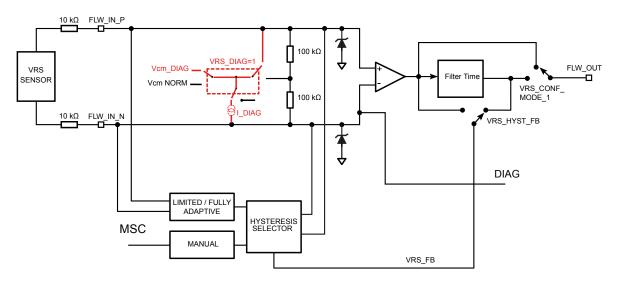

VRS interface runs either in normal mode to convert the input differential voltage or in diagnostic mode to detect eventual short to ground, short to battery, or open condition at sensor pins.

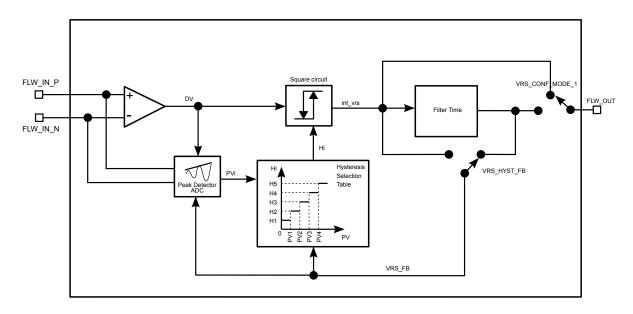

The Figure 1 shows the main elements of the VRS interface and, in red, the internal connection in case of diagnostic mode active.

Figure 1. VRS interface block diagram

GADG0612160835PS

The operating mode is defined in the VRS register through the VRS DIAG bit in CONFIG REG8:

- If VRS DIAG = 0, the VRS block is set in normal mode

- If VRS\_DIAG = 1, the VRS diagnosis mode is activated

When the L9788 is supplied and the VRS is running, the following conditions may occur:

- If the FLW\_IN\_P or FLW\_IN\_N voltage rises over V<sub>clpH</sub>, the voltage is clamped at V<sub>clpH</sub>.

- If the FLW\_IN\_P or FLW\_IN\_N voltage falls below V<sub>clpL</sub>, the voltage is clamped at V<sub>clpL</sub>.

The clamp activation, either on FLW\_IN\_P or FLW\_IN\_N, is specified by design and the FLW\_IN\_P voltage is higher than FLW\_IN\_N.

AN6023 - Rev 1 page 2/18

#### 2 VRS-Normal mode

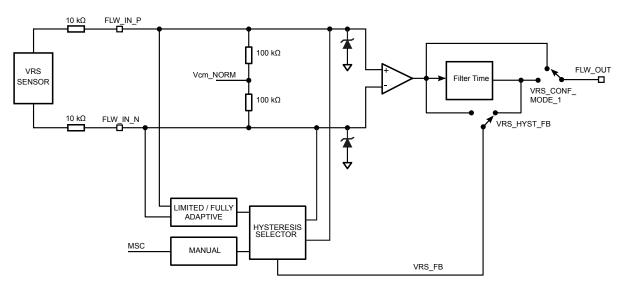

The VRS normal mode is set with VRS DIAG = 0.

In normal mode, the circuit is configured as the one reported in the Figure 2. It allows decoding the VRS signal while the flying wheel is in rotation.

Figure 2. VRS-Normal operating mode

GADG0612160922PS

#### 2.1 V<sub>diff</sub> steps

When "adaptive hysteresis current" is selected, the peak detector in the VRS block identifies the peak value of the input differential voltage ( $V_{diff}$  = FLW IN P - FLW IN N) and sets the hysteresis current consequently.

Instead, when the "manual hysteresis current" is selected, hysteresis current is user defined.

The hysteresis current is applied to avoid spurious commutation of the zero-crossing comparator that senses the FLW\_IN\_P - FLW\_IN\_N signal.

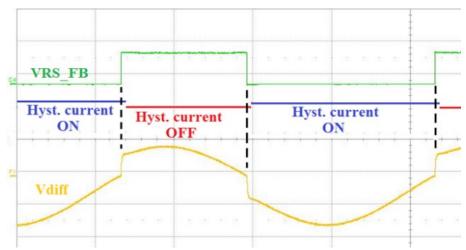

The hysteresis current is switched ON or OFF depending on the value of the zero-crossing comparator:

- If the output of the zero-crossing comparator is high, the hysteresis current is kept OFF

- If the output of the zero-crossing comparator is low, the hysteresis current is switched ON

This approach applies the hysteresis current only on the transition H-L of the VRS\_FB signal.

When the hysteresis current is on, it generates a voltage drop across the external resistors.

Next considerations are based on the 10 k $\Omega$  in series to FLW\_IN\_P and 10 k $\Omega$  FLW\_IN\_N pins.

The turning ON or OFF of the hysteresis current determines the steps of the input differential signal  $(V_{diff} = FLW_IN_P - FLW_IN_N)$  in correspondence of each zero-crossing.

This is visible in the Figure 3:

AN6023 - Rev 1 page 3/18

Figure 3. VRS-Steps in input differential signal

- If the hysteresis current is small, steps in V<sub>diff</sub> (= FLW\_IN\_P FLW\_IN\_N) are small

- If the hysteresis current is large, steps in V<sub>diff</sub> (= FLW\_IN\_P FLW\_IN\_N) are large

The VRS block senses the input differential voltage ( $V_{diff} = FLW_IN_P - FLW_IN_N$ ) and FLW\_OUT toggles on the  $V_{diff}$  zero-crossing.

The output of the zero-crossing comparator can be further processed by a filtering circuit or directly routed to FLW\_OUT.

#### 2.2 VRS clamp

Sensor signal range can be very wide, up to  $\pm 200$  V. These signals reported to the L9788 VRS input pins, shall be limited within the specified voltage AMR to prevent damage on the internal receiver structure. For these reasons VRS inputs are internally clamped in the range [ $V_{clpH}-V_{clpL}$ ]; current has to be externally limited as depicted in the specification. Sensor input pins have the common-mode VCM input, internally set for proper operation.

This allows the input differential signal to be processed that is V<sub>diff</sub> = FLW\_IN\_P - FLW\_IN\_N.

Current flowing through FLW\_IN\_P - FLW\_IN\_N has to be limited inside the absolute values, as reported in the specification. When the amplitude of the input signals overcomes the clamp values (FLW\_IN\_x <  $V_{clpL}$  and FLW\_IN\_y >  $V_{clpH}$ ), FLW\_IN\_P, FLW\_IN\_N and VCM reduce their value, refer to the Figure 4, Figure 5, and Figure 6.

The VRS block still senses the input differential signal and sets FLW\_OUT accordingly.

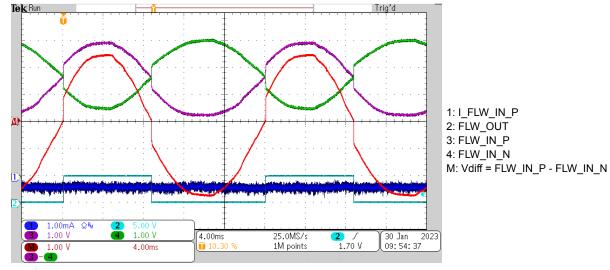

As an example:

- VRS\_MODE[1:0] = 00 (manual hysteresis current no filter time)

- VRS HYST[2:0] = 101 (high hysteresis current)

AN6023 - Rev 1 page 4/18

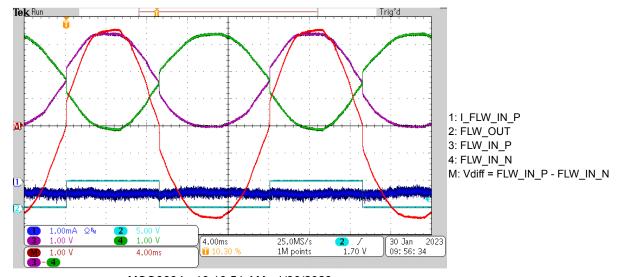

Figure 4. VRS-Manual HI5\_small input signal

MSO3034 - 10:08:54 AM 1/30/2023

Note: Evidence of wide steps on  $V_{diff}$  0 V crossing due to the high hysteresis current set and no clamps in FLW\_IN\_x. Increasing the amplitude of the VRS sensor, cuts on the positive waveform of FLW\_IN\_P and  $V_{diff}$  (refer to Figure 5) are evident, as the steps on  $V_{diff}$  0 V crossing.

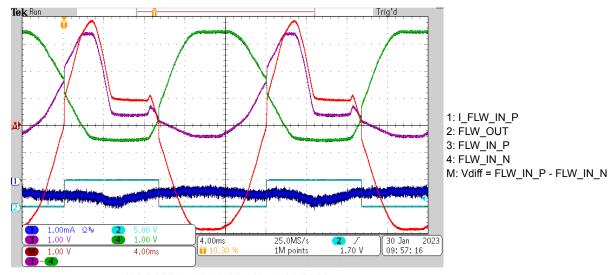

Figure 5. VRS-Manual HI5, FLW\_IN\_P at clampH

MSO3034 - 10:10:51 AM 1/30/2023

Increasing again the amplitude of the VRS sensor, positive FLW\_IN\_P and  $V_{diff}$  signals are reduced. Negative FLW\_IN\_N is cut at clampL and  $V_{diff}$  is cut consequently. This is due to the current in the ESD network limited to the AMR shown in the specification ( $\pm 200$  mA, refer to Figure 5), and the VCM is reduced accordingly.

AN6023 - Rev 1 page 5/18

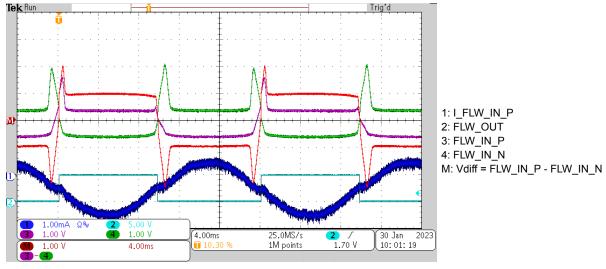

Figure 6. VRS-Manual HI5 and FLW\_IN\_N at clampL

MSO3034 - 10:11:33 AM 1/30/2023

A further increase of the VRS amplitude signal, determines the reduction of FLW\_IN\_P, FLW\_IN\_N, and VCM, due to the current in the ESD network, refer to Figure 7

Figure 7. VRS-Manual HI5, fading of FLW\_IN\_P, FLW\_IN\_N, and VCM

MSO3034 - 10:15:35 AM 1/30/2023

In all the cases mentioned above,  $FLW_OUT$  follows the input differential voltage ( $V_{diff} = FLW_IN_P - FLW_IN_N$ ) as expected, so the VRS signal is properly processed.

AN6023 - Rev 1 page 6/18

#### 2.3 VRS normal mode configurations

The L9788 integrates two main configurable modes: VRS\_A and VRS\_B. These modes are selected in the VRS register, VRS\_MODE\_SEL bit in CONFIG\_REG2.

Once VRS\_A (VRS\_MODE\_SEL = 1) or VRS\_B (VRS\_MODE\_SEL = 0) has been configured, the hysteresis and filtering strategy are defined through the VRS\_MODE[1:0] bit in the same CONFIG\_REG8 register:

- VRS\_MODE[1] defines a filtering function (OFF/ON and if ON, its time value)

- VRS\_MODE[0] defines the hysteresis (manual or adaptive)

The Table 1 and Table 2 summarize the parameters of the VRS\_A and VRS\_B modes; the next paragraphs detail the two configurations.

| VRS_MODE_SEL<br>(A config.) | VRS_MODE[1:0] | Filter |           |               | Hysteresis                                                              |

|-----------------------------|---------------|--------|-----------|---------------|-------------------------------------------------------------------------|

| 1                           | 00            | OFF    | 0 µs      | Manual        | Refer to:<br>VRS_A manual hysteresis                                    |

| 1                           | 01            | OFF    | 0 μs      | Full adaptive | Refer to:<br>VRS_A fully adaptive hysteresis                            |

| 1                           | 10            | ON     | T(n-1)/32 | Manual        | Refer to:  VRS_A manual hysteresis,  VRS_A adaptive filter time         |

| 1                           | 11            | ON     | T(n-1)/32 | Full adaptive | Refer to:  VRS_A fully adaptive hysteresis,  VRS_A adaptive filter time |

Table 1. VRS\_A hysteresis and filter time definition

Table 2. VRS\_B hysteresis and filter time definition

| VRS_MODE_SEL<br>(B config.) | VRS_MODE[1:0] | Fil | ter     | Hysteresis       |                                                |             |                          |

|-----------------------------|---------------|-----|---------|------------------|------------------------------------------------|-------------|--------------------------|

| 0                           | 00            | OFF | 0 µs    | Manual           | Refer to:<br>VRS_B manual hysteresis           |             |                          |

| 0                           | 01            | OFF | 0 µs    | Limited adaptive | Refer to:<br>VRS_B limited adaptive hysteresis |             |                          |

|                             |               |     |         |                  | Refer to:                                      |             |                          |

| 0                           | 10            | ON  | ON      | ON               | 4 µs                                           | 4 μs Manual | VRS_B manual hysteresis, |

|                             |               |     |         |                  |                                                |             |                          |

|                             |               |     |         |                  | Refer to:                                      |             |                          |

| 0                           | 11            | ON  | ON 4 µs | Limited adaptive | VRS_B limited adaptive hysteresis,             |             |                          |

|                             |               |     |         |                  | VRS_B fixed filter time                        |             |                          |

In case a change of the VRS\_MODE\_SEL bit within the normal operating mode occurs (1  $\rightarrow$  0 or 0  $\rightarrow$  1) with hysteresis current active, this leads to the change of the hysteresis (to HI1 or HI3 –default values–, according to the new selection programmed) not synchronized with any VRS\_FB zero-crossing.

#### 2.4 VRS\_A manual hysteresis

To set the manual hysteresis on VRS\_A configuration, bit VRS\_MODE[0] has to be configured at '0'. The hysteresis value is manually set through the VRS\_HYST[2:0] of CONFIG\_REG8 according to Table 3. Such hysteresis is fixed until a new programming frame occurs.

The default hysteresis current after exiting reset is HI3.

A new current value set through the MSC interface is updated during the HYST CURRENT OFF phase that means that the output comparator is high.

AN6023 - Rev 1 page 7/18

| Table 3. | VRS_A | hysteresis | values |

|----------|-------|------------|--------|

|----------|-------|------------|--------|

| Hysteresis current [HI] | Value |      |      | Unit  | Correspondent value on | Unit |  |

|-------------------------|-------|------|------|-------|------------------------|------|--|

| nysteresis current [mj  | Min.  | Тур. | Max. | Oilit | 20 kΩ ext. resistor    | Onne |  |

| HI1                     | 3     | 5    | 7    | μA    | 100                    | mV   |  |

| HI2                     | 7.5   | 10   | 13.5 | μA    | 200                    | mV   |  |

| HI3                     | 13    | 17   | 23   | μA    | 347                    | mV   |  |

| HI4                     | 23    | 32   | 40   | μA    | 644                    | mV   |  |

| HI5                     | 35    | 51   | 60   | μA    | 1020                   | mV   |  |

| No hyst.                |       |      |      |       |                        |      |  |

#### 2.5 VRS A fully adaptive hysteresis

To set the adaptive hysteresis on the VRS A configuration, the VRS MODE[0] bit has to be set to '1'.

In this configuration, VRS input differential signal is fed into a peak detector circuit and then it is quantized on 5 different voltage levels, based on 4 PVi thresholds (see Table 4). The default hysteresis current after exiting reset is HI3.

Table 4. Peak voltage value ranges

| Peak voltage [PVi] | Min. | Тур. | Max. | Unit |

|--------------------|------|------|------|------|

| PV1                | 600  | 930  | 1300 | mV   |

| PV2                | 1200 | 1600 | 1950 | mV   |

| PV3                | 2000 | 2300 | 2650 | mV   |

| PV4                | 2600 | 3000 | 3300 | mV   |

The quantized output is sent to a logic block (hysteresis selection Table) that chooses the proper hysteresis value HIi depending on the input peak voltage (PVi), see Table 5.

Table 5. Peak voltage range correspondence with hysteresis selection

| Input peak voltage range | Selected hysteresis (Hli) |

|--------------------------|---------------------------|

| 0-PV1                    | ни                        |

| PV1–PV2                  | HI2                       |

| PV2-PV3                  | HI3                       |

| PV3-PV4                  | HI4                       |

| > PV4                    | HI5                       |

Peak detector and hysteresis selection table circuits are enabled by the VRS\_FB signal according to the HYS\_FB\_SEL bit in the CONFIG\_REG8 register.

This bit defines if the feedback signal is before (HYS\_FB\_SEL=0) or after (HYS\_FB\_SEL=1) the filter time. VRS input differential voltage is continuously acquired.

During the time frame with the VRS\_FB signal asserted (that corresponds to the hysteresis current HI OFF), the maximum value of  $V_{diff}$  is reached.

This maximum value of  $V_{diff}$  is latched through the peak detector and the peak detector defines the appropriate hysteresis current HIi.

When VRS\_FB falls down crossing 0V, the hysteresis current is turned ON immediately or with a delay depending on the MASK\_TIME or FILTER\_TIME selection.

Based on the hysteresis current, the signal is processed by a squaring circuit, which processes the output signal of the comparator, see Figure 8.

AN6023 - Rev 1 page 8/18

Figure 8. VRS A fully adaptive hysteresis

GADG0612161130PS

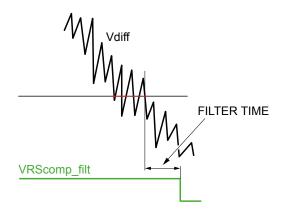

#### 2.6 VRS A adaptive filter time

In VRS\_A mode, it is possible to enable the filter time on the output of the zero-crossing comparator through the bit VRS\_MODE[1] of CONFIG\_REG8.

Once enabled, the most suitable internal filter based on the input signal frequency is determined.

According to the previous period of VRS, the filter time value is updated as per the following:

$$Tfilter_{(n)} = \frac{Tperiod_{(n-1)}}{32}$$

If the value of the previous period is longer than 128  $\mu$ s, the filter time would be saturated at 4  $\mu$ s fixed value. After reset T<sub>filter</sub> = 200  $\mu$ s (typ.)

Through the EN\_FALLING\_FILT bit in the CONFIG\_REG8 register, it is possible to configure two different strategies for the filtering algorithm:

- 1. VRS\_OUT rising edge: the transition depends on the hysteresis crossing of the differential signal V<sub>diff</sub>; VRS output is set if V<sub>diff</sub> remains asserted and stable for a period longer than T<sub>filter</sub>.

- 2. VRS OUT falling edge: the transition depends on the zero-crossing of the differential signal  $V_{\text{diff}}$ :

- EN\_FALLING\_FILT = 1: VRS\_OUT is deasserted when the differential signal V<sub>diff</sub> is low and remains stable for at least T<sub>filter</sub> time (see Figure 9).

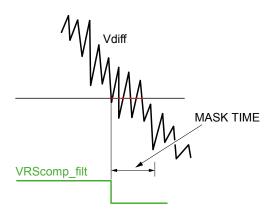

- EN\_FALLING\_FILT = 0: VRS\_OUT is deasserted at the first zero-crossing transition of the differential signal and the next eventual commutations are ignored for T<sub>filter</sub> time (see Figure 10).

AN6023 - Rev 1 page 9/18

Figure 9. EN\_FALLING\_FILT = 1

GADG0612161235PS

Figure 10. EN\_FALLING\_FILT = 0

GADG0612161240PS

#### 2.7 VRS\_B manual hysteresis

To define the manual hysteresis on VRS\_B configuration, bit VRS\_MODE [0] is set to '0'. Hysteresis value is manually selected through VRS\_HYST [2:0] of CONFIG\_REG8 according to Table 6. Such hysteresis is fixed until a new MSC programming occurs.

Table 6. VRS\_B hysteresis values

| Hyptoropic ourrent [HI] | Value |      |      | Unit  | Correspondent value on | Unit  |  |

|-------------------------|-------|------|------|-------|------------------------|-------|--|

| Hysteresis current [HI] | Min.  | Тур. | Max. | Oilit | 20 kΩ ext. resistor    | Oilit |  |

| HI1                     | 3     | 5    | 7    | μA    | 100                    | mV    |  |

| HI2                     | 7.5   | 10   | 13.5 | μA    | 200                    | mV    |  |

| HI3                     | 13    | 17   | 23   | μA    | 347                    | mV    |  |

| HI4                     | 23    | 32   | 40   | μA    | 644                    | mV    |  |

| HI5                     | 35    | 51   | 60   | μA    | 1020                   | mV    |  |

| No hyst.                |       |      |      |       |                        |       |  |

Once a new value is defined, a new hysteresis threshold is applied after the second VRS\_FB H-L transition and until the next rising edge of the VRS input differential voltage occurs.

AN6023 - Rev 1 page 10/18

#### 2.8 VRS\_B limited adaptive hysteresis

To set the limited adaptive hysteresis on the VRS\_B configuration, bit VRS\_MODE [0] has to be configured at '1'. In this mode, the user programs a hysteresis threshold through the VRS\_HYST [2:0] bit in the VRS register and the internal logic selects a hysteresis based on the input signal peak value: the maximum of these two values is actually applied.

Once a new value is defined, a new hysteresis threshold is applied after the second VRS\_FB H-L transition and until the next rising edge of the VRS input differential voltage occurs.

#### 2.9 VRS B fixed filter time

In the VRS\_B configuration, it is possible to enable the filter time on the output of the zero-crossing comparator through the bit VRS\_MODE[1] of the VRS register. This configuration allows defining the internal filter time at a fixed value of 4  $\mu$ s, active on both rising and falling edges of VRS output.

As per the VRS\_A architecture, EN\_FALLING\_FILT allows configuring the same two different strategies for the filtering algorithm.

AN6023 - Rev 1 page 11/18

### 3 VRS-Diagnostic mode

The diagnostic mode is selected through VRS\_DIAG = '1' in CONFIG\_REG8. This mode provides feedback to detect faulty conditions either on FLW IN P or FLW IN N.

To be noted that diagnostic results are not reliable while the flying wheel is rotating.

If a fault is detected in DIAG mode, the VRS correct functionality is not ensured. Fault bit VRS\_DIAG of the VRS register is consequently set.

The Figure 11 shows the circuit used in diagnostic mode. When VRS diagnostic mode is activated, FLW\_IN\_P is fixed at Vcm\_DIAG and I\_DIAG current generator is enabled, so the current path is the one in green.

VRS\_DIAG=1 Vcm\_DIAG 100 kO FLW\_OUT VPS SENSOR VRS\_CONF\_ MODE\_1 100 kΩ 10 kΩ FLW\_IN\_N VRS\_HYST\_FB DIAG LIMITED / FULLY ADAPTIVE HYSTERESIS SELECTOR MSC MANUAL VRS\_FB

Figure 11. VRS block diagram-Diagnostic operating mode-Current path

GADG0612161457PS

AN6023 - Rev 1 page 12/18

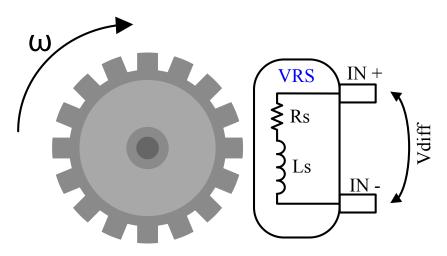

### 4 Application circuit

Sensor sketch and parameters are reported in the Figure 12.

Figure 12. VRS sensor sketch

GAPGPS00571

Table 7. VRS sensor parameters

| Symbol            | Parameter             | Min. | Тур. | Max. | Unit |

|-------------------|-----------------------|------|------|------|------|

| R <sub>s</sub>    | Sensor resistance     | 300  | 600  | 1000 | Ω    |

| L <sub>s</sub>    | Sensor inductor       | -    | 250  |      | mH   |

| V <sub>diff</sub> | Sensor output voltage | -200 |      | +200 | V    |

| T <sub>out</sub>  | Output period         | 100  |      | 5000 | μs   |

The interface handles signals coming from magnetic pick-up sensors. The interface feeds the digital signal to the microcontroller that extracts flying wheel rotational position, angular speed and acceleration.

AN6023 - Rev 1 page 13/18

### **Revision history**

Table 8. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 19-Dec-2023 | 1        | Initial release. |

AN6023 - Rev 1 page 14/18

### **Contents**

| 1  | VRS    | S interface detailed explanation  | 2  |

|----|--------|-----------------------------------|----|

| 2  |        | S–Normal mode                     |    |

|    | 2.1    | V <sub>diff</sub> steps           |    |

|    | 2.2    | VRS clamp                         |    |

|    | 2.3    | VRS normal mode configurations    |    |

|    | 2.4    | VRS_A manual hysteresis           | 7  |

|    | 2.5    | VRS_A fully adaptive hysteresis   | 8  |

|    | 2.6    | VRS_A adaptive filter time        |    |

|    | 2.7    | VRS_B manual hysteresis           | 10 |

|    | 2.8    | VRS_B limited adaptive hysteresis | 11 |

|    | 2.9    | VRS_B fixed filter time           |    |

| 3  | VRS    | S–Diagnostic mode                 | 12 |

| 4  | App    | olication circuit                 | 13 |

| Re | vision | history                           | 14 |

### **List of tables**

| Table 1. | VRS_A hysteresis and filter time definition                 | . 7 |

|----------|-------------------------------------------------------------|-----|

| Table 2. | VRS_B hysteresis and filter time definition                 | . 7 |

| Table 3. | VRS_A hysteresis values                                     | . 8 |

|          | Peak voltage value ranges                                   |     |

|          | Peak voltage range correspondence with hysteresis selection |     |

|          | VRS_B hysteresis values                                     |     |

|          | VRS sensor parameters                                       |     |

|          | Document revision history                                   |     |

AN6023 - Rev 1 page 16/18

# **List of figures**

| Figure 1.  | VRS interface block diagram                              | 2  |

|------------|----------------------------------------------------------|----|

| Figure 2.  | VRS–Normal operating mode                                | 3  |

| Figure 3.  | VRS–Steps in input differential signal                   | 4  |

| Figure 4.  | VRS-Manual HI5_small input signal                        | 5  |

| Figure 5.  | VRS-Manual HI5, FLW_IN_P at clampH                       | 5  |

| Figure 6.  | VRS-Manual HI5 and FLW_IN_N at clampL                    | 6  |

| Figure 7.  | VRS–Manual HI5, fading of FLW_IN_P, FLW_IN_N, and VCM    | 6  |

| Figure 8.  | VRS_A fully adaptive hysteresis                          | 9  |

| Figure 9.  | EN_FALLING_FILT = 1                                      | 10 |

| Figure 10. | EN_FALLING_FILT = 0                                      | 10 |

| Figure 11. | VRS block diagram–Diagnostic operating mode–Current path | 12 |

| Figure 12. | VRS sensor sketch                                        | 13 |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

AN6023 - Rev 1 page 18/18