## Migrating from STM32H730 and STM32H750 to STM32H7Rx/7Sx MCUs

#### Introduction

Designers of STM32 microcontroller applications must be able to easily replace one microcontroller type by another in the same product family or products from a different family.

Migrating an application to a different microcontroller is often needed when product requirements grow, putting extra demands on memory size, or increasing the number of I/Os. The objective of cost reduction may also be an argument to switch to smaller components and shrink the PCB area.

This application note analyzes the steps required to migrate from an existing design based on the STM32H730 or STM32H750 MCUs, to the STM32H7Rx/7Sx MCUs.

This document lists the full set of features available for the STM32H730 and STM32H750 devices, and the equivalent features on the STM32H7Rx/7Sx devices. This application note also provides a guideline on both hardware and peripheral migration.

To fully benefit from this application note, the user must be familiar with the STM32 microcontroller family. This application note is a complement to the STM32H730, STM32H750, and STM32H7Rx/7Sx datasheets and reference manuals. For additional information, refer to the product datasheets and reference manuals.

Table 1. Applicable products

| Туре             | Part numbers               |  |  |

|------------------|----------------------------|--|--|

| Microcontrollers | STM32H730 value line       |  |  |

|                  | STM32H750 value line       |  |  |

|                  | STM32H7R7/7S7 product line |  |  |

|                  | STM32H7R3/7S3 product line |  |  |

## 1 General information

The STM32H730, STM32H750, and STM32H7Rx/7Sx MCUs are STM32 32-bit devices based on Arm<sup>®</sup> Cortex<sup>®</sup> processors.

Note: Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

#### **Reference documents**

- [1] Reference manual STM32H7Rx/7Sx Arm®-based 32-bit MCUs (RM0477)

- [2] Reference manual STM32H723/733, STM32H725/735 and STM32H730 Value line advanced Arm®-based 32-bit MCUs (RM0468)

- [3] Reference manual STM32H742, STM32H743/753 and STM32H750 Value line advanced Arm®-based 32-bit MCUs (RM0433)

- [4] Datasheet Arm® Cortex®-M7 32b 550 MHz MCU, 128 KB Flash, 564 KB RAM, Ethernet, USB, 3 × FD-CAN, Graphics, 2 × 16b ADCs, crypto/hash (DS13315)

- [5] Datasheet Arm®Cortex®-M7 32-bit 480 MHz MCUs, 128 Kbyte flash, 1 Mbyte RAM, 46 com. and analog interfaces, crypto (DS12556)

- [6] Datasheet Arm®Cortex®-M7 32-bit 600 MHz MCU, 64 KB flash, 620 KB RAM, Ethernet, 2x USB, 2x FD-CAN, advanced graphics and security, 2x 12-bit ADCs (DS14359)

- [7] Datasheet Arm®Cortex®-M7 32-bit 600 MHz MCU, 64 KB flash, 620 KB RAM, Ethernet, 2x USB, 2x FD-CAN, advanced graphics, 2x 12-bit ADCs (DS14360)

AN5996 - Rev 3 page 2/42

## 2 STM32H7Rx/7Sx MCUs overview

The STM32H7Rx/7Sx devices offer extra performance compared to the STM32H730, and the STM32H750 devices without additional complexity.

The STM32H7Rx/7Sx devices, as Cortex<sup>®</sup>-M7 variants, are compatible with the STM32H7 series devices (for the common packages). This compatibility allows customers to easily migrate from STM32H7Rx/7Sx to STM32H730 and STM32H750 devices, and benefit from their significantly higher performance and their advanced peripherals.

The STM32H7Rx/7Sx devices include a larger set of peripherals with advanced features and optimized power consumption compared to the STM32H730 and STM32H750 devices.

Some of the improved peripherals for the STM32H7Rx/7Sx are:

- Advanced security features

- Life cycle support (HDPL0/1/2)

- Root of trust (ST-iROT)

- Debug authentication

- Secure firmware install (SFI)

- Root secure service (RSS)

- HASH processor (HASH)

- Cryptographic processor (CRYP)

- Memory cipher engine (MCE): on-the-fly encryption/decryption (MCE) for OCTOSPI/Hexa-SPI or FMC external memory

- True random generator (TRNG)

- Public key accelerator (PKA)

- Secure AES coprocessor (SAES)

- Advanced graphic peripherals

- NeoChrom graphic processor (GPU2D) accelerating any angle rotation, scaling, and perspective correct texture mapping

- Digital camera interface (DCMIPP)

- Chrom-GRC (GFXMMU)

- External memories:

- Two XSPI memory interfaces to support:

- One or two OCTOSPI memories, quad memory

- One OCTOSPI and one 16-bit SPI memory

- Advanced communication interface

- Improved inter-integrated circuit (I3C)

- USB Type-C® connector/USB power delivery interface (UCPD)

- USB OTG full-speed controller with embedded PHY

- USB OTG high-speed controller with embedded PHY

- Performance

- Frequency up to 600 MHz

- Power supply

Note:

- Dedicated external supply inputs for XSPI and USB to allow independent multiple voltage constraints and greater power supply choice

- Embedded automatic voltage scaling (AVS) mechanism to ensure that the maximum frequency is reached with the minimum power consumption

This document only manages the differences between STM32H730, STM32H750, and STM32H7Rx/7Sx for the common features. The new features of STM32H7Rx/7Sx are more detailed in the reference manual RM0477. The detailed list of available features and packages for each product is available in the respective product datasheet.

Table 2 summarizes the security and graphic IPs availability between STM32H7R3x8, STM32H7R3x8, STM32H7R7x8, and STM32H7R7x8 devices. For more details, refer to each device datasheet.

AN5996 - Rev 3 page 3/42

Table 2. Security and graphics IP availability per product line

| IP type  |                                        | STM32H7R3 | STM32H7R7 | STM32H7S3 | STM32H7S7 |  |  |

|----------|----------------------------------------|-----------|-----------|-----------|-----------|--|--|

|          | Neo-Chrom (GPU2D)                      | N         | Y         | N         | Y         |  |  |

|          | Chrom-ART (DMA2D)                      |           | Υ         |           |           |  |  |

| Craphica | Chrom-GRC (GFXMMU)                     |           | `         | <b>′</b>  |           |  |  |

| Graphics | Hardware codec (JPEG)                  |           | `         | <b>Y</b>  |           |  |  |

|          | LCD-TFT                                | N         | Y         | N         | Y         |  |  |

|          | Parallel display (FMC8/16)             |           | `         | Υ         |           |  |  |

|          | Life cycle support (HDPL0/1/2)         |           | `         | <b>Y</b>  |           |  |  |

|          | Root of trust (ST-iROT)                | N         | N         | Y         | Y         |  |  |

|          | Debug authentication                   |           | `         | 7         |           |  |  |

|          | Secure firmware install (SFI)          | Y         |           |           |           |  |  |

|          | Root secure service (RSS)              | Y         |           |           |           |  |  |

| Security | HASH accelerator and PKA verification  |           | `         | <b>Y</b>  |           |  |  |

|          | Crypto processor (Crypt, PKA, SAES)    | N         | N         | Y         | Y         |  |  |

|          | On-the-fly encryption/decryption (MCE) | N         | N         | Y         | Y         |  |  |

|          | True random generator (RNG)            | Υ         |           |           |           |  |  |

AN5996 - Rev 3 page 4/42

## 3 System architecture differences between STM32H7Rx/7Sx, STM32H730, and STM32H750 devices

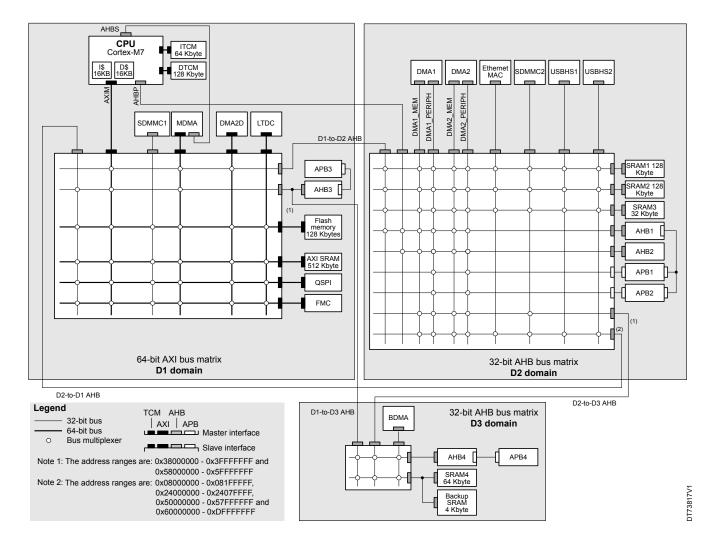

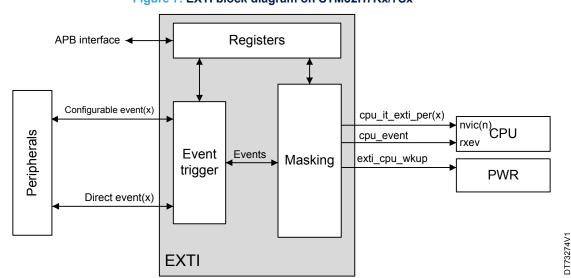

The STM32H7Rx/7Sx architecture features a 64-bit AXI and 32-bit multilayer AHB bus matrix, and bus bridges that allow interconnecting bus masters with bus slaves, as illustrated in Figure 1.

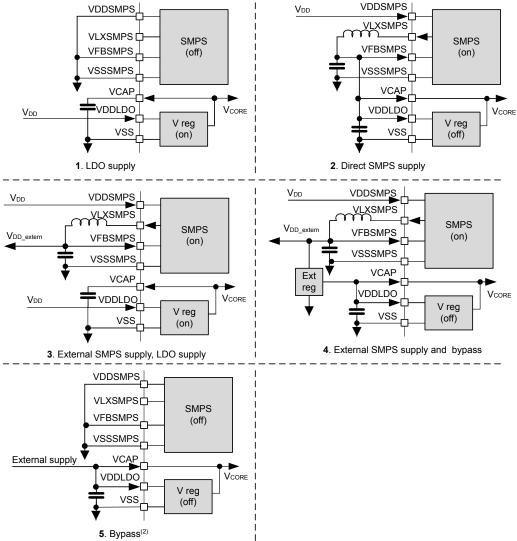

In STM32H730 and STM32H750 devices, there are three domains: an AXI bus matrix in D1 domain, and two AHB bus matrices in D2 and D3 domain.

The differences in power modes are addressed in Section 6.2.5.

Table 3, Figure 1, Figure 2, and Figure 3 illustrate the system architecture differences between the STM32H7Rx/7Sx devices, STM32H730, and STM32H750 devices.

Table 3. Available bus matrix on STM32H7Rx/7Sx, STM32H730, and STM32H750 devices

| Device                  | AHB bus matrix | AXI bus matrix |

|-------------------------|----------------|----------------|

| STM32H7Rx/7Sx           | 1              | 1              |

| STM32H730 and STM32H750 | 2              | 1              |

AN5996 - Rev 3 page 5/42

AHBS DTCM0 CPU Legend 32/96 Kbytes Bus interfaces Cortex®-M7 DTCM1 AXI - 32-bit bus AHB APB 32/96 Kbytes D\$ \_\_\_\_ ASIB 64-bit bus 32 Kbytes 32 Kbytes AMIB ITCM Bus multiplexer 64/192 Kbytes AHBP AXIM From AHB domain SDMMC1 HPDMA1 DCMIPP DMA2D GFXMMMU LTDC To AHB domain MCE3 FMC MCE1 XSPI1 MCE2 XSPI2 AXI SRAM4 SRAM3 SRAM2 SRAM1 FLASH GPV ETH1 SDMMC2 OTG\_HS GPDMA1 From AHPB AHB1 SRAM1 16 Kbytes SRAM2 16 Kbytes AHB2 AHB AHB3 AHB4 Backup SRAM (4 Kbytes) Reg To AXI AHB5

Figure 1. STM32H7Rx/7Sx devices system architecture

AN5996 - Rev 3 page 6/42

AHBS\_\_ CPU ITCM 64-Kbyte Cortex-M7 OR ■ ITCM 192-Kbyte DMA 1 DMA 2 USBHS1 DTCM 128-Kbyte DMA1\_PERIPH DMA2\_PERIPH DMA2\_MEM AXIM DMA1\_MEM SDMMC 1 MDMA DMA2D LTDC D1-to-D2 AHB AXI SRAM 192-Kbyte SRAM1 16-Kbyte SRAM2 16-Kbyte Flash A 128-Kbyte AHB1 AXI SRAM 128-Kbyte AHB2 OCTOSPI1 OTFDEC2 OCTOSPI2 APB1 FMC APB2 AHB3 APB3 64-bit AXI bus matrix 32-bit AHB bus matrix

D2 domain D1 domain D2-to-D1 AHB D2-to-D3 AHB D1-to-D3 AHB 32-bit AHB bus matrix BDMA D3 domain Legend APB4 TCM AHB

AXI APB

Master interface AHB4 SRAM4 16-Kbyte 32-bit bus DT73271V1 64-bit bus Slave interface o Bus multiplexer Backup SRAM

Figure 2. STM32H730 devices system architecture

AN5996 - Rev 3 page 7/42

Figure 3. STM32H750 devices system architecture

AN5996 - Rev 3 page 8/42

## 4 Hardware migration

## 4.1 Package availability

The available packages on the STM32H7Rx/7Sx, STM32H730, and STM32H750 devices are listed in Table 4. The STM32H730 devices are offered in several packages ranging from 100 to 176 pins/balls. The STM32H7Rx/7Sx devices, on the other hand, are offered in packages ranging from 68 to 225 pins/balls.

The STM32H7Rx/7Sx and STM32H730 devices support the switched-mode power supply (SMPS) step-down converter available in some specific packages, which are not pinout compatible with the legacy packages. See Table 4.

The STM32H750 devices are offered in three packages ranging from 100 pins to 240 pins/balls and support only LDO option supply.

For more details on the pinout, refer to the product datasheets.

Table 4. Available packages on STM32H7Rx/7Sx, STM32H730, and STM32H750 devices

| Package               | STM32H750 | STM32H730 | STM32H7Rx/7Sx               | Regulator                     |  |

|-----------------------|-----------|-----------|-----------------------------|-------------------------------|--|

| LQFP100               | Х         | X         | X <sup>(1)</sup>            |                               |  |

| TFBGA100              | NA        | X         | NA                          |                               |  |

| LQFP144               | Х         | X         | X <sup>(1)</sup>            |                               |  |

| UFBGA144              | NA        | X         | NA                          | LDO <sup>(3)</sup>            |  |

| LQFP176               | Х         | NA        | NA                          | LDO                           |  |

| UFBGA176+25           | X         | NA        | NA                          |                               |  |

| TFBGA240+25           | Х         | NA        | NA                          |                               |  |

| VFQFPN68              | NA        | NA        | X <sup>(1)</sup>            |                               |  |

| UFBGA169 SMPS         | NA        | X         | X <sup>(1)(2)</sup>         |                               |  |

| UFBGA176+25 SMPS      | NA        | X         | X <sup>(1)(2)</sup>         |                               |  |

| LQFP176 SMPS          | NA        | X         | X <sup>(1)(2)</sup>         |                               |  |

| TFBGA100 SMPS         | NA        | NA        | X <sup>(1)</sup>            |                               |  |

| UFBGA144 SMPS         | NA        | NA        | X <sup>(1)(2)</sup>         | LDO/SMPS/<br>regulator bypass |  |

| WLCSP SMPS            | NA        | NA        | X <sup>(1)</sup> (WLCSP101) | regulator bypass              |  |

| TFBGA225 HEXA<br>SMPS | NA        | NA        | X <sup>(1)(2)</sup>         | -                             |  |

| TFBGA225 OCTO<br>SMPS | NA        | NA        | X <sup>(1)(2)</sup>         |                               |  |

- 1. GP device package

- 2. GFx device package

- 3. The STM32H750 devices can be used in regulator bypass mode.

## 4.2 Pinout compatibility

The STM32H7Rx/7Sx devices differ from the STM32H730 and STM32H750 devices in terms of MCU port assignment to package terminals, meaning their pinout or ballout is not identical. This holds for all common package types of the package listed in Table 4.

AN5996 - Rev 3 page 9/42

## 5 Boot mode compatibility

#### 5.1 Boot mode selection

In STM32H730 and STM32H750 devices, two different boot spaces can be selected through the BOOT pin and the boot base address programmed in the BOOT ADD0 or BOOT ADD1 option bytes as shown in Table 5.

The  ${\tt BOOT\_ADD0}$  and  ${\tt BOOT\_ADD1}$  address option bytes can program any boot memory address from 0x0000 0000 to 0x3FFF 0000, which includes:

- All flash memory address space.

- All RAM address space: ITCM, DTCM RAMs, and SRAMs.

- The TCM-RAM.

Table 5. Boot modes for STM32H730 and STM32H750

| Boot mode selection |                           |                                                                                                                                |  |

|---------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| BOOT pin            | Boot address option bytes | Boot area                                                                                                                      |  |

| 0                   | BOOT_ADD0[15:0]           | Boot address defined by user option byte BOOT_ADD0[15:0] STMicroelectronics programmed value: flash memory at 0x0800 0000      |  |

| 1                   | BOOT_ADD1[15:0]           | Boot address defined by user option byte BOOT_ADD1[15:0] STMicroelectronics programmed value: system bootloader at 0x1FF0 0000 |  |

For the STM32H7Rx/7Sx devices, the boot memory space is selected by the BOOT pin and the NVSTATE as shown in Table 6. For NVSTATE=OPEN the choice is be made by the BOOT pin. For the NVSTATE=CLOSED, the boot is from the RSS in the system flash

Table 6. Boot modes for STM32H7Rx/7Sx

| Boot mode selection |          | Boot area                                        |  |

|---------------------|----------|--------------------------------------------------|--|

| NVSTATE             | Boot pin | — Boot area                                      |  |

|                     |          | Boot from the user flash memory at 0x0800 0000   |  |

| Open 1              |          | Boot from the bootloader                         |  |

| Closed              | -        | Boot from the RSS in flash memory at 0x1FF0 0080 |  |

## 5.2 System bootloader

The system bootloader is located in the system memory, and programmed by STMicroelectronics during production. The system bootloader permits to reprogram the flash memory using one of the supported serial interfaces. More details are provided in the following table:

Table 7. STM32H7Rx/7Sx, STM32H730, and STM32H750 devices bootloader communication peripherals

| System bootloader peripherals | STM32H750<br>I/O pin                  | STM32H730<br>I/O pin   | STM32H7Rx/7Sx<br>I/O pin              |  |                                       |

|-------------------------------|---------------------------------------|------------------------|---------------------------------------|--|---------------------------------------|

| DFU                           | USB OTG FS (PA11/PA12) in device mode |                        | USB OTG FS (PA11/PA12) in device mode |  | USB OTG FS (PM12/PM11) in device mode |

| USART1                        | PA9/PA10<br>PB14/PB15                 | PA9/PA10               | PA9/PA10                              |  |                                       |

| USART2                        |                                       | PA2/PA3                |                                       |  |                                       |

| USART3                        | PB10/PB11                             | PB10/PB11<br>PD8 / PD9 | PD8/PD9                               |  |                                       |

AN5996 - Rev 3 page 10/42

| System bootloader<br>peripherals | STM32H750<br>I/O pin | STM32H730<br>I/O pin | STM32H7Rx/7Sx<br>I/O pin |

|----------------------------------|----------------------|----------------------|--------------------------|

| UART4                            | N                    | IA                   | PD0/PD1                  |

| I2C1 <sup>(1)</sup>              | PB6                  | /PB9                 | PB8/PB7                  |

| 12C2                             | PF0                  | /PF1                 | PB10/PB11                |

| I2C3                             |                      | PA8/PC9              |                          |

| SPI1                             |                      | PA7/PA6/PA5/PA4      |                          |

| SPI2                             | PI3/PI2/PI1/PI0      | NA                   | PB15/PB14/PB13/PB12      |

| SPI3                             | PC12/PC11            | /PC10/PA15           | PC12/PB4/PB3/PA15        |

| SPI4                             | PE14/PE13            | NA                   |                          |

| FDCANx <sup>(2)</sup>            | NA                   | PH13/PH14<br>PD1/PD0 | PB5/PB1                  |

- 1. Shared with I3C for STM32H7Rx/7Sx

- 2. FDCAN1 (for STM32H730) and FDCAN2 (for STM32H7Rx/7Sx).

AN5996 - Rev 3 page 11/42

## 6 Peripheral migration

## 6.1 Cross-compatibility between STM32 products

The STM32 microcontrollers embed a set of peripherals that can be classified in the following groups:

- Group 1: Peripherals are common to all products.

These peripherals have the same structure, registers, and control bits. There is no need to perform any firmware change to keep the same functionality at the application level after migration.

All the features and behavior remain the same.

- Group 2: These peripherals are shared by all products but may have minor differences to support new

features. The migration from one product to another is relatively easy and does not require significant new

development effort..

- Group 3: Peripherals that have considerable changes from one product to another (for example new architecture or new features). For this group of peripherals, the migration requires a new development at the application level.

Table 8 summarizes the available peripherals in STM32H730 and STM32H750 devices compared to STM32H7Rx/7Sx devices.

All the features and peripherals listed in Table 8 for the STM32H7Rx/7Sx are relative to the package TFBGA225 HEXA SMPS .

Table 8. Peripheral summary for STM32H7Rx/7Sx, STM32H730, and STM32H750 devices

| ٠., | not | avai | ıaı | വമ |

|-----|-----|------|-----|----|

|     |     |      |     |    |

| Peripherals     |                        | STM32H750                   | STM32H730                              | STM32H7Sxx          | STM32H7Rxx               |

|-----------------|------------------------|-----------------------------|----------------------------------------|---------------------|--------------------------|

| Maximum CP      | U frequency            | 480 MHz                     | 550 MHz 600 MHz                        |                     |                          |

| MPU region n    | MPU region number      |                             |                                        | 16                  |                          |

| Data cache (K   | (bytes)                | 16                          | 32                                     | 32                  |                          |

| Instruction cad | che (Kbytes)           | 16                          | 32                                     | 32                  |                          |

| User flash me   | mory (Kbytes)          | 128 Kbytes                  | 128 Kbytes                             | 64 Kby              | tes                      |

| SRAMs (Kbyte    | es)                    | 864                         | Up to 368 <sup>(1)</sup>               | Up to 48            | 38 <sup>(2)</sup>        |

| TCM RAM         | ITCM                   | 64                          | Up to 256 <sup>(1)</sup>               | Up to 19            | <b>32</b> <sup>(2)</sup> |

| (Kbytes)        | DTCM                   | 128                         | 128                                    | Up to 19            | )2 <sup>(2)</sup>        |

| Backup SRAM     | // (Kbytes)            | 4                           | 4                                      | 4                   |                          |

| FMC             |                        | 1                           | 1                                      |                     |                          |

| External        | SDMMC                  | 2                           | 2                                      |                     |                          |

| memories        | XSPI                   | 1 Quad-SPI interface        | 2 OCTOSPI interfaces 2 XSPI interfaces |                     | erfaces                  |

|                 | High resolution        | 8 (16 bits)                 |                                        | -                   |                          |

|                 | General purpose        | 8 (16 bits)/<br>2 (32 bits) | 4 (32 bits)/<br>10 (16 bits)           | 4 (32 bi<br>7 (16 b |                          |

|                 | Advanced control (PWM) | 2 (16 bits)                 | 2 (32 bits)                            | 1 (16 b             | its)                     |

|                 | Basic                  | 2 (16 bits)                 | 2 (16 bits)                            |                     |                          |

| Timers          | Low-power              | 5 (16 bits)                 | 5 (16 bits)                            | 5 (16 b             | its)                     |

|                 | GFXTIM                 | -                           | - 1                                    |                     |                          |

|                 | SysTick timer          | 1                           | 1                                      |                     |                          |

|                 | Watchdog               | 2                           |                                        | 2                   |                          |

|                 | RTC                    | 1                           |                                        | 1                   |                          |

AN5996 - Rev 3 page 12/42

|                            | Peripherals                                | STM32H750                                        | STM32H730                 | STM32H7Sxx STM32H7Rxx                                                                                   |  |

|----------------------------|--------------------------------------------|--------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------|--|

|                            | SPI/I2S                                    | 6/3                                              |                           | 6/4                                                                                                     |  |

|                            | I2C                                        | 4                                                | 5                         | 3                                                                                                       |  |

|                            | I3C                                        | -                                                | -                         | 1                                                                                                       |  |

|                            | USART/UART                                 | 4/4                                              | 5/5                       | 3/4                                                                                                     |  |

|                            | LPUART                                     | 1                                                |                           | 1                                                                                                       |  |

|                            | SAI                                        | 4                                                |                           | 2                                                                                                       |  |

|                            | SPDIFRX                                    |                                                  | 4 inputs                  |                                                                                                         |  |

| Communication              | SWPMI                                      | 1                                                |                           | 1                                                                                                       |  |

| interfaces                 | MDIO                                       | 1                                                | 1 1                       |                                                                                                         |  |

|                            | FDCAN/TT-FDCAN                             | 1/1                                              | 2/1                       | 2/-                                                                                                     |  |

|                            | USB OTG FS                                 | 1                                                | -                         | 1                                                                                                       |  |

|                            | USB OTG HS                                 |                                                  | 1(3)                      |                                                                                                         |  |

|                            | UCPD                                       | -                                                | -                         | 1                                                                                                       |  |

|                            | HDMI-CEC                                   | 1                                                |                           | 1                                                                                                       |  |

|                            | DFSDM                                      | Ye                                               | es (8 channels/4 filters) | -                                                                                                       |  |

|                            | ADF                                        | -                                                | -                         | Yes (1 filter)                                                                                          |  |

|                            | Ethernet                                   |                                                  | 1                         |                                                                                                         |  |

| Digital camera             | DCMI                                       | Yes                                              | Yes                       | -                                                                                                       |  |

| interface                  | DCMIPP                                     |                                                  | -                         | Yes                                                                                                     |  |

|                            | PSSI                                       | -                                                | Yes                       |                                                                                                         |  |

|                            | Chrom-ART Accelerator <sup>™</sup> (DMA2D) | Yes                                              |                           |                                                                                                         |  |

|                            | JPEG codec                                 | Yes -                                            |                           | Yes                                                                                                     |  |

| Graphics                   | GFXMMU                                     | -                                                | -                         | Yes                                                                                                     |  |

|                            | ICACHE                                     | -                                                | -                         | Yes <sup>(4)</sup>                                                                                      |  |

|                            | Neo-Chrom (GPU2D)                          | -                                                | -                         | Yes <sup>(4)</sup>                                                                                      |  |

|                            | LCD-TFT                                    |                                                  | Yes                       | Yes <sup>(4)</sup>                                                                                      |  |

| GPIOs                      |                                            | Up to 168                                        | Up to 128                 | Up to 152                                                                                               |  |

| DTS (Digital tem           | nperature sensor)                          | -                                                |                           | 1                                                                                                       |  |

|                            | 12-bit ADC                                 | -                                                | 1 (up to 17 channels)     | 2 (up to 19 channels)                                                                                   |  |

|                            | 16-bit ADC                                 | 3 (up to 36 channels)                            | 2 (up to 20 channels)     | -                                                                                                       |  |

| Analog                     | 12-bit DAC                                 |                                                  | 2                         | -                                                                                                       |  |

| peripheral                 | Operational amplifier                      |                                                  | 2                         | -                                                                                                       |  |

|                            | Ultra-low-power comparator                 |                                                  | 2                         | -                                                                                                       |  |

|                            | Temperature sensor (connected to ADC)      | 1 (ADC3)                                         |                           | 1 (ADC1)                                                                                                |  |

| DMA                        | ,                                          | 4 DMA: 2 dual port DMA, 1 MDMA, 1 BDMA           |                           | 2 dual port DMA: HPDMA, GPDMA                                                                           |  |

| Cryptographic acceleration |                                            | Random number generator (RNG)     HASH processor |                           | <ul> <li>Random number generator<br/>(RNG)</li> <li>HASH processor</li> <li>PKA verification</li> </ul> |  |

|                            |                                            | Cryptographic processor                          |                           | Cryptographic processor                                                                                 |  |

AN5996 - Rev 3 page 13/42

|                            | Peripherals           | STM32H750                                        | STM32H730                                                                                                                                                          | STM32H7Sxx                                      | STM32H7Rxx                                              |  |

|----------------------------|-----------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------|--|

| Cryptographic acceleration |                       |                                                  | -                                                                                                                                                                  |                                                 | -                                                       |  |

|                            |                       | -                                                | 2 × OTFDEC for OCTOSPI memory                                                                                                                                      | 3 × MCE for OCTO/<br>Hexa-SPI memory<br>and FMC |                                                         |  |

|                            |                       | _                                                | ation protection<br>otection (WRP)<br>detection                                                                                                                    |                                                 |                                                         |  |

| Security feature           | Security feature      |                                                  | <ul> <li>Global device readout protection (RDP)</li> <li>Proprietary code readout protection (PC-ROP)</li> <li>Secure access mode: root secure services</li> </ul> |                                                 | e<br>cation<br>mode: root<br>(RSS) and<br>tection (HDP) |  |

|                            |                       | (RSS) ar                                         | (RSS) and secure user memory                                                                                                                                       |                                                 | -                                                       |  |

|                            | Ambient temperatures  | -40° to<br>+85 °C -40° to +125 °C <sup>(5)</sup> |                                                                                                                                                                    | -40° to +8                                      | 35 °C                                                   |  |

| Operating temperatures     | Junction temperatures | -40° to<br>+125 °C<br>VOS0 up to<br>105 °C       | +125 °C<br>VOS0 up to  -40° to +140 °C(°)  VOS1 up to 140 °C  VOS0 up to 140 °C                                                                                    |                                                 | 25 °C<br>to 105 °C                                      |  |

| Operating volta            | ge                    |                                                  | 1.62 to 3.6 V <sup>(7)</sup>                                                                                                                                       |                                                 | 1.71 to 3.6 V                                           |  |

- 1. Includes 192 Kbytes shared between ITCM and AXI.

- 2. Includes 128 Kbytes shared between ITCM and AXISRAM1 and 128 Kbytes shared between DTCM and AXISRAM3 and 72 Kbytes shared between ECC and AXISRAM4.

- 3. USB OTG high-speed interface with full-speed capability.

- 4. Not available in STM32H7R3/S3x8.

- 5. 125 °C can be reached only for part numbers in temperature range 3. For part numbers in temperature range 6, this value must be decreased to 85 °C.

- 6. 140 °C can be reached only for part numbers in temperature range 3. For part numbers in temperature range 6, this value must be decreased to 125 °C.

- 7. V<sub>DD</sub> can drop down to 1.62 V by using an external power supervisor and connecting PDR\_ON pin to VSS. Otherwise, the supply voltage must stay above 1.71 V with the embedded power voltage detector enabled.

## 6.2 System peripherals

### 6.2.1 Embedded flash memory (FLASH)

Table 9 compares the flash memory interface between the STM32H7Rx/7Sx, STM32H730, and STM32H750 devices.

For more information on programming, erasing, and protection, refer to the corresponding product reference manual.

Table 9. Flash memory differences

| Flash memory | STM32H750                                                                    | STM32H730 | STM32H7Rx/7Sx                                   |

|--------------|------------------------------------------------------------------------------|-----------|-------------------------------------------------|

| Main/program | 128 Kbytes  One bank and one sector of 128 Kbytes.                           |           | 64 Kbytes                                       |

| memory       |                                                                              |           | One bank divided in 8 sectors of 8 Kbytes each. |

| Feature      | <ul><li>Programming granularity</li><li>Single flash word write: 2</li></ul> |           | Programming granularity: 128 bits               |

AN5996 - Rev 3 page 14/42

| Flash memory                       | STM32H750                                                                                                                                  | STM32H730                                                                                              | STM32H7Rx/7Sx                                                                                                                                              |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    | <ul> <li>Read operations supporting multiple lengths (64 bits, 32 bits, 16 bits, or one byte)</li> <li>Sector erase, bank erase</li> </ul> |                                                                                                        | Single flash word write: 128-bit granularity Read operations supporting multiple lengths (64 bits, 32 bits, 16 bits, or one byte) Sector erase, bank erase |

| error code correction (ECC)        | <ul> <li>One error detection/corr<br/>per 256-bit.</li> <li>Flash memory word usir</li> </ul>                                              | One error detection/correction or two error detections per 128-bit flash memory word using 9 ECC bits. |                                                                                                                                                            |

| Wait-states                        | Up to four (depending on the core voltage and frequency).                                                                                  | Up to three (depending on the core voltage and frequency).                                             | Up to seven (depending on the core voltage and frequency).                                                                                                 |

| User option bytes                  |                                                                                                                                            | Yes                                                                                                    |                                                                                                                                                            |

| One time programmable (OTP) memory |                                                                                                                                            | -                                                                                                      |                                                                                                                                                            |

|                                    | <ul><li>Configuration protection</li><li>Write protection</li></ul>                                                                        |                                                                                                        |                                                                                                                                                            |

| Protection<br>mechanisms           | Global device readout protection (RDP)     Proprietary code readout protection (PCROP)     Secure access mode areas                        |                                                                                                        | Temporal isolation management (HDPL) Product life cycle management (product state) Secure access mode areas OTP locking                                    |

#### 6.2.2 SRAMs

Table 10 shows the difference of RAM size between STM32H7Rx/7Sx, STM32H730, and STM32H750 devices. All devices feature a RAM ECC monitoring unit (RAMECC). It provides a mean for application software to verify the ECC status and execute service routines when an error occurs.

The RAM ECC monitoring unit includes the following features:

- RAM ECC monitoring per domain

- RAM failing address/data identification

Internal SRAM data are protected by ECC. It supports single-error and double-error detection, as well as single-error correction:

- 7 ECC bits are added per 32-bit word.

- 8 ECC bits are added per 64-bit word.

For STM32H7Rx/7Sx devices, the ECC is enabled/disabled by the user option byte ECC\_ON\_SRAM (refer to Flash memory option byte word 2 status register (FLASH\_OBW2SR) in RM0477 for more details).

AN5996 - Rev 3 page 15/42

Table 10. Comparison of RAM size between STM32H7Rx/7Sx, STM32H730, and STM32H750 devices

|              | Memory                 | STM32H750       | STM32H730                 | STM32H7Rx/7Sx                                 | Units  |

|--------------|------------------------|-----------------|---------------------------|-----------------------------------------------|--------|

| TCM-RAM      | ITCM-RAM (instruction) | 64              | 64 to 256 <sup>(1)</sup>  | 64 to 192 <sup>(2)</sup>                      |        |

| I CIVI-RAIVI | DTCM-RAM (data)        | 128             | 128                       | 64 to 192 <sup>(2)</sup>                      |        |

|              | AXI-SRAM1              | Up to 512       | 128 to 320 <sup>(1)</sup> | 0 to 128 <sup>(2)</sup>                       |        |

|              | AXI-SRAM2              | -               | -                         | 128                                           |        |

| AXI-SRAM     | AXI-SRAM3              | -               | -                         | 0 to 128 <sup>(3)</sup>                       |        |

|              | AXI-SRAM4              | -               | -                         | 0 to 72 <sup>(4)</sup>                        |        |

|              | Total AXI-SRAM         | Up to 512       | Up to 320                 | Up to 456                                     | Kbytes |

|              | SRAM1                  | 128 (D2 domain) | 16 (D2 domain)            | 16                                            | raytes |

|              | SRAM2                  | 128 (D2 domain) | 16 (D2 domain)            | 16                                            |        |

| AHB_SRAM     | SRAM3                  | 32 (D2 domain)  | -                         | -                                             |        |

|              | SRAM4                  | 64 (D3 domain)  | 16 (D3 domain)            | -                                             |        |

|              | Total AHB-SRAM         | 352             | 48                        | 32                                            |        |

| Backup SRAM  |                        |                 | 4                         |                                               |        |

|              | Total                  | 1060            | 564                       | 620                                           |        |

|              | ECC                    | TCM and SRAMs   | TCM and SRAMs             | AXISRAM1,<br>AXISRAM3,<br>BKPSRAM, and<br>TCM | -      |

- 1. Includes 192 Kbytes shared between ITCM and AXI SRAM.

- 2. Includes 128 Kbytes shared between ITCM / AXI SRAM1.

- 3. Includes 128 Kbytes shared between DTCM/AXI-SRAM3.

- 4. 72 Kbytes SRAM shared with ECC.

#### 6.2.3 Direct memory access controller (DMA)

The STM32H7Rx/7Sx, STM32H730 and STM32H750 devices have different DMA architecture and features.

The STM32H730 and STM32H750 DMA controllers are high-speed general-purpose master direct memory access controllers (MDMA), dual-port DMAs with FIFO and request router capabilities, and basic DMA with request router capabilities (BDMA).

The STM32H7Rx/7Sx devices DMA controllers are general-purpose direct memory access controllers (GPDMA), and high-performance direct memory access (HPDMA) with FIFO and linked-listed support.

All the devices also embed a Chrom-ART Accelerator (DMA2D), a specialized DMA dedicated to image manipulation.

Table 11. DMA features

| -                                         | STM32H750/STM32H730                                                                                      |                      | STM32I         | H7Rx/7Sx       |                       |  |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------|----------------|----------------|-----------------------|--|

| Instance                                  | Dual-port DMA                                                                                            | BDMA                 | MDMA           | HPDMA          | GPDMA                 |  |

| Number of instances                       | 2                                                                                                        | 1                    |                |                |                       |  |

| Number of masters                         | Dual AHB master                                                                                          | single AHB<br>master | AXI/AHB master | AXI/AHB master | Dual AHB master       |  |

| Number of channels                        | 8                                                                                                        | 8 16                 |                |                |                       |  |

| Data transfers from source to destination | Peripheral-to-memory, memory-to-peripheral, memory-to-memory and peripheral-to-peripheral data transfers |                      |                |                | al-to-peripheral data |  |

| Privileged/<br>unprivileged support       |                                                                                                          | - Yes                |                |                | ⁄es                   |  |

| Linked-list                               | -                                                                                                        | Yes                  |                |                |                       |  |

AN5996 - Rev 3 page 16/42

## 6.2.4 Reset and clock control (RCC)

The table below presents the main differences related to the RCC (reset and clock controller) between the STM32H7Rx/7Sx, STM32H730, and STM32H750 devices.

Table 12. RCC features

| Sourc                  | e clock | STM32H750                                                                                                            | STM32H730  | STM32H7Rx/7Sx                                                    |  |

|------------------------|---------|----------------------------------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------|--|

|                        | HSI     | 64 MHz                                                                                                               |            |                                                                  |  |

| Internal oscillators   | HSI48   | 48 MHz                                                                                                               |            |                                                                  |  |

| internal oscillators   | CSI     | 4 MHz                                                                                                                |            |                                                                  |  |

|                        | LSI     |                                                                                                                      | 32 KHz     |                                                                  |  |

| External accillaters   | HSE     |                                                                                                                      | 4-50 MHz   |                                                                  |  |

| External oscillators   | LSE     |                                                                                                                      | 32.768 KHz |                                                                  |  |

| PLLs                   |         | VCO frequency range:  VCOH: 192 to 836 MHz  VCOL: 150 to 420 MHz  VCOL: 150 to 420 MHz  VCOL: 150 to 420 MHz         |            | VCO frequency range:  • VCOH: 384 to 1672 MHz before the divider |  |

| AXI and AHB max freque | ency    | 240 MHz                                                                                                              | 275 MHz    | 300 MHz                                                          |  |

| APB max frequency      |         | 120 MHz                                                                                                              | 137.5 MHz  | 150 MHz                                                          |  |

| RTC clock source       |         | LSE, LSI, or HSE/32                                                                                                  |            |                                                                  |  |

| Kernel clock           |         | Independent kernel clock for each IP, allowing frequency scaling without any impact on the communication interfaces. |            |                                                                  |  |

| System clock source    |         | HSI, CSI, HSE, or PLL1                                                                                               |            |                                                                  |  |

| Clock security system  |         | CSS on HSE                                                                                                           |            |                                                                  |  |

| MCO clock source       |         | MCO1 pin (PA8): HSI, LSE, HSE, PLL1, or HSI48 MCO2 pin (PC9): SYSCLK, PLL2, HSE, PLL1, CSI, or LSI                   |            |                                                                  |  |

#### Peripheral clock configuration

The peripheral clocks are the clocks provided by the RCC to the peripherals. Two kinds of clocks are available:

- The bus interface clocks

- The kernel clocks

On STM32H7Rx/7Sx, STM32H730, and STM32H750 devices, the peripherals generally receive:

- One or several bus clocks.

- One or several kernel clocks.

The following table describes an example of peripheral clock distribution for STM32H730, STM32H750 and STM32H7Rx/7Sx devices. For more details about peripheral clock distribution, refer to the peripheral clock distribution summary of the product reference manual.

AN5996 - Rev 3 page 17/42

Table 13. Peripheral clock distribution example

| Peripherals      | STM32H750                                 | STM32H730        | STM32H7Rx/7Sx                                     |

|------------------|-------------------------------------------|------------------|---------------------------------------------------|

| I3C1             | NA                                        | A                | rcc_pclk1 pll3_r_ck hsi_ker_ck csi_ker_ck         |

| FDCAN            | hse_ck pll1_q_ck pll2_q_ck rcc_pclk1      |                  | hse_ker_ck pll1_q_ck pll2_p_ck rcc_pclk1          |

| FMC              | rcc_h<br>pll1_c<br>pll2_r<br>per_         | ı_ck<br>⁻_ck     | rcc_hclk5 pll1_q_ck pll2_r_ck hsi_ker_ck rcc_aclk |

| MCE1, MCE2, MCE3 | N.A.                                      | 4                | rcc_aclk<br>rcc_hclk5                             |

| GPU2D, GFXMMU    | N.A.                                      | 4                | rcc_hclk5<br>rcc_aclk                             |

| DTS              | rcc_p                                     | clk4             | lse_ck<br>rcc_pclk4                               |

| GFXTIM           | NA.                                       | A                | pclk5                                             |

| HASH             | rcc_h                                     | clk2             | rcc_hclk3                                         |

| RNG              | hsi48<br>pll1_c<br>lse_<br>lsi_c<br>rcc_h | 1_ck<br>ck<br>ck | hsi48_ker_ck<br>hclk3                             |

## 6.2.5 Power (PWR)

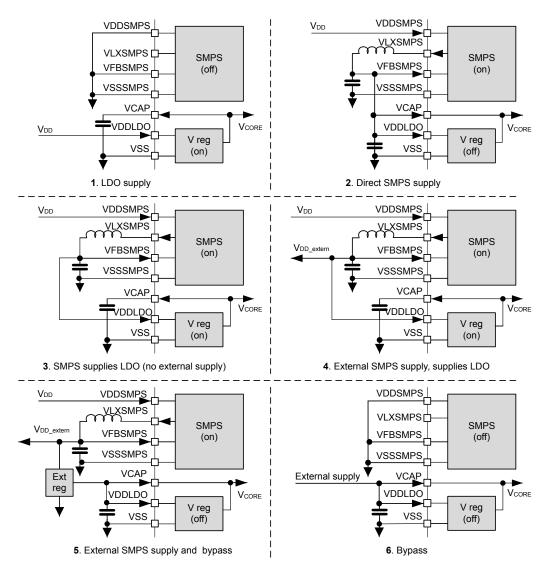

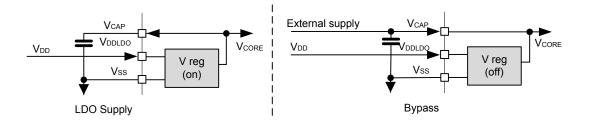

Table 14 presents the PWR controller differences between STM32H750, STM32H730, and STM32H7Rx/7Sx devices. Figure 4, Figure 5, and Figure 6 present the different supply configurations for these devices.

The STM32H7Rx/7Sx uses an automatic voltage scaling (AVS) mechanism which is automatically selected when using an internal power supply. The AVS setting is die dependent, and cannot be modified. All values given in this document are derived and guaranteed for an internal supply with LDO or SMPS only, and not when a bypass mechanism is used.

The STM32H750 devices embed an LDO regulator (LDO) with configurable scalable output to supply the digital circuitry. The different supply configurations is controlled by software at system start-up.

The STM32H7Rx/7Sx and STM32H730 devices embed two regulators: LDO and SMPS to provide the  $V_{CORE}$  supply for digital peripherals, SRAMs (except BKPSRAM), and embedded flash memory. These regulators can provide different voltages (voltage scaling) and can operate in Stop modes.

For the STM32H730 and STM32H7Rx/7Sx devices, there is no dedicated pin that defines if the regulator is in bypass mode or which regulator(s) is/are used. It is done through software at system startup. Both LDO and SMPS regulators are enabled by default during startup and the user software defines if the LDO or the SMPS or both are switched off.

AN5996 - Rev 3 page 18/42

Table 14. PWR controller differences between the STM32H7Rx/7Sx, STM32H730 and STM32H750 devices

|                              | Peripherals                                                                       | <b>S</b>                                                                                                                                                                                                                                                         | STM32H750                                                                                      | STM32H730                                                                                                                                                              | STM32H7Rx/7Sx                                                                                                                               |

|------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Low-power modes              |                                                                                   | <ul> <li>CSleep (CPU clock stopped)</li> <li>CStop (CPU subsystem clock stopped)</li> <li>DStop (domain bus matrix clock stopped)</li> <li>Stop (system clock stopped)</li> <li>DStandby (domain powered down)</li> <li>Standby (system powered down)</li> </ul> |                                                                                                | Sleep (CPU clock stopped and still in Run mode) Stop (system clock stopped) Standby (system powered down)                                                              |                                                                                                                                             |

|                              |                                                                                   | SMPS                                                                                                                                                                                                                                                             | NA                                                                                             | Yes                                                                                                                                                                    | Yes                                                                                                                                         |

| System supply volta          | ngo rogulation                                                                    | LDO                                                                                                                                                                                                                                                              | Yes                                                                                            | Yes                                                                                                                                                                    | Yes                                                                                                                                         |

| System supply voite          | age regulation                                                                    | SMPS supplies LDO                                                                                                                                                                                                                                                | NA                                                                                             | Yes                                                                                                                                                                    | NA                                                                                                                                          |

|                              |                                                                                   | External (bypass)                                                                                                                                                                                                                                                | Yes                                                                                            | Yes                                                                                                                                                                    | Yes                                                                                                                                         |

| Voltage scaling              |                                                                                   | Run mode                                                                                                                                                                                                                                                         | VOS0                                                                                           | to VOS3                                                                                                                                                                | <ul><li>VOS low</li><li>VOS high</li></ul>                                                                                                  |

| voltage scaling              |                                                                                   | Stop mode                                                                                                                                                                                                                                                        | SVOS3                                                                                          | to SVOS5                                                                                                                                                               | <ul><li>SVOS low</li><li>SVOS high</li></ul>                                                                                                |

|                              | External pow                                                                      | er supply for I/Os                                                                                                                                                                                                                                               | V <sub>DD</sub> = 1.                                                                           | 62 to 3.6 V                                                                                                                                                            | V <sub>DD</sub> = 1.71 to 3.6 V                                                                                                             |

|                              | Internal regu<br>V <sub>CORE</sub>                                                | lator (LDO) supplying                                                                                                                                                                                                                                            | V <sub>DDLDO</sub> = 1.62 to 3.6 V                                                             |                                                                                                                                                                        | V <sub>DDLDO</sub> = 1.71 to 3.6 V                                                                                                          |

|                              | Step-down converter (SMPS) supplying V <sub>CORE</sub>                            |                                                                                                                                                                                                                                                                  | NA                                                                                             | <ul> <li>V<sub>DDSMPS</sub> = 1.62 to 3.6 V</li> <li>V<sub>LXSMPS</sub> = V<sub>CORE</sub> or 1.8 V</li> <li>V<sub>FBSMPS</sub> = V<sub>CORE</sub> or 1.8 V</li> </ul> | V <sub>DDSMPS</sub> = 1.71 to 3.6 V<br>V <sub>LXSMPS</sub> = V <sub>CORE</sub> or 1.8 V<br>V <sub>FBSMPS</sub> = V <sub>CORE</sub> or 1.8 V |

|                              | External ana                                                                      | log power supply                                                                                                                                                                                                                                                 | V <sub>DDA</sub> = 1                                                                           | .62 to 3.6 V                                                                                                                                                           | V <sub>DDA</sub> = 1.71 to 3.6 V                                                                                                            |

| Power supplies               | USB power s                                                                       | supply                                                                                                                                                                                                                                                           | $V_{DD33USB} = 3.0 \text{ to } 3.6 \text{ V}$<br>$V_{DD50USB} = 4.0 \text{ to } 5.5 \text{ V}$ |                                                                                                                                                                        | V <sub>DD33USB</sub> = 3.0 to 3.6 V<br>V <sub>DD50USB</sub> = 4.0 to 5.5 V                                                                  |

|                              | Backup dom                                                                        | ain                                                                                                                                                                                                                                                              | V <sub>BAT</sub> = 1.2 to 3.6 V                                                                |                                                                                                                                                                        | V <sub>BAT</sub> = 1.2 to 3.6 V                                                                                                             |

|                              | XSPI power                                                                        | supply                                                                                                                                                                                                                                                           | NA                                                                                             |                                                                                                                                                                        | V <sub>DDXSPI1</sub> = 1.62 to 3.6 V<br>V <sub>DDXSPI2</sub> = 1.62 to 3.6 V                                                                |

|                              | V <sub>CORE</sub> suppl                                                           | ies                                                                                                                                                                                                                                                              | 0.7 V ≤ V <sub>CAP</sub> ≤ 1.35 V                                                              |                                                                                                                                                                        | 0.74 V ≤ V <sub>CAP</sub> ≤ 1.36 V                                                                                                          |

|                              |                                                                                   |                                                                                                                                                                                                                                                                  | V <sub>OS0</sub> = 1.38 V                                                                      |                                                                                                                                                                        |                                                                                                                                             |

|                              | Rea hypass:                                                                       | must be supplied from                                                                                                                                                                                                                                            | V <sub>OS1</sub>                                                                               | = 1.2 V                                                                                                                                                                | V <sub>OS high</sub> = 1.38 V                                                                                                               |

|                              | Reg bypass: must be supplied from an external regulator on V <sub>CAP</sub> pins. |                                                                                                                                                                                                                                                                  | V <sub>OS2</sub>                                                                               | = 1.1 V                                                                                                                                                                | Voo. = 1 23 V                                                                                                                               |

|                              |                                                                                   | V <sub>OS3</sub> = 1.03 V                                                                                                                                                                                                                                        |                                                                                                | V <sub>OS low</sub> = 1.23 V                                                                                                                                           |                                                                                                                                             |

| Peripheral supply regulation |                                                                                   | USB regulator                                                                                                                                                                                                                                                    |                                                                                                | USB regulator                                                                                                                                                          |                                                                                                                                             |

| Power supply supervision     |                                                                                   | <ul> <li>POR/PDR monitor</li> <li>BOR monitor</li> <li>PVD monitor</li> <li>AVD monitor<sup>(1)</sup></li> <li>V<sub>BAT</sub> thresholds<sup>(2)</sup></li> <li>Temperature thresholds<sup>(3)</sup></li> </ul>                                                 |                                                                                                |                                                                                                                                                                        |                                                                                                                                             |

<sup>1.</sup> Analog voltage detector (AVD): Monitor the V<sub>DDA</sub> supply by comparing it to a threshold selected by the ALS[1:0] bits in the PWR\_CR1 register. The AVD is enabled by setting the AVDEN bit in the PWR\_CR1 register.

AN5996 - Rev 3 page 19/42

<sup>2.</sup> Battery voltage thresholds ( $V_{BAT}$  thresholds): Indicate if  $V_{BAT}$  is higher or lower than the threshold. The  $V_{BAT}$  supply monitoring (available only in  $V_{BAT}$  mode) can be enabled/disabled via the MONEN bit in the PWR\_CR2 register.

<sup>3.</sup> Temperature thresholds: Indicates whether the device temperature is higher or lower than the threshold. The temperature monitoring can be enabled/disabled via the MONEN bit in the PWR\_CR2 register.

Figure 4. System supply configuration on STM32H7Rx/7Sx

Notes:

The mode SMPS supplies LDO is not supported in STM32H7Rx/Sx.

The SMPS step-down converter is not available on all packages, and the Bypass mode is available only when the SMPS is available.

DT72527V1

Figure 5. System supply configuration on STM32H730

Note: The SMPS step-down converter is not available on all packages, and the Bypass mode is available only when the SMPS is available.

Figure 6. System supply configuration on STM32H750

JT73272V1

AN5996 - Rev 3

#### 6.2.6 General-purpose I/Os (GPIO)

The STM32H7Rx/7Sx devices implement the same GPIO features than the STM32H730 and STM32H750 devices, but with main differences. For the STM32H7Rx/7Sx devices, each GPIO port has:

- Four 32-bit configuration registers:

- GPIOx MODER

- GPIOx OTYPER

- GPIOx OSPEEDR

- GPIOx PUPDR

- Two 32-bit data registers:

- GPIOx\_IDR

- GPIOx ODR

- A 16-bit reset register:

- GPIOx BRR

- A 32-bit set/reset register:

- GPIOx BSRR

- A 32-bit locking register:

- GPIOx LCKR