## Migrating from STM32F446 to STM32H523/533 MCUs

#### Introduction

The designers of STM32 microcontroller applications must have the possibility to easily replace one microcontroller type with another one from the same product family or products from a different family. The reasons for migrating an application to a different microcontroller can be for example:

- To fulfill higher product requirements, extra demands on memory size, or an increased number of I/Os.

- To meet cost reduction constraints that require a switch to smaller components and shrink the PCB area.

This application note details the steps required to migrate from an existing design based on the STM32F446 MCUs to one based on the STM32H523/533 MCUs.

This document provides the full set of features available for the STM32F446 devices, and the equivalent features on the STM32H523/533 product lines. This document also provides guidelines on both hardware and peripheral migration.

To better understand the information inside this application note, the user must be familiar with the STM32 microcontroller family.

This application note is a complement to the STM32F446 and STM32H523/533 datasheets and reference manuals. For additional information, refer to the product datasheets and reference manuals.

## 1 General information

STM32F446 and STM32H523/533 MCUs are 32-bit microcontrollers based on the Arm® Cortex® processor.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

**Table 1. Reference documents**

| Document<br>number | Title                                                                                                                                                                                          |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [1]                | STM32F446xx advanced Arm®-based 32-bit MCUs reference manual (RM0390)                                                                                                                          |

| [2]                | STM32H523/33, STM32H562/63, and STM32H573 Arm®-based 32-bit MCUs reference manual (RM0481)                                                                                                     |

| [3]                | Arm® Cortex®-M4 32-bit MCU+FPU, 225 DMIPS, up to 512 KB Flash/128+4 KB RAM, USB OTG HS/FS, seventeen TIMs, three ADCs and twenty communication interfaces datasheet (DS10693)                  |

| [4]                | Arm <sup>®</sup> Cortex <sup>®</sup> -M33 32-bit MCU+TrustZone <sup>®</sup> +FPU, 375 DMIPS 250 MHz, 512-Kbyte flash memory, 272-Kbyte RAM, math accelerators datasheet (DS14539 and DS14540 ) |

AN5992 - Rev 2 page 2/45

Note:

## 2 STM32H523/533 MCUs overview

#### 2.1 Main features

STM32H523/533 MCUs include a larger set of peripherals, with more advanced features compared to STM32F446 MCUs.

Some of the new peripherals for STM32H523/533 are:

- Security

- TrustZone<sup>®</sup>-aware and securable peripherals

- Active tamper, secure firmware installation, secure firmware upgrade support, and secure data storage with hardware unique key

- Preconfigured immutable root of trust (ST-iROT)

- Flexible life cycle scheme with secure debug authentication

- Up to eight configurable SAU regions

- Additional encryption accelerator engine

- Advanced encryption hardware accelerator (AES)

- Public key accelerator (PKA)

- Secure AES coprocessor (SAES)

- On-the-fly decryption engine on OCTOSPI (OTFDEC)

- Performance

- Frequency up to 250 MHz

- Direct access to flash interface through ICACHE

- ICACHE for internal and external memories

- DCACHE for external memories

- New communication interface

- I3C, FDCAN, LPUART, USB Type-C® connector/USB power delivery interface (UCPD), PSSI

This document only manages the differences between STM32F446 and STM32H523/533 for the common features. The new features of STM32H523/533, mainly linked to TrustZone<sup>®</sup> support, are not covered. The detailed list of available features and packages for each product is available in the respective product datasheets.

The table below summarizes the memory availability of the STM32F446 and STM32H523/533 MCUs.

Flash memory RAM size (Kbytes) **Products** Feature level SRAM1 SRAM2 SRAM3 **BKPSRAM** Size Dual bank With hardware crypto: AES, PKA, STM32H533 Up to 512 Kbytes 2 Yes 128 an 64 SAES, and OTFDEC STM32H523 Up to 512 Kbytes Yes 128 80 64 2 Without hardware crypto STM32F446 Up to 512 Kbytes No 112 16 NA 4 NA

Table 2. Memory availability

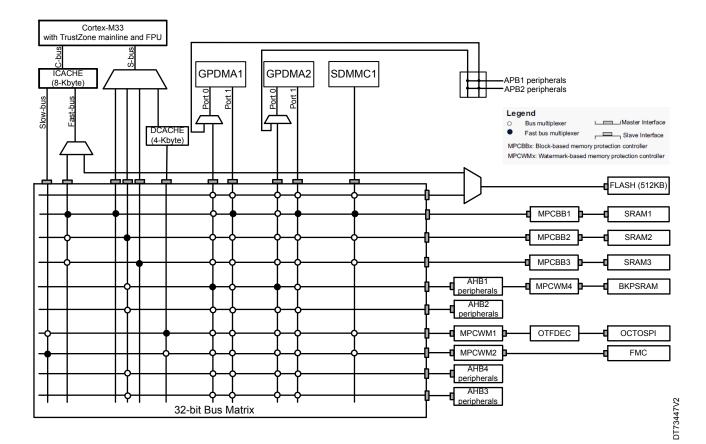

## 2.2 System architecture

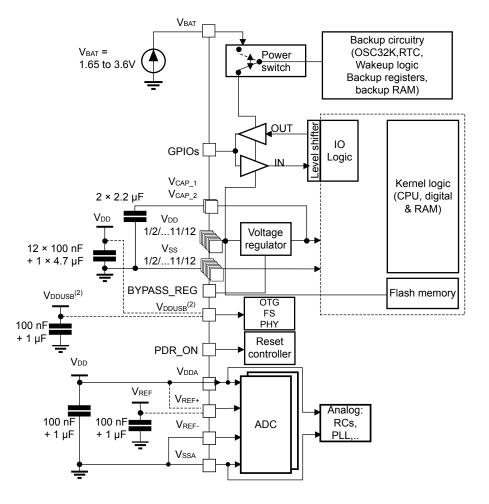

The STM32H523/533 MCUs embed:

- High-speed memories: 512 Kbytes of dual bank flash memory and 272 Kbytes of SRAM.

- A flexible external memory controller (FMC) for devices with packages of 100 pins and more.

- One Octo-SPI memory interface (one Octo-SPI available on all packages) and an extensive range of enhanced I/Os and peripherals connected to three APB buses.

- Three AHB buses and a 32-bit multi-AHB bus matrix.

The following table illustrates the bus matrix differences between STM32F446 and STM32H523/533.

AN5992 - Rev 2 page 3/45

Table 3. Bus matrix

| Bus type                     | STM32F446                                                                                                                                                                                          | STM32H523/533                                                                                                                                                                                        |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| AHB bus<br>matrix<br>masters | Up to 7 masters:  CPU I-bus, D-bus and S-bus, DMA1 memory bus, DMA2 memory bus, DMA2 peripheral bus, USB OTG_HS DMA bus                                                                            | Up to 11 masters: Fast C-bus, slow C-bus, CPU S-bus for internal memories, CPU S-bus for external memories, GPDMA1 (featuring two controller ports), GPDMA2 (featuring two controller ports), SDMMC1 |  |

| AHB bus<br>matrix slaves     | Up to 7 slaves: Internal flash memory ICode bus, internal flash memory DCode bus, SRAM1, SRAM2, AHB1 peripherals (including AHB to APB bridges and APB peripherals), AHB2 peripherals, FMC/QUADSPI | Up to 10 slaves: Internal flash memory, SRAM1, SRAM2, SRAM3, AHB1 peripherals (including APB1 and APB2), backup RAM, AHB2 peripherals, FMC, OCTOSPI, AHB3 peripherals, AHB4 peripherals              |  |

The bus matrix provides access from a controller to a target, enabling concurrent access and efficient operations even when several high-speed peripherals work simultaneously.

The figures below show the system architectures of STM32F446 and STM32H523/533.

ARM GΡ GΡ USB OTG Cortex-M4 DMA1 DMA2 HS snq-I D-bus S-pns DMA\_PI DMA\_P2 USB\_HS\_M DMA MEM1 DMA\_MEM2 ICODE ACCEL Flash memory DCODE SRAM1 112 Kbyte SRAM2 16 Kbyte AHB1 peripherals APB1 AHB2 peripherals APB2 FMC MemCtl/ QuadSPI DT73442V1 Bus matrix-S

Figure 1. STM32F446 system architecture

AN5992 - Rev 2 page 4/45

Figure 2. STM32H523/533 system architecture

AN5992 - Rev 2 page 5/45

## 3 Hardware migration

This section presents the package and pinout compatibility details for the hardware migration.

## 3.1 Package availability

STM32H523 and STM32H533 devices offer eight packages from 39 to 144 pins.

The table below lists the available packages on STM32H523 and STM32H533 devices compared to STM32F446 devices.

Package(size in mm x mm) STM32F446 STM32H523/533 LQFP144 (20 x 20 mm) Х Х LQFP100 14 x 14 mm) Χ Χ LQFP64 (10 x 10 mm) Х LQFP48 (7 x 7 mm) NA Х UFBGA144 (10 x 10 mm, 0,80 mm pitch) Χ Χ UFBGA144 (7 x 7 mm, 0,50 mm pitch) Χ NA UFBGA100 (7 x 7 mm, 0,50 mm pitch) NA Х **UFQFPN48 (7 x 7 mm)** NA **WLCSP** WLCSP81 WLCSP39

Table 4. Available packages

## 3.2 Pinout compatibility

STM32F446 devices are not identical to STM32H523/533 devices in terms of MCU port assignment to package terminals, that is, in terms of pinout. This holds for all common package types of the packages listed in Table 4. Available packages.

For the LQFP144 package, in STM32H523/533 devices, the VCAP\_1 and VCAP\_2 pins are replaced with a VSS and VDDUSB pin, respectively.

The following sections show the packages pinout figures and difference tables.

AN5992 - Rev 2 page 6/45

<sup>1.</sup> X = available, NA = not available

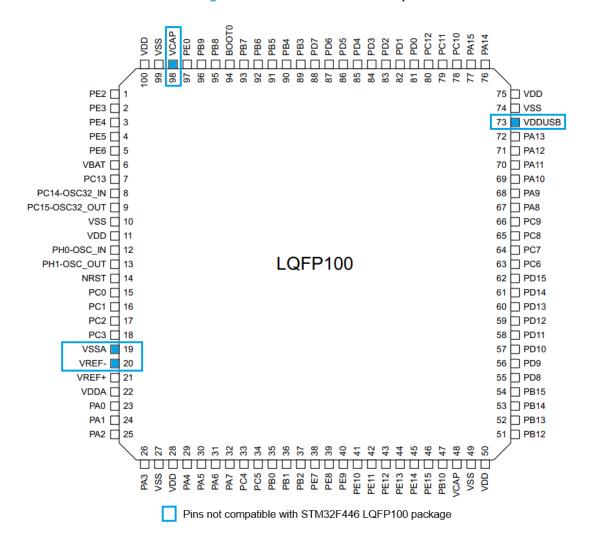

### 3.2.1 LQFP100 package

Figure 3. STM32H523/533 LQFP100 pinout

Table 5. LQFP100 pinout differences

| LQFP100 pin number | STM32F446 pinout | STM32H523/533 pinout |

|--------------------|------------------|----------------------|

| 19                 | VDD              | VSSA                 |

| 20                 | VSSA/VREF-       | VREF-                |

| 73                 | VCAP_2           | VDDUSB               |

| 98                 | PE1              | VCAP                 |

AN5992 - Rev 2 page 7/45

#### 3.2.2 LQFP144 package

108 🗖 VDD 107 🛭 VSS VDDUSB 106 106 VDDU

105 PA13

104 PA12

103 PA11

102 PA10

101 PA9

100 PA8

99 PC9

98 PC8

97 PC7

96 PC6 95 VDD 94 VSS 93 | PG8 92 | PG7 91 | PG6 90 | PG5 89 | PG4 LQFP144 88 | PG3 87 | PG2 86 | PD15 85 | PD14 84 | VDD 83 | VSS 82 | PD13 81 | PD12 80 | PD14 80 PD11 79 PD10 78 | PD9 77 | PD8 76 PB15 75 PB14 74 PB13 73 PB12

Figure 4. STM32H523/533 LQFP144 pinout

Pins not compatible with STM32F446 LQFP144 package

Table 6. LQFP144 pinout differences

| LQFP144 pin number | STM32F446 pinout | STM32H523/533 pinout |

|--------------------|------------------|----------------------|

| 70                 | PB11             | VCAP                 |

| 71                 | VCAP_1           | VSS                  |

| 95                 | VDDUSB           | VDD                  |

| 106                | VCAP_2           | VDDUSB               |

| 121                | VDD              | VDDIO2               |

| 142                | PE1              | VCAP                 |

| 143                | PDR_ON           | VSS                  |

AN5992 - Rev 2 page 8/45

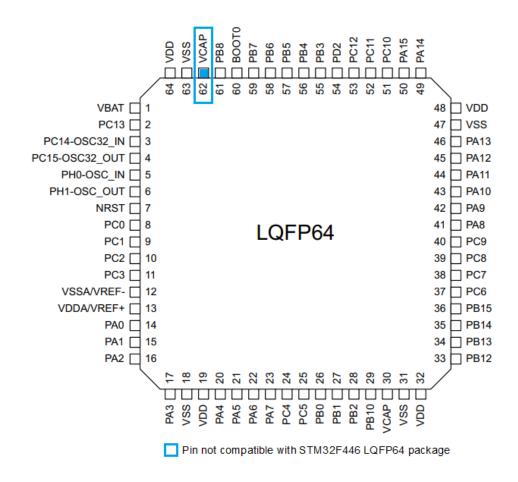

### 3.2.3 LQFP64 package

Figure 5. STM32H523/533 LQFP64 pinout

Table 7. LQFP64 pinout differences

| LQFP64 pin number | STM32F446 pinout | STM32H523/533 pinout |  |

|-------------------|------------------|----------------------|--|

| 62                | PB9              | VCAP                 |  |

#### 3.2.4 UFBGA144 package

For the UFBGA144 package, STM32F446 devices are not compatible with STM32H523/533 devices.

AN5992 - Rev 2 page 9/45

## 4 Boot mode compatibility

#### 4.1 Boot mode selection

In STM32F446, three different boot modes can be selected through the BOOT[1:0] pins as shown in the table below.

Table 8. Boot modes for STM32F446

| Boot mode selection pins |       | Boot mode                                                     | Aliasing                                             |

|--------------------------|-------|---------------------------------------------------------------|------------------------------------------------------|

| BOOT1                    | воото | Boot mode                                                     | Allasiliy                                            |

| X                        | 0     | Main flash memory                                             | The main flash memory is selected as the boot space. |

| 0                        | 1     | System memory The system memory is selected as the boot space |                                                      |

| 1                        | 1     | Embedded SRAM                                                 | The embedded SRAM is selected as the boot space.     |

STM32H523/533 embed an SBS peripheral that controls boot and security features. For these devices, the main boot control actions are listed below:

- Run the product with or without TrustZone<sup>®</sup> enabled.

- Choose between ST-iROT or OEM-iROT (refer to the reference manual for more details).

- Boot when launching a debug authentication sequence.

- Select boot between the bootloader or the user flash memory boot.

- Initialize the HDPL boot value.

For STM32H523/533 devices, the boot configurations are chosen based on the product settings:

- BOOT0: to select booting on user flash memory or RSS (root secure services).

- BOOT\_UBE: option byte to select the iROT between ST-iROT and OEM-iROT.

- TZEN: option byte to activate/deactivate the TrustZone<sup>®</sup>.

- sbs\_boot\_addresses: list of addresses defined by the flash memory:

- NSBOOTADD: nonsecure boot address

- SECBOOTADD: secure boot address

- PRODUCT\_STATE: option byte to activate the different security mechanisms depending on the product use

- sbs\_dbg\_req: used to launch the debug authentication protocol when booting.

The tables below present the STM32H533 boot modes, with TrustZone® either disabled or enabled.

Table 9. STM32H533 boot modes when TrustZone® is disabled (TZEN=0xC3)

| PRODUCT_STATE                  | BOOT0<br>pin | BOOT_UBE<br>FLASH_OPTSR[29:22] | Boot address<br>option-byte<br>selection | Boot area                                                      | STMicroelectronics<br>default programmed<br>value |

|--------------------------------|--------------|--------------------------------|------------------------------------------|----------------------------------------------------------------|---------------------------------------------------|

| Open                           | 0            | NA                             | NSBOOTADD[31:8]                          | Boot address defined<br>by user option byte<br>NSBOOTADD[31:8] | Flash: 0x0800 0000                                |

|                                | 1            | NA                             | NA                                       | Bootloader                                                     | Bootloader                                        |

| Provisioning                   | Х            | NA                             | NA                                       | RSS                                                            | RSS                                               |

| Provisioned,<br>Closed, Locked | х            | NA                             | NSBOOTADD[31:8]                          | Boot address defined<br>by user option byte<br>NSBOOTADD[31:8] | Flash: 0x0800 0000                                |

AN5992 - Rev 2 page 10/45

| Table 10. STM32H533 boot modes when TrustZone® is enabled (TZEN=0xB4 |

|----------------------------------------------------------------------|

|----------------------------------------------------------------------|

| PRODUCT_STATE                | BOOT0<br>pin | BOOT_UBE<br>FLASH_OPTSR[29:22] | Boot address<br>option-byte<br>selection | Boot area                                                       | STMicroelectronics<br>default<br>programmed value |

|------------------------------|--------------|--------------------------------|------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------|

| Open                         | 0            | x                              | SECBOOTADD[31:8]                         | Boot address defined<br>by user option byte<br>SECBOOTADD[31:8] | Flash: 0x0C00 0000                                |

| Open                         | 1            | 0xB4                           | NA                                       | Bootloader                                                      | Bootloader                                        |

|                              | 1            | 0xC3                           | NA                                       | ST-iROT                                                         | ST-iROT                                           |

| Provisioning                 | х            | NA                             | NA                                       | RSS                                                             | RSS                                               |

| Provisioned.                 | х            | 0xC3                           | ST-iROT                                  | ST-iROT                                                         | ST-iROT                                           |

| TZ_Closed,<br>Closed, Locked | x            | 0xB4                           | SECBOOTADD[31:8]                         | Boot address defined<br>by user option byte<br>SECBOOTADD[31:8] | Flash: 0x0C00 0000                                |

The tables below illustrate the STM32H523 boot modes, with TrustZone® either disabled or enabled.

Table 11. STM32H523 boot mode when TrustZone® is disabled (TZEN=0xC3)

| PRODUCT_STATE                  | BOOT0<br>pin | Boot address option-<br>byte selection | Boot area                                                | STMicroelectronics<br>default programmed<br>value |

|--------------------------------|--------------|----------------------------------------|----------------------------------------------------------|---------------------------------------------------|

| Open                           | 0            | NSBOOTADD[31:8]                        | Boot address defined by user option byte NSBOOTADD[31:8] | Flash: 0x0800 0000                                |

|                                | 1            | NA                                     | Bootloader                                               | Bootloader                                        |

| Provisioning                   | х            | NA                                     | RSS                                                      | RSS                                               |

| Provisioned, Closed,<br>Locked | x            | NSBOOTADD[31:8]                        | Boot address defined by user option byte NSBOOTADD[31:8] | Flash: 0x0800 0000                                |

Table 12. STM32H523 boot mode when TrustZone® is enabled (TZEN=0xB4)

| PRODUCT_STATE                                | BOOT0<br>pin | Boot address option-<br>byte selection | Boot area                                                 | STMicroelectronics<br>default programmed<br>value |

|----------------------------------------------|--------------|----------------------------------------|-----------------------------------------------------------|---------------------------------------------------|

| Open                                         | 0            | SECBOOTADD[31:8]                       | Boot address defined by user option byte SECBOOTADD[31:8] | Flash: 0x0C00 0000                                |

|                                              | 1            | NA                                     | Bootloader                                                | Bootloader                                        |

| Provisioning                                 | х            | NA                                     | RSS                                                       | RSS                                               |

| Provisioned,<br>TZ_Closed, Closed,<br>Locked | х            | SECBOOTADD[31:8]                       | Boot address defined by user option byte SECBOOTADD[31:8] | Flash: 0x0C00 0000                                |

## 4.2 System bootloader

The system bootloader is located in the system memory, programmed by STMicroelectronics in production. It is used to reprogram the flash memory using one of the serial interfaces.

The following table shows the supported communication peripherals by the system bootloader. For more details, refer to the application note *STM32 microcontroller system memory boot mode* (AN2606).

AN5992 - Rev 2 page 11/45

Table 13. Bootloader communication peripherals

| System bootloader peripherals | STM32F446xx I/O pin     | STM32H523/533 I/O pin              |

|-------------------------------|-------------------------|------------------------------------|

| DFU <sup>(1)</sup>            | PA11/F                  | PA12                               |

| USART1                        | PA10/I                  | PA9                                |

| USART2                        | NA                      | PA3/PA2                            |

| USART3                        | PB10/PB11 and PC10/PC11 | PD9/PD8 <sup>(2)</sup>             |

| CAN                           | CAN2 (PB5/PB13)         | FDCAN2(PB5/PB13) <sup>(3)</sup>    |

| I2C1                          | PB6/PB9                 | PB8/PB9 <sup>(4)</sup>             |

| I2C2                          | PF1/PF0                 | NA                                 |

| I2C3                          | PA8/PC9                 | PA8/PC9 <sup>(5)</sup>             |

| I3C1                          | NA                      | PB6 <sup>(6)</sup> /PB7            |

| SPI1                          | PA7/PA6/PA5/PA4         | PA7/PA6/PA5/PA4                    |

| SPI2                          | PB15/PB14/PC7/PB12      | PC1 <sup>(7)</sup> /PB14/PB10/PB12 |

| SPI3                          | NA                      | PC12/PC11/PC10/PA15 <sup>(4)</sup> |

| SPI4                          | PE14/PE13/PE12/PE11     | NA                                 |

- 1. On STM32H5, the USB DFU bootloader does not need an external quartz. It uses internal HSI48.

- $2. \quad \textit{Only for LQFP100, LQFP144, UFBGA144 and UFBGA100}\\$

- 3. On STM32H5xx, the FDCAN bootloader does not use an external quartz. It uses HSI and PLL.

- 4. Not available for LQFP48, UFQFN48, WLCSP39

- 5. PC9 is replaced by PB4 on LQFP48, UFQFN48 and WLCSP39

- 6. PB6 is replaced by PB8 on LQFP48, UFQFN48 and WLCSP39

- 7. PC1 is replaced by PB15 on LQFP48, UFQFN48 and WLCSP39

AN5992 - Rev 2 page 12/45

## 5 Peripheral migration

### 5.1 Cross compatibility between STM32 products

STM32 microcontrollers embed a set of peripherals that can be classified in the following groups:

- Group 1: peripherals common to all products by definition.

These peripherals are identical, so they have the same structure, registers, and control bits. There is no need to perform any firmware changes to keep the same functionality at the application level after migration. All features and behaviors remain the same.

- Group 2: peripherals shared by all products, but with minor differences (to support new features, in general).

- The migration from one product to another is easy and does not require any significant new development efforts.

- Group 3: peripherals that have considerable changes from one product to another (new architecture or new features, for example).

- For this group of peripherals, the migration requires a new development at the application level.

For STM32H523/533, all of the following can be configured as trusted or untrusted: each GPIO or peripheral, DMA channel, clock configuration register, ICACHE, DCACHE, and small part of the flash memory or SRAM. The following table summarizes the available peripherals in STM32F446 compared to STM32H523/533.

Table 14. STM32 peripheral compatibility between products

| Peripherals              |                                       | STM32F446 <sup>(1)</sup>                   | STM32H523/533 <sup>(1)</sup>                                                                                                                                         |

|--------------------------|---------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core                     |                                       | Cortex <sup>®</sup> -M4                    | Cortex <sup>®</sup> -M33 with TrustZone <sup>®</sup><br>mainline and FPU                                                                                             |

| ST immutable Root        | Of Trust (STIROT)                     | No                                         | Yes                                                                                                                                                                  |

| Maximum CPL              | J frequency                           | Up to 180 MHz                              | Up to 250 MHz                                                                                                                                                        |

| Flash me                 | emory                                 | Up to 512 Kbytes                           | Up to 512 Kbytes, with high-data-<br>cycle capability                                                                                                                |

| SRAMs                    | System                                | 128 Kbytes<br>(112+16)                     | 272 Kbytes<br>(128+80 (w/ECC)+64)                                                                                                                                    |

|                          | Backup                                | 4 Kbytes                                   | 2 Kbytes                                                                                                                                                             |

|                          | General purpose                       | 2 (32 bits) and 8 (16 bits)                | 2 (32 bits) and 4 (16 bits)                                                                                                                                          |

|                          | Advanced control                      | 2(16 bits)                                 | 2 (16 bits)                                                                                                                                                          |

|                          | Basic                                 | 2 (16 bits)                                | 2 (16 bits)                                                                                                                                                          |

| Timers                   | Low power <sup>(2)</sup>              | No                                         | 2 (16 bits)                                                                                                                                                          |

|                          | SysTick timer                         | 1                                          | 2                                                                                                                                                                    |

|                          | Watchdog timers (independent, window) | 2                                          | 2                                                                                                                                                                    |

|                          | SPI/I2S                               | Up to 4 SPIs, 3 with muxed full-duplex I2S | Up to 4 SPIs, including three muxed full-duplex I2S, and up to 4 additional SPIs from 3xUSART when configured in Synchronous mode (one additional SPI with Octo-SPI) |

| Communication interfaces | I2C                                   | Up to 4 I2C interfaces (SMBus/PMBus)       | 3 (Sm, Fm, and Fm+ interfaces (SMBus/PMBus)                                                                                                                          |

| Communication interfaces | I3C <sup>(2)</sup>                    | No                                         | 2                                                                                                                                                                    |

|                          | USART/UART                            | 4/2                                        | 4/2                                                                                                                                                                  |

|                          | LPUART <sup>(2)</sup>                 | No                                         | 1                                                                                                                                                                    |

|                          | USB                                   | USB OTG_FS and USB<br>OTG_HS               | USB FS                                                                                                                                                               |

AN5992 - Rev 2 page 13/45

| Peripherals                |                                | STM32F446 <sup>(1)</sup>                                                                    | STM32H523/533 <sup>(1)</sup>                                                                        |  |

|----------------------------|--------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|

|                            | UCPD (2)                       | No                                                                                          | Yes                                                                                                 |  |

|                            | CAN                            | 2                                                                                           | 2 FDCAN <sup>(2)</sup>                                                                              |  |

|                            | SAI                            | 2                                                                                           | No                                                                                                  |  |

| Communication interfaces   | SDIO                           | 1                                                                                           | 1                                                                                                   |  |

|                            | DCMI                           | Yes                                                                                         | Yes                                                                                                 |  |

|                            | PSSI <sup>(2)</sup>            | No                                                                                          | Yes                                                                                                 |  |

|                            | SPDIFRX                        | Yes                                                                                         | No                                                                                                  |  |

| Flexible memory of         | controller (FMC)               | Yes (8-, 6-bit data bus width); with SDRAM                                                  | Yes (8-, 16-bit data bus width); no SDRAM                                                           |  |

| Octo-S                     | SPI <sup>(2)</sup>             | No                                                                                          | 1                                                                                                   |  |

| Quad SPI memory in         | terface (Quad-SPI)             | Yes                                                                                         | Yes (Octo-SPI in quad-mode)                                                                         |  |

| HDMI-                      | CEC                            | Yes                                                                                         | Yes                                                                                                 |  |

| CRO                        | <u>C</u>                       | Yes                                                                                         | Yes                                                                                                 |  |

| DMA  Real-time clock (RTC) |                                | DMA1-DMA2 (8 streams each)                                                                  | 2 GPDMA <sup>(2)</sup> (featuring two controller ports), TrustZone <sup>®</sup> support/linked-list |  |

|                            |                                | Yes                                                                                         | Yes                                                                                                 |  |

| Random number g            | generator (RNG)                | No                                                                                          | Yes                                                                                                 |  |

| SAES, A                    | <b>AES</b> <sup>(2)</sup>      | No                                                                                          | Yes                                                                                                 |  |

| Public key accel           | erator <sup>(2)</sup> (PKA)    | No                                                                                          | Yes                                                                                                 |  |

| HASH (SHA-512)             |                                | No                                                                                          | Yes                                                                                                 |  |

| On-the-fly decryption      | engine <sup>(2)</sup> (OTFDEC) | No                                                                                          | Yes <sup>(3)</sup>                                                                                  |  |

| GPIC                       | Os                             | Up to 114                                                                                   | Up to 112                                                                                           |  |

| ADC (12 bits)              | Count                          | 3 (12-bit ADC 2.4 MSPS<br>and 7.2 MSPS in triple<br>interleaved mode); up to 24<br>channels | 2 (12-bit ADC with up to 5 MSPS); up to 20 channels                                                 |  |

| DAC (12 bits)              | Count                          | 1 (two channels)                                                                            | 1 (two channels)                                                                                    |  |

| Digital tempera            | ature sensor                   | No                                                                                          | Yes                                                                                                 |  |

| Operating temperatures     |                                | Ambient temperature: : -40 to +85°C /-40 to +105°C  Junction temperature: -40 to +125°C     | Ambient operating temperature: -40 to +85°C/-40 to +125°C  Junction temperature: -40 to +130°C      |  |

| Operating                  | voltage                        | 1.7 to 3.6 V                                                                                | 1.71 to 3.6 V                                                                                       |  |

| Internal voltage re        | eference buffer                | No                                                                                          | Yes                                                                                                 |  |

- 1. For more details, refer to the product datasheets.

- 2. New versus STM32F446.

- 3. Only for STM32H533xx devices.

## 5.2 Migration of system peripherals

## 5.2.1 Embedded flash memory (FLASH)

The following table compares the flash memory interface on STM32F446 and STM32H523/533 devices.

AN5992 - Rev 2 page 14/45

Table 15. FLASH features

| Flash memory                             | STM32F446                                                                                                                       | STM32H523/533                                                                                                                                                                                                                                                                        |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main/program memory                      | <ul><li>Up to 512 Kbytes</li><li>4 sectors of 16 Kbytes</li><li>1 sector of 64 Kbytes</li><li>3 sectors of 128 Kbytes</li></ul> | <ul> <li>Up to 512 Kbytes (dual bank)</li> <li>Flash memory read operations supporting multiple lengths: 128 bits, 64 bits, 32 bits, 16 bits, or one byte</li> <li>8 Kbytes sector erase, bank erase and dual-bank mass erase</li> </ul>                                             |

| Dual bank                                | No                                                                                                                              | Read while write (RWW) and flash bank swapping                                                                                                                                                                                                                                       |

| Error code correction (ECC)              | No                                                                                                                              | One error detection/correction or two error detections per 128-bit flash memory word using 9 ECC bits                                                                                                                                                                                |

| Wait states                              | Up to 8 (depending on the supply voltage and frequency)                                                                         | Up to 6 (depending on the supply voltage and frequency)                                                                                                                                                                                                                              |

| One time<br>programmable (OTP)<br>memory | 512 bytes (OTP) for user data                                                                                                   | 2 Kbytes (OTP) area                                                                                                                                                                                                                                                                  |

| FLASH security and protections           | <ul> <li>Read protection (RDP)</li> <li>Write protections</li> <li>Proprietary code readout protection (PCROP)</li> </ul>       | <ul> <li>TrustZone® backed watermark and block security protection</li> <li>HDP protection providing temporal isolation</li> <li>Configuration protection</li> <li>Write protection</li> <li>Device nonvolatile security life cycle and application boot state management</li> </ul> |

|                                          |                                                                                                                                 | NRST_STBY                                                                                                                                                                                                                                                                            |

|                                          |                                                                                                                                 | NRST_STOP                                                                                                                                                                                                                                                                            |

|                                          | nRST_STDBY                                                                                                                      | IWDG_SW                                                                                                                                                                                                                                                                              |

|                                          | nRST_STOP                                                                                                                       | WWDG_SW                                                                                                                                                                                                                                                                              |

|                                          | WDG_SW                                                                                                                          | IWDG_STBY, IWDG_STOP                                                                                                                                                                                                                                                                 |

|                                          | BOR_LEV                                                                                                                         | BOR_LEV                                                                                                                                                                                                                                                                              |

| User option bytes (1)                    | OPTSTRT                                                                                                                         | BORH_EN                                                                                                                                                                                                                                                                              |

| Oser option bytes                        | OPTLOCK                                                                                                                         | BOOT_UBE                                                                                                                                                                                                                                                                             |

|                                          | nWRP                                                                                                                            | OPTSTRT                                                                                                                                                                                                                                                                              |

|                                          | RDP                                                                                                                             | OPTLOCK                                                                                                                                                                                                                                                                              |

|                                          | USER                                                                                                                            | WRPSG                                                                                                                                                                                                                                                                                |

|                                          | SPRMOD                                                                                                                          | PRODUCT_STATE                                                                                                                                                                                                                                                                        |

|                                          |                                                                                                                                 | IO_VDDIO2_HSLV                                                                                                                                                                                                                                                                       |

|                                          |                                                                                                                                 | SWAP_BANK                                                                                                                                                                                                                                                                            |

<sup>1.</sup> Refer to the "Option-byte organization" table in the reference manual that provides all user option bytes.

#### 5.2.2 SRAMs

The RAMCFG controller, a new peripheral available on STM32H523/533, is dedicated to control SRAM1, SRAM2, SRAM3, and BKPSRAM. Refer to the *RAMs configuration controller* section in the corresponding reference manual for more details.

Table 16. SRAM features

| Features | STM32F446                                                                                                | STM32H523/533                                                                             |

|----------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Size     | Up to 128 Kbytes:  Main internal SRAM1 (112 KB)  Auxiliary internal SRAM2 (16 KB)  Kbytes of backup SRAM | Up to 274 Kbytes:  128-Kbyte SRAM1  80-Kbyte SRAM2 w/ECC  64-Kbyte SRAM3  2-Kbyte BKPSRAM |

AN5992 - Rev 2 page 15/45

| Features                               | STM32F446                                                                                                                                             | STM32H523/533                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Access by DMA and CPU                  | Bytes, half-words (16 bits),<br>or full words (32 bits)<br>possible access.                                                                           | Bytes, half-words (16 bits), or full words (32 bits) possible access.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CPU access<br>bus                      | System bus or I-Code/D-Code buses.                                                                                                                    | <ul><li>System bus or C-bus.</li><li>BKPSRAM (only system bus).</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Retention                              | Optional retention in Standby     Optional retention in VBAT m                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Security                               | NA                                                                                                                                                    | When the TrustZone® security is enabled, all SRAMs are secure after reset.  The SRAMs can be programmed as nonsecure, using the MPCBB with a block granularity of 512 bytes.                                                                                                                                                                                                                                                                                                                         |

| Hardware and software erase conditions | <ul> <li>The backup SRAM is not mass erased by a tamper event.</li> <li>Backup SRAM is only erased when the RDP changes from level 1 to 0.</li> </ul> | <ul> <li>SRAM1 and SRAM2 erase can be requested by executing a specific software sequence, detailed in section RAMCFG of the product reference manual.</li> <li>SRAM2 and optional backup SRAM are protected by the tamper detection circuit, and erased by hardware in case of tamper detection.</li> <li>SRAM2 is erased in case of regression.</li> </ul>                                                                                                                                         |

| System reset erase                     | NA                                                                                                                                                    | <ul> <li>SRAM2 can be erased with a system reset using the option bit SRAM2_RST option bit in the flash memory user option bytes.</li> <li>SRAM1 and SRAM3 are erased when a system reset occurs if the SRAM13_RST option bit is selected in the flash memory user option bytes.</li> </ul>                                                                                                                                                                                                          |

| Error detection and correction         | NA                                                                                                                                                    | <ul> <li>Single error detection and correction with interrupt generation.</li> <li>Double error detection with interrupt or NMI generation.</li> <li>The ECC is supported by SRAM2 and BKPSRAM when enabled with the SRAM2_ECC and BKPRAM_ECC user option bits.</li> <li>ECC: 7 bits are added per 32 bits.</li> <li>Interrupts are generated when single- and/or double-ECC errors are detected:         <ul> <li>Two ECC RAMCFG interrupts.</li> <li>One ECC NMI interrupt.</li> </ul> </li> </ul> |

| Write protection                       | NA                                                                                                                                                    | <ul> <li>SRAM2 can be write-protected with a page granularity of 1 Kbyte.</li> <li>Each 1-Kbyte page can be write-protected by setting its corresponding PxWP (x = 0 to 63) bit in RAMCFG registers.</li> </ul>                                                                                                                                                                                                                                                                                      |

## 5.2.3 System configuration controller

The table below illustrates the main differences in the system configuration controller (SYSCFG) between STM32F446 and STM32H523/533 devices.

Note: For the STM32H5 series, SYSCFG is integrated in the system configuration, boot, and security (SBS).

**Table 17. System configuration features**

| STM32F446                                                                                                     |    | STM32H523/533                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                               |    | Managing the I/O compensation cell                                                                                                                                                                                                                                                                                                          |

| Remap the memory accessible in the code area.     Manage the external interrupt line connection to the GPIOs. |    | NA                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                               | NA | <ul> <li>Enabling/disabling the FMP high-drive mode of some I/Os and voltage booster for the I/O analog switches.</li> <li>Configuring TrustZone<sup>®</sup> security register access.</li> <li>Tracking the PVT conditions to control the current slew-rate and output impedance in the I/O buffer through compensations cells.</li> </ul> |

AN5992 - Rev 2 page 16/45

| STM32F446 | STM32H523/533                                                                                                                                   |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

|           | Two compensation cells are embedded, one for the I/Os supplied by the VDDIO power rail, and one for the I/Os supplied by the VDDIO2 power rail. |  |

#### 5.2.4 Instruction and data caches (ICACHE/DCACHE)

STM32H523/533 devices embed an ICACHE (8 Kbytes) and a DCACHE (4 Kbytes), which allow a more efficient use of the external memory through Octo-SPI and FMC ports.

STM32F446 devices embed an ART Accelerator with cache.

## 5.2.5 Direct memory access controller (DMA)

STM32F446 and STM32H523/533 have different DMA architectures and features.

All devices embed two DMA controllers:

- DMA1 (eight channels) and DMA2 (eight channels) for STM32F446.

Each channel has dedicated management of the memory access requests from one or more peripherals.

The devices also embed an arbiter for handling the priorities among the DMA requests.

- GPDMA1 (eight channels) and GPDMA2 (eight channels) for STM32H523/533. Each GPDMA instance has

the same channel-based implementation and is connected to the same requests and triggers.

The following table illustrates the main differences between DMA requests in STM32F446 and STM32H523/533.

| Peripherals -                   | STM32F446               |                            | STM32H523/533     |                   |

|---------------------------------|-------------------------|----------------------------|-------------------|-------------------|

|                                 | DMA1                    | DMA2                       | GDMA1             | GDMA2             |

| Architecture                    | Each instance of        | DMA controllers can access | s memory and peri | oherals           |

| Number of instances             | 1 1 1                   |                            |                   |                   |

| Number of controllers           | Dual AHB controller bus | Dual AHB controller bus    | Dual bidirections | al AHB controller |

| Number of channels              | 8                       | 8                          | 8                 | 8                 |

| TrustZone <sup>®</sup> security |                         |                            |                   |                   |

| Privileged/unprivileged DMA     | NA                      |                            | Yes               |                   |

| Linked-List                     |                         |                            |                   |                   |

Table 18. DMA features

#### 5.2.6 Reset and clock control (RCC)

The table below presents the main differences related to the RCC (reset and clock controller) between STM32F446 and STM32H523/533 devices.

Table 19. RCC features

| RCC   | STM32F446            | STM32H523/533                                                                                             |

|-------|----------------------|-----------------------------------------------------------------------------------------------------------|

| HSI   | 16 MHz RC oscillator | 64 MHz RC oscillator                                                                                      |

|       |                      | CSI: low-power RC oscillator that can be used directly as a system clock, peripheral clock, or PLL input: |

|       |                      | low-cost clock source since no external crystal is required                                               |

| CSI   | NA NA                | faster startup time than HSI (a few microseconds)                                                         |

|       |                      | very low-power consumption.                                                                               |

|       |                      | The CSI provides a clock frequency of about 4 MHz.                                                        |

| HSI48 | NA                   | 48 MHz RC oscillator                                                                                      |

| ПЭ140 | NA NA                | HSI48 can drive USB and RNG.                                                                              |

| 1.01  | 32 kHz RC            |                                                                                                           |

| LSI   | Lower consu          | umption, higher accuracy                                                                                  |

AN5992 - Rev 2 page 17/45

| RCC                 | STM32F446                                                                                                                                                                                                                                                                                                                                                 | STM32H523/533                                                                                                                                                                                                                                                                                      |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HSE                 | From 4 to 26 MHz                                                                                                                                                                                                                                                                                                                                          | From 4 to 50 MHz                                                                                                                                                                                                                                                                                   |  |

| LSE                 | 32.768 kHz                                                                                                                                                                                                                                                                                                                                                | 32.768 kHz                                                                                                                                                                                                                                                                                         |  |

| LSE                 | Configurable drive/consumption                                                                                                                                                                                                                                                                                                                            | Configurable drive/consumption                                                                                                                                                                                                                                                                     |  |

| PLL                 | Three PLLs:  PLLI2S and PLLSAI generate an accurate clock  A main PLL clocked by the HSE or HSI oscillator and featuring three different output clocks:  One output generates the high-speed system clock (up to 180 MHz)  One output for USB OTG_FS, or SDIO  One output for the I2S1 and I2S2 clocks, the SPDIFRX clock, or the high speed system clock | Three PLLs:  Main PLL (PLL1) provides clocks for CPU and some peripherals  PLL2 and PLL3 generate the kernel clock for peripherals  Each PLL offers three outputs with postdividers.  Input frequency range:  2 to 16 MHz for the VCO in wide-range mode  1 to 2 MHz for the VCO in low-range mode |  |

| AHB frequency       | Up to 180 MHz                                                                                                                                                                                                                                                                                                                                             | Up to 250 MHz                                                                                                                                                                                                                                                                                      |  |

| APB1 frequency      | 42 MHz                                                                                                                                                                                                                                                                                                                                                    | Up to 250 MHz                                                                                                                                                                                                                                                                                      |  |

| APB2<br>frequency   | 84 MHz                                                                                                                                                                                                                                                                                                                                                    | Up to 250 MHz                                                                                                                                                                                                                                                                                      |  |

| RTC clock source    | LSE,                                                                                                                                                                                                                                                                                                                                                      | LSI, or HSE/ 32                                                                                                                                                                                                                                                                                    |  |

| Kernel clock        | Yes                                                                                                                                                                                                                                                                                                                                                       | Independent kernel clock for each peripheral, allowing frequency scaling without impact on communication interfaces                                                                                                                                                                                |  |

| System clock source | HSI, HSE, two main PLL                                                                                                                                                                                                                                                                                                                                    | HSI, CSI, HSE, or PLL1                                                                                                                                                                                                                                                                             |  |

| Clock security      | CSS on HSE                                                                                                                                                                                                                                                                                                                                                | CSS on HSE                                                                                                                                                                                                                                                                                         |  |

| system              | OSS SITTISE                                                                                                                                                                                                                                                                                                                                               | CSS on LSE                                                                                                                                                                                                                                                                                         |  |

| MCO clock<br>source | <ul> <li>MCO1 pin (PA8): HSI, LSE, HSE, or PLL</li> <li>MCO2 pin (PC9): HSE, PLL, SYSCLK, or<br/>PLLI2S</li> </ul>                                                                                                                                                                                                                                        | <ul> <li>MCO1 pin (PA8): HSI, LSE, HSE, PLL1, or HSI48</li> <li>MCO2 pin (PC9): SYSCLK, PLL2, HSE, PLL1, CSI, or LSI</li> </ul>                                                                                                                                                                    |  |

### Peripheral clock configuration

The peripherals presented below have a dedicated clock source that is used to generate the clock required for their operations. This section presents the differences between STM32F446 and STM32H523/533 devices, for peripherals with different clock sources.

Table 20. Peripherals with different clock sources

| Peripherals | STM32F446                                             | STM32H523/533            |

|-------------|-------------------------------------------------------|--------------------------|

|             | PLLI2S_Q                                              | pll1_q_ck                |

|             | PLLSAI_Q                                              | pll2_p_ck                |

| SAI         | PLL_R                                                 | pll3_p_ck                |

|             | HSI/HSE depends on PLLSRC (only for SAI2)             | AUDIOCLK                 |

|             | External clock mapped on I2S_CKIN pin (only for SAI1) | per_ck                   |

|             | APB1 or APB2 clock:                                   | rcc_pclk1 <sup>(1)</sup> |

| U(S)ART     | PCLK2 (only for USART1 and USART6)                    | rcc_pclk2 <sup>(2)</sup> |

|             | PCLK1 (for other USARTs)                              | pll2_q_ck                |

AN5992 - Rev 2 page 18/45

| Peripherals | STM32F446                                         | STM32H523/533             |

|-------------|---------------------------------------------------|---------------------------|

|             |                                                   | pll3_q_ck                 |

|             |                                                   | hsi_ker_ck                |

|             |                                                   | csi_ker_ck                |

|             |                                                   | lse_ck                    |

|             |                                                   | rcc_pclk1(3)              |

| I2Cs        | APB1 clock (PCLK1)                                | rcc_pclk3 <sup>(4)</sup>  |

| .255        | 7.1. 2.1. GOOK (* G2.1.1.)                        | pll3_r_ck                 |

|             |                                                   | hsi_ker_ck                |

|             |                                                   | rcc_pclk2 <sup>(5)</sup>  |

|             |                                                   | rcc_pclk3                 |

|             |                                                   | pll2_q_ck <sup>(5)</sup>  |

|             |                                                   | pll3_q_ck <sup>(5)</sup>  |

|             |                                                   | hsi_ker_ck <sup>(5)</sup> |

|             |                                                   | hse_ck <sup>(5)</sup>     |

| SPI         | APB clock (PCLK)                                  | csi_ker_ck <sup>(5)</sup> |

|             |                                                   | pll1_q_ck <sup>(6)</sup>  |

|             |                                                   | pll2_p_ck <sup>(6)</sup>  |

|             |                                                   | pll3_p_ck <sup>(6)</sup>  |

|             |                                                   | AUDIOCLK <sup>(6)</sup>   |

|             |                                                   | per_ck <sup>(6)</sup>     |

|             |                                                   | pll1_q_ck                 |

|             | PLLI2S_R                                          | pll2_p_ck                 |

| I2S         | External clock mapped on I2S_CKIN pin PLL_R       | pll3_p_ck                 |

|             | HSI/HSE depends on PLLSRC bit                     | AUDIOCLK                  |

|             |                                                   | per_ck                    |

|             |                                                   | hse_ck                    |

| CAN         | APB clock (PCLK)                                  | pll1_q_ck                 |

|             |                                                   | pll2_q_ck                 |

|             |                                                   | rcc_hclk                  |

|             |                                                   | sys_ck                    |

|             |                                                   | pll2_r_ck                 |

| ADC         | APB2 clock (PCLK2)                                | hse_ck                    |

|             |                                                   | hsi_ker_ck                |

|             |                                                   | csi_ker_ck                |

|             |                                                   | hsi48_ker_ck              |

| USB FS      | PLL 48 MHz derived from main PLL VCO (PLLQ clock) | pll1_q_ck                 |

|             |                                                   | pll3_q_ck                 |

|             | enio.                                             | SDMMC1:                   |

| SDIO/SDMMC  | SDIO:                                             | pll1_q_ck                 |