# L62xx motor drivers: contribution of internal resistance and propagation delay in current control circuitry

## Introduction

Some devices of the L62xx family integrate peak current control functions: the load current is measured through an external shunt resistor ( $R_{SENSEX}$ ) and compared to a reference value ( $V_{REFX}$ ). When the comparator triggers, a decay sequence is started with the duration set by an RC network.

This document investigates how the following parameters affect the set point of the current regulator:

- Parasitic resistances between the power stage and shunt resistor

- Propagation delay of the current control loop

The parasitic resistances do not affect the overcurrent protection.

Table 1 lists the devices concerned by this application note.

**Table 1. Devices list**

| Devices                      | Description                                          |

|------------------------------|------------------------------------------------------|

| L6207, L6207Q, L6227, L6227Q | Dual full bridge drivers with PWM current controller |

| L6208, L6208Q, L6228, L6228Q | Drivers for bipolar stepper motor                    |

| L6235, L6235Q, L6229, L6229Q | Drivers for three-phase brushless DC motor           |

# 1 Current sensing circuit

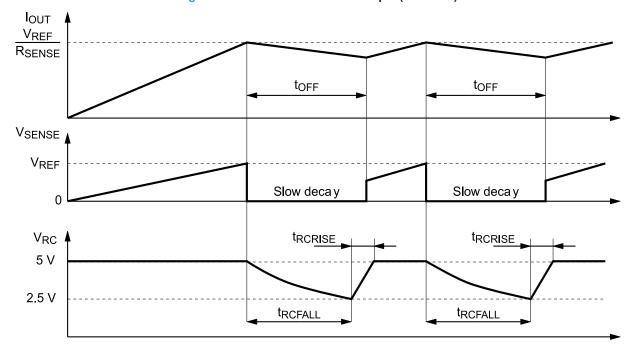

The PWM current control of the L62xx family is based on a peak detection with constant decay time.

The current flowing into the load is converted to voltage by the external shunt resistance to be compared with the target reference.

When the target reference is reached, the control circuitry commutates the power stage to the decay mode and triggers a monostable. This condition is maintained until the monostable returns to its steady-state according to the timing imposed by the external RC network.

Figure 1. PWM current limiter example (L6207/27)

AN5934 - Rev 1 page 2/12

## 1.1 Effect of parasitic resistances on PWM current control

The input of the control circuitry's comparator is not directly connected to the shunt and its voltage also depends on two parasitic resistances: internal connection between power stage and SENSEx pin and PCB traces (see Figure 2).

VSX I<sub>OUTX</sub> OUT2X **DRIVERS** Load **DRIVERS DEAD TIME** DEAD TIME OUT1X SENSE COMPARATOR CURRENT LIMITER **LOGIC** R<sub>SENSE,int</sub> **VREFX SENSEX R**SENSEX  $V_{REFX}$  $R_{\mathsf{SENSEX},\mathsf{PCB}}$

Figure 2. Current sensing circuit and parasitic resistances

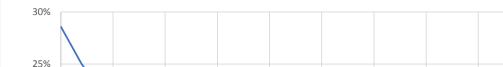

The internal connection resistance depends on package and its typical value is listed in Table 2.

$\begin{array}{c} \textbf{Typical internal resistance} \\ \textbf{(R}_{SENSE,int}) \\ \\ SO-24 & 10 \text{ m}\Omega \\ \\ PowerSO 36 & < 5 \text{ m}\Omega \\ \\ QFN48 7x7 \text{ mm} & 30 \text{ m}\Omega \\ \\ QFN32 5x5 \text{ mm} & 40 \text{ m}\Omega \\ \end{array}$

Table 2. Internal resistance contribution of different packages

The contribution of PCB traces depends on layout and is hardly predictable. The best solution is to minimize it, mounting the shunt resistors as near as possible to the SENSEX pins and keeping the ground connection as short as possible.

AN5934 - Rev 1 page 3/12

Parasitic resistances cause an extra drop at comparator input:

#### **Equation 1**

$$V_{COMP} = I_{OUTX} \times \left(R_{SENSEX} + R_{SENSEX, PCB} + R_{SENSE, int}\right) \tag{1}$$

Lowering the peak current level compared to the ideal set point:

## **Equation 2**

$$I_{peak,ID} = \frac{V_{REFX}}{R_{SENSEX}} \tag{2}$$

## **Equation 3**

$$I_{peak, actual} = \frac{V_{REFX}}{R_{SENSEX} + R_{SENSEX, PCB} + R_{SENSE, int}}$$

(3)

## **Equation 4**

$$I_{peak,\,actual} = I_{peak,\,ID} \times \left(\frac{R_{SENSEX}}{R_{SENSEX} + R_{SENSEX,\,PCB} + R_{SENSE,\,int}}\right) \tag{4}$$

To minimize the error, a higher value for the shunt resistor must be selected.

Figure 3. Peak current error vs. shunt resistor

AN5934 - Rev 1 page 4/12

Figure 4 shows the effect of internal parasitic resistance on the L6227Q.

Figure 4. Parasitic resistance effect example (L6227Q)

AN5934 - Rev 1 page 5/12

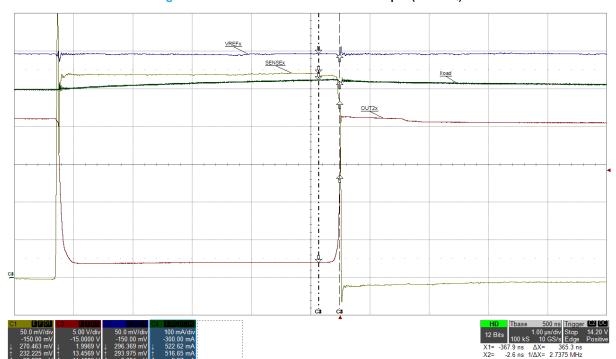

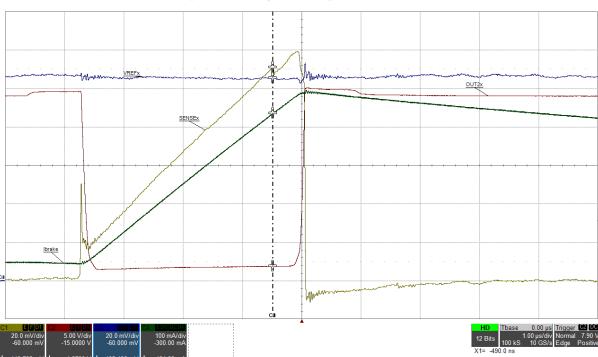

## 1.2 Effect of propagation delay on PWM current control

The turning-off of the power stage is delayed by  $t_{PROP}$  (500 ns typical) with respect to comparator triggering. This is related to both the intervention time of the control circuitry and power MOSFETs commutation timings.

Consequently, the actual peak current is always higher than the threshold value: the higher the charging slope, the bigger the error:

## **Equation 5**

$$\Delta I_{PEAK} = \frac{dI_{load}}{dt} \times t_{PROP} \tag{5}$$

Current slope is directly related to the characteristics of the load (inductance) and supply voltage.

Figure 5. Propagation delay effect example

AN5934 - Rev 1 page 6/12

# 2 Conclusions and overall behavior

As described in previous sections, the parasitic resistance always introduces a negative error (that is, actual current lower than target) and the propagation delay a positive one.

For this reason, in many cases the two effects compensate each other.

However, in particular cases one of the two could cause a not negligible difference between expected and actual peak current:

- Low shunt resistance value;

- Fast current slope (that is, low inductance and/or high supply voltage).

AN5934 - Rev 1 page 7/12

# **Revision history**

Table 3. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 21-Mar-2023 | 1       | Initial release. |

AN5934 - Rev 1 page 8/12

# **Contents**

| 1    | Cur     | rent sensing circuit                                   | 2  |

|------|---------|--------------------------------------------------------|----|

|      | 1.1     | Effect of parasitic resistances on PWM current control | 3  |

|      | 1.2     | Effect of propagation delay on PWM current control     | 6  |

| 2    | Cor     | iclusions and overall behavior                         | 7  |

| Rev  | rision  | history                                                | 8  |

| List | t of ta | bles                                                   | 10 |

| List | of fi   | aures                                                  | 11 |

# **List of tables**

| Table 1. | Devices list                                           |

|----------|--------------------------------------------------------|

| Table 2. | Internal resistance contribution of different packages |

|          | Document revision history                              |

AN5934 - Rev 1 page 10/12

# **List of figures**

| Figure 1. | PWM current limiter example (L6207/27)            | 2 |

|-----------|---------------------------------------------------|---|

| Figure 2. | Current sensing circuit and parasitic resistances | 3 |

| Figure 3. | Peak current error vs. shunt resistor             | 4 |

| Figure 4. | Parasitic resistance effect example (L6227Q)      | 5 |

| Figure 5. | Propagation delay effect example                  | 6 |

AN5934 - Rev 1 page 11/12

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2023 STMicroelectronics – All rights reserved

AN5934 - Rev 1 page 12/12