## How to build a short range wireless application with STM32WBA MCUs

#### Introduction

This application note guides designers through the steps required to build specific Bluetooth® Low Energy, Zigbee®, and Thread applications based on STM32WBA series microcontrollers.

It groups together the most important information and lists the aspects to be addressed.

To fully benefit from the information in this document and to develop an application, the user must be familiar with STM32 microcontrollers, Bluetooth® Low Energy, Zigbee®, and Thread technologies, and controller system services, such as low-power management and task sequencing.

For more information, such as deep dive concepts, instructions, and examples, visit the wiki website or refer to www.st.com.

**Table 1. Applicable products**

| Туре              | Product         |

|-------------------|-----------------|

| Microcontrollers  | STM32WBA series |

| Development board | NUCLEO-WBA55CG  |

|                   | NUCLEO-WBA52CG  |

|                   | NUCLEO-WBA65RI  |

| Discovery kit     | STM32WBA55G-DK1 |

|                   | STM32WBA65I-DK1 |

# List of acronyms and abbreviations

Table 2. Acronyms and abbreviations

| ACI         Application command interface           ATT         Attribute protocol           BLE         Bluetooth® Low Energy           BSP         Board support package           EXTI         Extended interrupts and event controller           FM         Flash manager           FUOTA         Firmware update over the air           FW         Firmware           GAP         Generic access profile           GATT         Generic attribute profile           HAL         Hardware abstraction layer           HCI         Host controller interface           HSE         High-speed external oscillator           HW         Hardware           IFS         Interframe space           IP         Semiconductor intellectual property core           ISR         Interrupt service routine           L2CAP         Logical link control and adaptation protocol           LL         Link layer           LPBAM         Low-speed external oscillator           NVIC         Nested vectored interrupt controller           NVM         Nonvolatile memory           OS         Operating system           PHY         Phase-locked loops           QOS         Quality of service <tr< th=""><th>Acronyms</th><th>Definitions</th></tr<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Acronyms | Definitions                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------|

| BIEE Bluetooth® Low Energy BSP Board support package EXTI Extended interrupts and event controller FM Flash manager FUOTA Firmware update over the air FW Firmware GAP Generic access profile GATT Generic attribute profile HAL Hardware abstraction layer HCI Host controller interface HSE High-speed external oscillator HW Hardware IFS Interframe space IP Semiconductor intellectual property core ISR Interrupt service routine L2CAP Logical link control and adaptation protocol LL Link layer LPBAM Low-power background autonomous mode LSE Low-speed external oscillator NVIC Nested vectored interrupt controller NVM Nonvolatile memory OS Operating system PHY Physical layer PLL Phase-locked loops QOS Quality of service RTG Real-time clock RTOS Real time operating system SNVMA Simple NVM arbiter SoC System on a chip SW office interrupt controller Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ACI      | Application command interface                |

| BSP Board support package  EXTI Extended interrupts and event controller  FM Flash manager  FUOTA Firmware update over the air  FW Firmware  GAP Generic access profile  GATT Generic access profile  HAL Hardware abstraction layer  HCI Host controller interface  HSE High-speed external oscillator  HW Hardware  IFS Interframe space  IP Semiconductor intellectual property core  ISR Interrupt service routine  L2CAP Logical link control and adaptation protocol  LL Link layer  LPBAM Low-power background autonomous mode  LSE Low-speed external oscillator  NVIC Nested vectored interrupt controller  NVM Nonvolatile memory  OS Operating system  PHY Physical layer  PLL Phase-locked loops  Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ATT      | Attribute protocol                           |

| EXTI Extended interrupts and event controller  FM Flash manager  FUOTA Firmware update over the air  FW Firmware  GAP Generic access profile  GATT Generic attribute profile  HAL Hardware abstraction layer  HCI Host controller interface  HSE High-speed external oscillator  HW Hardware  IFS Interframe space  IP Semiconductor intellectual property core  ISR Interrupt service routine  L2CAP Logical link control and adaptation protocol  LL Link layer  LPBAM Low-power background autonomous mode  LSE Low-speed external oscillator  NVIC Nested vectored interrupt controller  NVM Nonvolatile memory  OS Operating system  PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | BLE      | Bluetooth® Low Energy                        |

| FIM Flash manager FUOTA Firmware update over the air FW Firmware GAP Generic access profile GATT Generic attribute profile HAL Hardware abstraction layer HCI Host controller interface HSE High-speed external oscillator HW Hardware IFS Interframe space IP Semiconductor intellectual property core ISR Interrupt service routine L2CAP Logical link control and adaptation protocol LL Link layer LPBAM Low-spower background autonomous mode LSE Low-speed external oscillator NVIC Nested vectored interrupt controller NVIC Nested vectored interrupt controller NVM Nonvolatile memory OS Operating system PHY Physical layer PLL Phase-locked loops QOS Quality of service RTC Real-time clock RTOS Real time operating system SNVMA Simple NVM arbiter SoC System on a chip SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BSP      | Board support package                        |

| FUOTA Firmware update over the air  FW Firmware  GAP Generic access profile  GATT Generic attribute profile  HAL Hardware abstraction layer  HCI Host controller interface  HSE High-speed external oscillator  HW Hardware  IFS Interframe space  IP Semiconductor intellectual property core  ISR Interrupt service routine  L2CAP Logical link control and adaptation protocol  LL Link layer  LPBAM Low-speed external oscillator  NVIC Nested vectored interrupt controller  NVIC Nested vectored interrupt controller  NVM Nonvolatile memory  OS Operating system  PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | EXTI     | Extended interrupts and event controller     |

| FIW GAP Generic access profile GATT Generic attribute profile HAL Hardware abstraction layer HCI Host controller interface HSE High-speed external oscillator HW Hardware IFS Interframe space IP Semiconductor intellectual property core ISR Interrupt service routine L2CAP Logical link control and adaptation protocol LL Link layer LPBAM Low-power background autonomous mode LSE Low-speed external oscillator NVIC Nested vectored interrupt controller NVM Nonvolatile memory OS Operating system PHY Physical layer PLL Phase-locked loops QOS Quality of service RTC Real-time clock RTOS Real time operating system SNVMA Simple NVM arbiter SoC System on a chip SW Simple NVM arbiter Software Interval Adaptation Simple NVM arbiter Software Interval Service Int | FM       | Flash manager                                |

| GAP Generic access profile GATT Generic attribute profile HAL Hardware abstraction layer HCI Host controller interface HSE High-speed external oscillator HW Hardware IFS Interframe space IP Semiconductor intellectual property core ISR Interrupt service routine L2CAP Logical link control and adaptation protocol LL Link layer LPBAM Low-power background autonomous mode LSE Low-speed external oscillator NVIC Nested vectored interrupt controller NVM Nonvolatile memory OS Operating system PHY Physical layer PLL Phase-locked loops QOS Quality of service RTC Real-time clock RTOS Real time operating system SNVMA Simple NVM arbiter SoC System on a chip SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | FUOTA    | Firmware update over the air                 |

| GATT Generic attribute profile HAL Hardware abstraction layer HCI Host controller interface HSE High-speed external oscillator HW Hardware IFS Interframe space IP Semiconductor intellectual property core ISR Interrupt service routine L2CAP Logical link control and adaptation protocol LL Link layer LPBAM Low-power background autonomous mode LSE Low-speed external oscillator NVIC Nested vectored interrupt controller NVM Nonvolatile memory OS Operating system PHY Physical layer PLL Phase-locked loops QOS Quality of service RTC Real-time clock RTOS Real time operating system SNVMA Simple NVM arbiter SoC System on a chip SW official simple system services and so the simple system on a chip SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FW       | Firmware                                     |

| HAL Hardware abstraction layer HCI Host controller interface HSE High-speed external oscillator HW Hardware IFS Interframe space IP Semiconductor intellectual property core ISR Interrupt service routine L2CAP Logical link control and adaptation protocol LL Link layer LPBAM Low-power background autonomous mode LSE Low-speed external oscillator NVIC Nested vectored interrupt controller NVM Nonvolatile memory OS Operating system PHY Physical layer PLL Phase-locked loops QOS Quality of service RTC Real-time clock RTOS Real time operating system SNVMA Simple NVM arbiter SoC System on a chip SW of the real possible o | GAP      | Generic access profile                       |

| HCI Host controller interface HSE High-speed external oscillator HW Hardware IFS Interfame space IP Semiconductor intellectual property core ISR Interrupt service routine L2CAP Logical link control and adaptation protocol LL Link layer LPBAM Low-power background autonomous mode LSE Low-speed external oscillator NVIC Nested vectored interrupt controller NVM Nonvolatile memory OS Operating system PHY Physical layer PLL Phase-locked loops QOS Quality of service RTC Real-time clock RTOS Real time operating system SNVMA Simple NVM arbiter SoC System on a chip SW office Asserting asser | GATT     | Generic attribute profile                    |

| HSE High-speed external oscillator  HW Hardware  IFS Interframe space  IP Semiconductor intellectual property core  ISR Interrupt service routine  L2CAP Logical link control and adaptation protocol  LL Link layer  LPBAM Low-power background autonomous mode  LSE Low-speed external oscillator  NVIC Nested vectored interrupt controller  NVM Nonvolatile memory  OS Operating system  PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW Service RES Service RES Service RES Service RES Service Signed on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | HAL      | Hardware abstraction layer                   |

| HW Hardware  IFS Interframe space  IP Semiconductor intellectual property core  ISR Interrupt service routine  L2CAP Logical link control and adaptation protocol  LL Link layer  LPBAM Low-power background autonomous mode  LSE Low-speed external oscillator  NVIC Nested vectored interrupt controller  NVM Nonvolatile memory  OS Operating system  PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SOC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | HCI      | Host controller interface                    |

| IFS Interframe space IP Semiconductor intellectual property core ISR Interrupt service routine L2CAP Logical link control and adaptation protocol LL Link layer LPBAM Low-power background autonomous mode LSE Low-speed external oscillator NVIC Nested vectored interrupt controller NVM Nonvolatile memory OS Operating system PHY Physical layer PLL Phase-locked loops QOS Quality of service RTC Real-time clock RTOS Real time operating system SNVMA Simple NVM arbiter SoC System on a chip SW Semicoland adaptation protocol Interrupt control of the co | HSE      | High-speed external oscillator               |

| IP Semiconductor intellectual property core ISR Interrupt service routine L2CAP Logical link control and adaptation protocol LL Link layer LPBAM Low-power background autonomous mode LSE Low-speed external oscillator NVIC Nested vectored interrupt controller NVM Nonvolatile memory OS Operating system PHY Physical layer PLL Phase-locked loops QOS Quality of service RTC Real-time clock RTOS Real time operating system SNVMA Simple NVM arbiter SoC System on a chip SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | HW       | Hardware                                     |

| ISR Interrupt service routine  L2CAP Logical link control and adaptation protocol  LL Link layer  LPBAM Low-power background autonomous mode  LSE Low-speed external oscillator  NVIC Nested vectored interrupt controller  NVM Nonvolatile memory  OS Operating system  PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | IFS      | Interframe space                             |

| L2CAP Logical link control and adaptation protocol  LL Link layer  LPBAM Low-power background autonomous mode  LSE Low-speed external oscillator  NVIC Nested vectored interrupt controller  NVM Nonvolatile memory  OS Operating system  PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IP       | Semiconductor intellectual property core     |

| LL Link layer  LPBAM Low-power background autonomous mode  LSE Low-speed external oscillator  NVIC Nested vectored interrupt controller  NVM Nonvolatile memory  OS Operating system  PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ISR      | Interrupt service routine                    |

| LPBAM Low-power background autonomous mode  LSE Low-speed external oscillator  NVIC Nested vectored interrupt controller  NVM Nonvolatile memory  OS Operating system  PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | L2CAP    | Logical link control and adaptation protocol |

| LSE Low-speed external oscillator  NVIC Nested vectored interrupt controller  NVM Nonvolatile memory  OS Operating system  PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | LL       | Link layer                                   |

| NVIC Nested vectored interrupt controller  NVM Nonvolatile memory  OS Operating system  PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LPBAM    | Low-power background autonomous mode         |

| NVM Nonvolatile memory OS Operating system PHY Physical layer PLL Phase-locked loops QOS Quality of service RTC Real-time clock RTOS Real time operating system SNVMA Simple NVM arbiter SoC System on a chip SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LSE      | Low-speed external oscillator                |

| OS Operating system  PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | NVIC     | Nested vectored interrupt controller         |

| PHY Physical layer  PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NVM      | Nonvolatile memory                           |

| PLL Phase-locked loops  QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | OS       | Operating system                             |

| QOS Quality of service  RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PHY      | Physical layer                               |

| RTC Real-time clock  RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PLL      | Phase-locked loops                           |

| RTOS Real time operating system  SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | QOS      | Quality of service                           |

| SNVMA Simple NVM arbiter  SoC System on a chip  SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RTC      | Real-time clock                              |

| SoC System on a chip SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RTOS     | Real time operating system                   |

| SW software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | SNVMA    | Simple NVM arbiter                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SoC      | System on a chip                             |

| TZ TrustZone®                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SW       | software                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | TZ       | TrustZone®                                   |

| WFI Wait for interrupt (Arm assembly code)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | WFI      | Wait for interrupt (Arm assembly code)       |

AN5928 - Rev 5 page 2/36

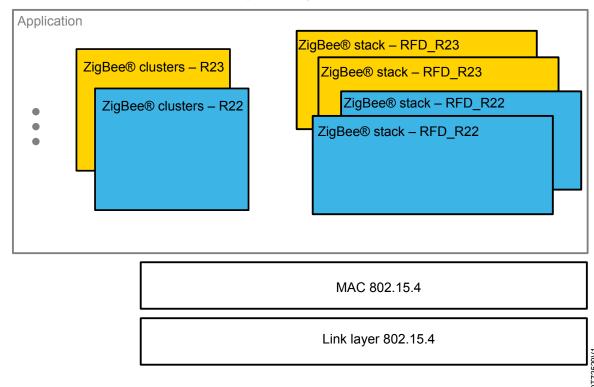

## 2 General information

The STM32WBA device is a multiprotocol wireless and ultra-low-power device. It embeds an Arm<sup>®</sup>CPU Cortex<sup>®</sup>-M33 core alongside a 2.4 GHz radio compliant with diverse wireless protocols such as Bluetooth<sup>®</sup> Low Energy (BLE), Zigbee<sup>®</sup>, or Thread.

It is also composed of a multitude of smart and high-performance peripherals, a large set of advanced and low-power analog features, and several peripherals tuned for low-power modes.

In addition to these, the STM32WBA also provides a dedicated security framework.

For more precise explanation relative to protocols, for example, BLE or system concepts related to low-power, refer to our wiki website.

Note: Arm is a registered trademark of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

arm

AN5928 - Rev 5 page 3/36

## 3 STM32WBA overview

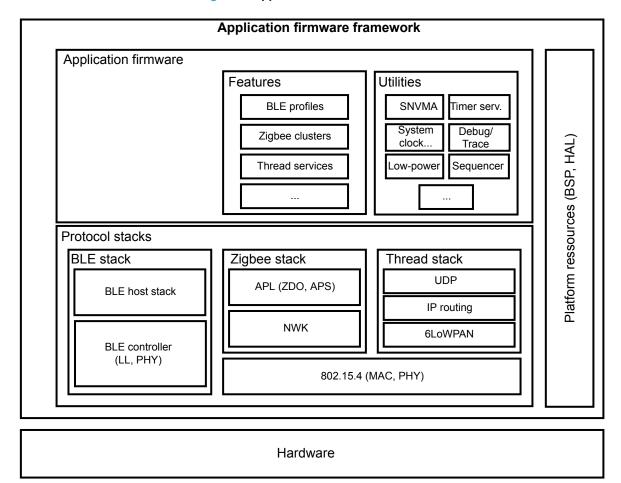

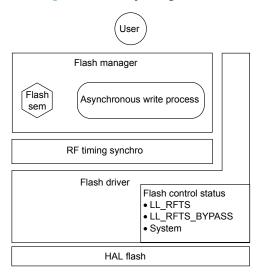

## 3.1 Software architecture

The software architecture is explained from two points of view:

- The application

- The project

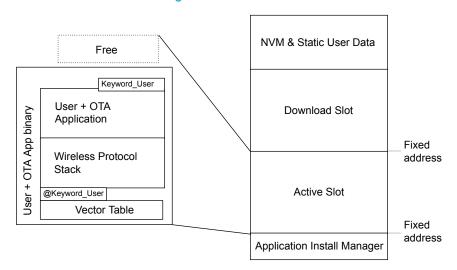

#### 3.1.1 Application view

From the application point of view, the user can rely on multiple modules and SW blocks to create an application. The framework is referred to as the Application Firmware Framework.

The architecture is designed over a 3-level organization:

- Application firmware

- Protocol stack (for example, Bluetooth® Low Energy, Zigbee®, or Thread

- Platform resources

Figure 1. Application Firmware Framework

DT72443V1

#### 3.1.1.1 Application firmware

The user application is based on:

- Peripherals either from STMicroelectronics or from a third-party supplier.

- Features developed by STMicroelectronics for short-range protocols, such as Bluetooth<sup>®</sup> Low Energy profiles, and others.

- Utilities required by the application and the protocol stacks.

- Generic utilities that provide easy access to basic features such as low-power management, sequencer, and others.

#### 3.1.1.2 Protocol stacks

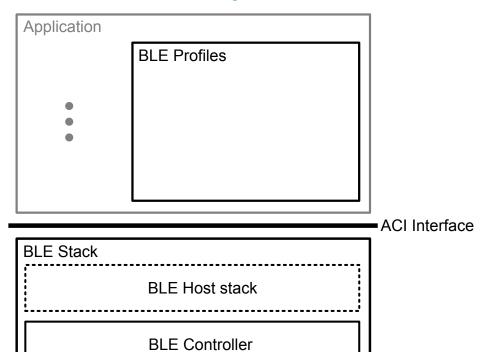

Multiple protocol stacks can interface with the application and the hardware. For instance, the Bluetooth® Low Energy stack is the main interface for BLE purposes. It is composed of two layers:

- BLE stack: It manages all networks and transport protocols that allow the application to communicate with other devices. Provided by STMicroelectronics, it can also be substituted by the host stack of the user.

- BLE controller: The BLE controller manages the hardware part, the RF state, and guarantees that the RF protocol is correctly followed. It includes the physical layer, the link layer, and the host controller interface.

#### 3.1.1.3 Platform resources

The platform resources include all the HALs, BSPs, and drivers that ease the platform hardware use.

#### 3.1.2 Project view

The project organization differs slightly from the application architecture, as it is repository based. Nevertheless, the above-mentioned concepts are found without difficulties.

This organization is divided into four parts as shown below.

Figure 2. Project view organization

| □ ●BLE_HeartRate - BLE_HeartRate |

|----------------------------------|

| —⊞ <b>f</b> Application          |

| —⊞ <b>i</b> Common               |

| —⊞ <b>=</b> Doc                  |

| — <b>⊞  ii</b> Drivers           |

| —⊞ <b>iii</b> Middlewares        |

| —⊞ <b>iii</b> Utilities          |

AN5928 - Rev 5 page 5/36

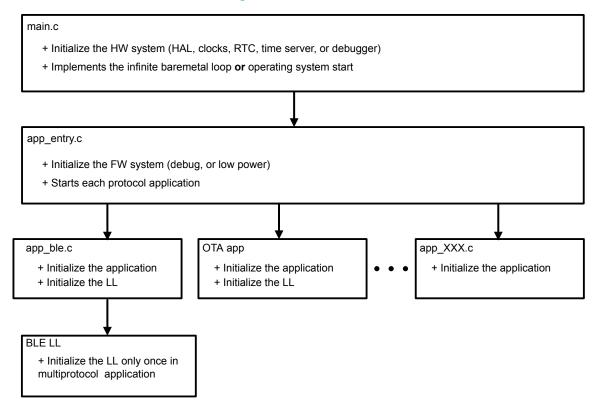

#### 3.1.2.1 Application

Application is the core part of the project. It regroups the main information and actions that define the user application.

This section is divided into five subdirectories:

- Core: This directory is the main entry point of the application. It contains all the setup and entry codes such as hardware initialization routines, IRQ's setup, scheduler configuration, or tasks registration.

The files contained below this directory are, for example, main.c, app entry.c.

- Startup: Includes the startup file of the project.

- STM32 WPAN: This part is composed of two subparts:

- App: Main applicative source files, for the example of HR, this repository contains the main application file app ble.c and the Bluetooth LE services implementation.

- Target: Dedicated to interface and integration of the libraries and modules present in middleware.

- System: System-related modules, interfaces, and utilities (PKA, RNG, advanced memory manager, USART, or RTDebug.). The user also has access to several configuration files to customize the system experience.

- System: This section regroups the system-related configurations, interfaces, and some application specific

modules (Bluetooth®LE timer, low-power management, etc.).

Note:

These are specific for each application - Not shared by every application and not necessarily in the same configuration. There are also generic modules, interfaces and startup available. They are shared by multiple applications and can be found in the Common/WPAN directory.

#### 3.1.2.2 Common

It is a directory that handles all the system modules, hardware interfaces, and startup files that are generic in between all the application.

This directory aims to limit divergence and heterogeneity among the connectivity application.

#### 3.1.2.3 Drivers

The drivers are divided into four component sets:

Hardware abstraction layer (HAL):

This layer provides the hardware abstraction drivers and the hardware interfacing methods to interact with the upper layers (application, libraries, and stacks). The HAL is composed of:

HAL drivers:

A set of portable abstraction APIs based on high level services built around standalone processes. The HAL drivers are functionality oriented, for example to the timer peripheral, for which it is possible to split APIs into several categories following the functions offered by the IPs (basic timer, capture, or PWM).

Low layer drivers:

A set of basic drivers with direct hardware access with no standalone processes. This layer is called either by the applications or by the HAL drivers.

HAL core drivers:

A set of internal drivers providing low level operations to the "complex" peripherals like the USB and Ethernet. They all come with a dedicated source and header files. Some drivers may have an additional file containing extended features, identified by the file extension " ex".

BSP drivers:

This layer contains the high-level board services for the different functionalities offered by the hardware (for example, LED, audio, or pushbuttons) and the drivers for the external components mounted on the used boards (audio codec, or IO expander).

CMSIS drivers:

Cortex<sup>®</sup> microcontroller software interface standard (CMSIS) drivers that provide a single standard across all Cortex-Mx processor series vendors. It enables code reuse and code sharing across software projects.

Basic peripheral usage examples:

This layer encloses the examples built over the STM32 peripheral using the HAL APIs and the low layer drivers.

AN5928 - Rev 5 page 6/36

#### 3.1.2.4 Middleware

Libraries and protocol-based components (BLE stack, for example). This directory contains the BLE services management, and system commands.

Horizontal interactions between the components of this layer are directly performed by calling the features APIs while the vertical interaction with the low-level drivers are performed through specific callbacks and static macros implemented in the library interface.

#### **3.1.2.5** *Utilities*

Miscellaneous software utilities that provide additional system and media resources services like sequencer tools box, time server, low-power manager, along with several trace utilities and standard library services like, memory, string, timer, and math services.

## 3.2 SW concepts/features

This chapter covers some of the main software components available on the STM32WBA. Each module concept is briefly described to enhance user appreciation of the platform capabilities.