# Solenoid driver channels parallel mode functionality: guidelines and limits

### Introduction

This document is intended to integrate the information provided in the L9305 product datasheet, in order to facilitate the correct usage of parallel mode functionality featured for solenoid driver channels. Guidelines are suggested for the device correct operation in parallel mode. Configuration and diagnostic items involved are highlighted.

# 1 Solenoid driver channels parallel mode operation

The 4 channels can be configured to work in parallel mode to allow regulation of higher current set-points: suitable for example in applications where HILOAD = 1 accuracy and resolution are not matching the desired target.

Channel parallelization can be enabled only for fixed channel pairs:

- ch0 can parallel with ch1 only

- ch2 can parallel with ch3 only

In parallel mode one channel acts as a master (ch0, ch2) and the other as a slave (ch1, ch3); both channel current sense measurements are kept active to measure load current split between channel pairs and the two measurements are combined and used to close control loop on master logic only.

Configuration of parallel mode is done through master channel registers. The following master parameters are valid for both channels, overwriting slave channel configuration (if any):

- current set-point

- · dither parameters

- control loop parameters (KI, KP, fix/var frequency mode selector, KFI, etc...)

As a consequence of described implementation, resulting resolution of current and dither set-point registers is doubled, since target value is applied on both channels in parallel: it means that in parallel mode 1LSB = 0.5 mA instead of default 0.25 mA for HILOAD = 0, while 1LSB = 0.66 mA instead of default 0.33 mA for HILOAD = 1. Resulting accuracy for current measurement is kept at 1% for high current range while is doubled from 5 mA to 10 mA for low current range for HILOAD = 0. For HILOAD = 1, accuracy for current measurement is kept at 4% for high current range while is doubled from 20 mA to 40 mA for low current range.

Feedback of measured average current is kept distinguished like in normal operation and available for each channel on its own register with nominal LSB of 0.25 mA or 0.33 mA according to HILOAD setting. The same applies for HS-LS compare check and applied offset compensation.

The following parameters are kept independent between master and slave channels and particular attention must be paid for proper configuration settings:

- · HW/SW mode selection

- HS/LS configuration

- INx/NDISx functionality

- diagnostic

- · calibration data

- offset compensation

To enable parallel mode the following conditions must be verified, in case any of the following is missing the channels will be kept independent following their own settings:

- Bit 14 and/or Bit 15 in SERVENA register must be set to 1 (Bit 14 enables parallel mode for ch0-ch1 pair, Bit 15 for ch2-ch3 pair)

- SOLENDRV configuration must be equal for the selected parallel channel pair

Even if diagnostic is kept independent, faults causing tri-state condition will affect both channels in parallel mode. Global registers for enabling parallel mode operation are the following:

AN5672 - Rev 1 page 2/36

### Service Enable - SERVENA

Address Global Base Address + 0x00

Type Read/Write

Description General SERVICE Enable bits

Table 1. SERVENA register detail

| Register bit | Field name/description                                                                                         | Default values | Typical conf. <sup>(1)</sup> | Type       |

|--------------|----------------------------------------------------------------------------------------------------------------|----------------|------------------------------|------------|

| [15]         | Parallel mode selection for ch2-ch3                                                                            | 0              | 1                            | Read/Write |

| [14]         | Parallel mode selection for ch0-ch1                                                                            | 0              | 1                            | Read/Write |

| [13:10]      | Unused                                                                                                         | 00 0000        | 00 0000                      | Read       |

| [9]          | RAM retrigger  1: Download calibration data from EEPROM.  0: Download complete or inactive                     | 0              | 0                            | Read/Write |

| [8]          | Spread Spectrum Disable:  0: Main Clock Spread Spectrum Enabled  1: Main Clock Spread Spectrum Disabled        | 0              | 0                            | Read/Write |

| [7:1]        | Unused                                                                                                         | 000 0000       | 000 0000                     | Read       |

| [0]          | Stagger Enable:  1: Stagger Enabled.  0: Stagger Disabled.  Valid only when channel is in Fixed Frequency mode | 0              | 0                            | Read/Write |

Typical configuration for parallel mode (different configuration might be needed, depending on specific customer's application).

#### **Solenoid Drivers Enable - SOLENDR**

Address Global Base Address + 0x01

Type Read/Write

Description Solenoid Driver Configuration

| Register bit | Field name/description                                                                                                                                                                                                                                  | Default values | Typical conf.(1) | Туре       |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|------------|

| [15:8]       | Unused                                                                                                                                                                                                                                                  | All "0"        | All "0"          | Read       |

| [7:6]        | Solenoid Driver State, Channel 3 00: Driver Off, OFF State Diagnostics disabled and masked 01: Driver tristate. OFF DIAG depending on bit on config reg 10: Drives on in PWM. OFF DIAG off and masked 11: Drives on in full-on. OFF DIAG off and masked | 01             | 01               | Read/Write |

| [5:4]        | Solenoid Driver State, Channel 2 00: Driver Off, OFF State Diagnostics disabled and masked 01: Drives tristate. OFF DIAG depending on bit on config reg 10: Drives on in PWM. OFF DIAG off and masked 11: Drives on in full-on. OFF DIAG off and masked | 01             | 01               | Read/Write |

AN5672 - Rev 1 page 3/36

| Register bit | Field name/description                                        | Default values | Typical conf.(1) | Туре       |

|--------------|---------------------------------------------------------------|----------------|------------------|------------|

|              | Solenoid Driver State, Channel 1                              |                |                  |            |

|              | 00: Driver Off, OFF State Diagnostics disabled and masked     |                |                  |            |

| [3:2]        | 01 : Drives tristate. OFF DIAG depending on bit on config reg | 01             | 01               | Read/Write |

|              | 10: Drives on in PWM. OFF DIAG off and masked                 |                |                  |            |

|              | 11: Drives on in full-on. OFF DIAG off and masked             |                |                  |            |

|              | Solenoid Driver State, Channel 0                              |                |                  |            |

|              | 00: Driver Off, OFF State Diagnostics disabled and masked     |                |                  |            |

| [1:0]        | 01: Drives tristate. OFF DIAG depending on bit on config reg  | 01             | 01               | Read/Write |

|              | 10: Drives on in PWM. OFF DIAG off and masked                 |                |                  |            |

|              | 11: Drives on in full-on. OFF DIAG off and masked             |                |                  |            |

<sup>1.</sup> Typical configuration for parallel mode (different configuration might be needed, depending on specific customer's application).

# 1.1 Channel registers configuration details

For channel pair configuration, the following registers can be written just for master channel, because the corresponding slave channel registers will be overwritten with the same settings.

#### **Current Setpoint - SETPOINT**

Address Channel\_X\_BaseAddress + 0x06

Type Read/Write

Description Register stores current setpoint code (HW mode current control). Current Control SETPOINT is coded into 13 bits. Current value depends on HILOAD bit

Table 2. SETPOINT register detail

| Register bit | Field name/description                                       | Default values | Typical conf. <sup>(1)</sup> | Туре       |

|--------------|--------------------------------------------------------------|----------------|------------------------------|------------|

|              | Auto Limit: Activates the transient mode on setpoint change: |                |                              |            |

| [15]         | 0: Inactive                                                  | 0              | 0                            | Read/Write |

|              | 1: Active                                                    |                |                              |            |

| [14:13]      | Unused                                                       | 0              | 0                            | Read       |

| [12:0]       | Current Setpoint Code                                        | All "0"        | User's setup                 | Read/Write |

<sup>1.</sup> Typical configuration for parallel mode (different configuration might be needed, depending on specific customer's application).

AN5672 - Rev 1 page 4/36

### **Control Configuration - CTRLCFG**

Address Channel\_X\_BaseAddress + 0x07

Type Read/Write

Description -

Table 3. CTRLCFG register detail

| Register bit | Field name/description                                                                                                                  | Default<br>values | Typical conf. | Туре       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------|------------|

|              | Transition Time: Too long period detection (if the current PWM time exceeds this threshold, the controller enters the transient state): |                   |               |            |

| [15:14]      | 00: 2.5 * Tpwm                                                                                                                          | 0                 | 0             | Read/Write |

| []           | 01 : 4.5 * Tpwm                                                                                                                         |                   |               |            |

|              | 10: 8.5 * Tpwm                                                                                                                          |                   |               |            |

|              | 11 : 16.5 * Tpwm                                                                                                                        |                   |               |            |

| [13:12]      | Unused                                                                                                                                  | 0                 | 0             | Read       |

|              | HW feedback Frequency Mode:                                                                                                             |                   |               |            |

| [11]         | 0: Fixed Frequency <sup>(2)</sup>                                                                                                       | 0                 | 0             | Read/Write |

|              | 1: Variable Frequency                                                                                                                   |                   |               |            |

| [10:0]       | Target PWM Period Code                                                                                                                  | All "0"           | User's setup  | Read/Write |

<sup>1.</sup> Typical configuration for parallel mode (different configuration might be needed, depending on specific customer's application).

#### **Gains Configuration - KGAINS**

Address Channel\_X\_BaseAddress + 0x09

Type Read/Write

Description Register stores KI (Integral error gain: HW mode current control) and KP (Proportional error gain: HW mode current control)

Table 4. KGAINS register detail

| Register bit | Field name/description                                                | Default values | Typical conf. <sup>(1)</sup> | Туре       |

|--------------|-----------------------------------------------------------------------|----------------|------------------------------|------------|

| [15:6]       | Unused                                                                | All "0"        | All "0"                      | Read       |

| [5:3]        | KI: Integral Gain of HW current control loop (fixed & variable freq.) | 100            | 110 <sup>(2)</sup>           | Read/Write |

| [2:0]        | KP: Proportional Gain of HW current control loop (fixed freq. only)   | 100            | 100 <sup>(2)</sup>           | Read/Write |

<sup>1.</sup> Typical configuration for parallel mode (different configuration might be needed, depending on specific customer's application).

AN5672 - Rev 1 page 5/36

<sup>2.</sup> For Fixed frequency Mode D[11] = 0 (default).

<sup>2.</sup> KI and KP parameters are strongly dependant on specific load and need to be fine tuned on actual application.

### Frequency Control - KFREQCTRL

Address Channel\_X\_BaseAddress + 0x08

Type Read/Write

Description Register stores KF, FCIL (Variable frequency forward gain: HW mode current control)

Table 5. KFREQCTRL register detail

| Register bit | Field name/description                                                       | Default values | Typical conf.(1)   | Туре       |

|--------------|------------------------------------------------------------------------------|----------------|--------------------|------------|

| [15:6]       | unused                                                                       | All "0"        | All "0"            | Read       |

| [5:3]        | KFI: Integral Gain of Frequency Control Loop                                 | 101            | 101 <sup>(2)</sup> | Read/Write |

| [2:0]        | FINT_START: Start value for frequency integrator upon exiting transient mode | 111            | 111 <sup>(2)</sup> | Read/Write |

Typical configuration for parallel mode (different configuration might be needed, depending on specific customer's application).

#### **Dither Programming 1 - DITHPGM1**

Address Channel\_X\_BaseAddress + 0x04

Type Read/Write

Description Dither Generator Configuration

Table 6. DITHPGM1 register detail

| Register bit | Field name/description                          | Default values | Typical conf. <sup>(1)</sup> | Туре       |

|--------------|-------------------------------------------------|----------------|------------------------------|------------|

|              | Dither Enable:                                  |                |                              |            |

| [15]         | 0: Disabled                                     | 0              | User's setup                 | Read/Write |

|              | 1: Enabled                                      |                |                              |            |

|              | DITHER_SYNC_EN:                                 |                |                              |            |

| [14]         | 0: Disabled                                     | 0              | User's setup                 | Read/Write |

|              | 1: Enabled                                      |                |                              |            |

|              | SYNC TYPE:                                      |                |                              |            |

| [13]         | 0: Dither Synchronization at each Dither Step   | 0              | User's setup                 | Read/Write |

|              | 1: Dither Synchronization at each dither Period |                |                              |            |

| [12:8]       | Unused                                          | All "0"        | All "0"                      | Read       |

| [7:0]        | Istep: Current step Value                       | 0101 0000      | User's setup                 | Read/Write |

<sup>1.</sup> Typical configuration for parallel mode (different configuration might be needed, depending on specific customer's application).

AN5672 - Rev 1 page 6/36

<sup>2.</sup> KFI and and FINT\_START parameters are strongly dependant on specific load and need to be fine tuned on actual application.

### **Dither Programming 2 - DITHPGM2**

Address Channel\_X\_BaseAddress + 0x05

Type Read/Write

Description Dither Generator Configuration

Table 7. DITHPGM2 register detail

| Register bits | Field name/description                               | Default values | Typical conf. <sup>(1)</sup> | Туре       |

|---------------|------------------------------------------------------|----------------|------------------------------|------------|

| [15:13]       | Unused                                               | 0              | 0                            | Read       |

| [12:8]        | Nstep: Number of steps in a quarter of dither period | 0 0101         | User's setup                 | Read/Write |

| [7:6]         | Unused                                               | 0              | 0                            | Read       |

| [5:0]         | Tstep: Number of PWM cycles for each dither step     | 00 1010        | User's setup                 | Read/Write |

<sup>1.</sup> Typical configuration for parallel mode (different configuration might be needed, depending on specific customer's application).

All remaining channel specific registers are kept independent between master and slave channels and particular attention must be paid for proper configuration settings both for master and slave channel. In particular, the following registers must be set identical between master and slave.

### **Configuration 1 - CONFIGURATION1**

Address Channel\_X\_BaseAddress + 0x02

Type Read/Write

Description Configuration register provides information related to channel configuration

Table 8. CONFIGURATION1 register detail

| Register bit | Field name/description                        | Default values | Typical conf. <sup>(1)</sup> | Туре       |

|--------------|-----------------------------------------------|----------------|------------------------------|------------|

| [15]         | Unused                                        | 0              | 0                            | Read       |

|              | OFS_CMP_DIS:                                  |                |                              |            |

| [14]         | 0: Current Sense Offset Compensation Active   | 0              | 0                            | Read/Write |

|              | 1: Current Sense Offset Compensation disabled |                |                              |            |

|              | CALIBRATION_DIS:                              |                |                              |            |

| [13]         | 0: Digital Current Sense Calibration Active   | 0              | 0                            | Read/Write |

|              | 1: Digital Current Sense Calibration Disabled |                |                              |            |

| [12:11]      | Unused                                        | 0              | 0                            | Read       |

|              | Solenoid Logic BIST:                          |                |                              |            |

| [10]         | 0: Logic BIST Reset                           | 0              | 0                            | Read/Write |

|              | 1: Logic BIST Enabled                         |                |                              |            |

|              | Td_Blank:                                     |                |                              |            |

| [9]          | 0: Long Blanking Time                         | 0              | 0                            | Read/Write |

|              | 1: Short Blanking Time                        |                |                              |            |

|              | HILOAD: Current Sense Scale:                  |                |                              |            |

| [8]          | 0: 1.5 A Max Current Range                    | 0              | 0                            | Read/Write |

|              | 1: 2.0 A Max Current Range                    |                |                              |            |

AN5672 - Rev 1 page 7/36

| Register bit | Field name/description           | Default values | Typical conf. <sup>(1)</sup> | Туре       |

|--------------|----------------------------------|----------------|------------------------------|------------|

| [7]          | Unused                           | 0              | 0                            | Read       |

|              | Overcurrent threshold selection: |                |                              |            |

| [6]          | 0: 4 A Theshold                  | 0              | User's setup                 | Read/Write |

|              | 1: 5 A Threshold                 |                |                              |            |

|              | Enable OFF Diagnosis:            |                |                              |            |

| [5]          | 0: Disabled (OFF)                | 0              | 0                            | Read/Write |

|              | 1: Enabled                       |                |                              |            |

| [4]          | Unused                           | 0              | 0                            | Read       |

|              | Solenoid Load Configuration:     |                |                              |            |

| [3]          | 0: Low Side                      | 0              | User's setup                 | Read/Write |

|              | 1: High Side                     |                |                              |            |

|              | Current Feedback Control Mode:   |                |                              |            |

| [2]          | 0: HW Feedback                   | 0              | User's setup                 | Read/Write |

|              | 1: SW Feedback                   |                |                              |            |

|              | Output Slew Rate:                |                |                              |            |

|              | 00: 0.4 V/μs                     |                |                              |            |

| [1:0]        | 01: 1.0 V/μs                     | 0              | 11                           | Read/Write |

|              | 10: 4.0 V/μs                     |                |                              |            |

|              | 11: 8.0 V/µs                     |                |                              |            |

Typical configuration for parallel mode (different configuration might be needed, depending on specific customer's application).

### **Configuration 2 - CONFIGURATION2**

Address Channel\_X\_BaseAddress + 0x03

Type Read/Write

Description Configuration Register for channel configuration self-tests. Before restarting any tests, wait for the register to return to "0"

Table 9. CONFIGURATION2 register detail

| Register bit | Field name/description                                                                             | Default values | Typical conf. <sup>(1)</sup> | Туре       |

|--------------|----------------------------------------------------------------------------------------------------|----------------|------------------------------|------------|

| [15:2]       | Unused                                                                                             | All "0"        | AII "0"                      | Read       |

| [1]          | Solenoid Diag Self Test: Short, Open Load and PWM Check 0: Self Test Disabled 1: Self Test Enabled | 0              | 0                            | Read/Write |

| [0]          | GND_SOL loss self test 0: Self TestDisabled 1: Self Test Enabled                                   | 0              | 0                            | Read/Write |

Typical configuration for parallel mode (different configuration might be needed, depending on specific customer's application).

AN5672 - Rev 1 page 8/36

## 1.2 Setup recommendations

It is mandatory to use only maximum Output Slew Rate setting: CONFIGURATION1[1:0] = 11.

In parallel mode, to avoid cross-conduction issues, a minimum ON time is recommended, depending on VBATP level; in particular, limitations suggested are the following:

- 15 μs @ VBATP = 19 V

- 20 μs @ VBATP = 35 V

This requires user's knowledge of VBAT maximum rating and load characteristics, in order to determine minimum allowable Current Setpoint, according to the procedure described in the next section.

#### 1.2.1 Minimum Current Setpoint calculation

Given a load, with known resistance value R, and knowing VBATP value, full-on (unregulated) current can be calculated as:

$$Full \ On \ Current = \frac{VBATP}{R} \tag{1}$$

Regulated current on the load, can be expressed as function of PWM signal duty cycle:

$$I_LOAD = Full \ On \ Current \times PWM\_DC \tag{2}$$

Minimum allowed I\_LOAD is the current L9305 will regulate with minimum allowed TON (15  $\mu$ s) and maximum VBATP and can be calculated joining previous expressions as follows:

$$minimum I_{\_LOAD} = \left(\frac{\text{max}imum VBATP}{R}\right) \times \left(\frac{15 \,\mu s}{T_{\_PWM}}\right) \tag{3}$$

From this value, Current Setpoint to be written in CHX\_SETPOINT register can be calculated as follows:

HILOAD = 0 → normal current mode - single bit resolution = 0.25 mA

$$ch X setpoint = \frac{\min imum I\_LOAD}{0.25}$$

(4)

• HILOAD = 1  $\rightarrow$  normal current mode - single bit resolution = 0.33 mA

$$ch X setpoint = \frac{\min mum I\_LOAD}{0.33}$$

(5)

AN5672 - Rev 1 page 9/36

## 1.3 Operative hints

#### 1.3.1 Channel enabling

For parallel mode operativity, the following settings must be written:

- SERVENA[15:14] = 11b

- SOLENDR[7:0] = 10101010b

With these settings, ch2-3 and ch0-1 will be configured to operate in parallel and all channels will be enabled in pwm-mode. For each pair, current setup, pwm period and other settings will be the ones user configured, namely, for ch2 and ch0 (also known as "master" channels, while ch3 and ch1 are known as "slave" channels); see Section 1.1 Channel registers configuration details for detailed list of overridden settings.

Note that for parallel mode to operate with master's parameters, both channels have to be enabled by their respective SOLENDR bits. If master channel of a pair is disabled, slave keeps working with its specific settings.

#### 1.3.2 Load connection

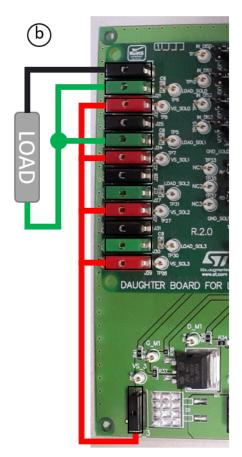

Although working in parallel mode, a load can be phisically connected to either one of the two LOADx pins of the master/slave pair, as shown in Figure 1 (a), where load is connected to LOAD0 pin of the ch0-ch1 parallel configuration.

Figure 1. Load connection in parallel mode

Note:

Be aware that, when parallel mode is used, reliable current reading will be available only on AVGCUR register of the channel to which load is phisically connected.

To avoid such problem, the simplest solution is to connect the load to both LOADx pins of the parallel channel, as shown in Figure 1 (b).

AN5672 - Rev 1 page 10/36

Parallel channels enabling bits can be modified while the solenoid is energized and the current regulation loop is working; should this happen, each channel will immediately start operating in stand-alone mode, according to its specific current setpoint, pwm period, KP and KI settings etc. General recommendation is to avoid runtime change of SERVENA[15:14] bits, however, according to the specific application, and being the user aware of the system behaviour during the parallel/stand-alone transition, it could be in principle performed.

AN5672 - Rev 1 page 11/36

# Parallel mode operation - faults and diagnostic management details

### 2.1 Overcurrent Protection

In the following analysis of overcurrent protection during parallel mode operation, two possible scenarios will be considered:

- the situation of Load\_solX pin short to battery;

- the situation of Load\_solX pin short to ground.

When overcurrent protection is triggered, the following SPI register is involved:

### **Exceptions 1 - EXCEPTIONS1**

Address Channel\_X\_BaseAddress + 0x00

Type Read Only

Description Solenoid Driver Fault Status

Table 10. EXCEPTIONS1 register detail

| Register bit | Field name/description                                                                      | Default<br>values | Туре           |

|--------------|---------------------------------------------------------------------------------------------|-------------------|----------------|

|              | Thermal Warning (T_WARN):                                                                   |                   |                |

| [15]         | 0: No Fault                                                                                 | 0                 | Clear on Read  |

|              | 1: Thermal Warning Present                                                                  |                   |                |

|              | EEPROM CRC Error on CSA Calibration Data:                                                   |                   |                |

| [14]         | 0: No Fault                                                                                 | 0                 | Read           |

|              | 1: CRC Error                                                                                |                   |                |

|              | EEPROM CRC error on A2D trimming bits:                                                      |                   |                |

| [13]         | 0: No Fault                                                                                 | 0                 | Read           |

|              | 1: CRC Error                                                                                |                   |                |

|              | PWM Check Fault (ON State):                                                                 |                   |                |

| [12]         | 0: No Fault                                                                                 | 0                 | Clear on Read  |

|              | 1: Fault                                                                                    |                   |                |

|              | PWM Check Comp Mismatch (ON State):                                                         |                   |                |

| [11]         | 0: No Fault                                                                                 | 0                 | Clear on Read  |

|              | 1: Fault                                                                                    |                   |                |

|              | Solenoid Logic BIST Status: (ADC mismatch, out of regulation, Solenoid driver control loop) |                   |                |

|              | 00: Idle                                                                                    |                   |                |

| [10:9]       | 01: BIST running                                                                            | 0                 | Read           |

|              | 10: BIST passed                                                                             |                   |                |

|              | 11: BIST failed                                                                             |                   |                |

|              | Solenoid Diag Self Test (OFF State):                                                        |                   |                |

| [8:7]        | 00: Self Test pass                                                                          | 0                 | Clear on Read  |

|              | 1: DIAG_LV comparator fail                                                                  |                   | Cical Oll Read |

|              | 10: DIAG OL comparator fail                                                                 |                   |                |

AN5672 - Rev 1 page 12/36

| Register bit | Field name/description         | Default<br>values | Туре          |

|--------------|--------------------------------|-------------------|---------------|

|              | 11: Self Test fail             |                   |               |

|              | Open Load (OFF State):         |                   |               |

| [6]          | 0: No Fault                    | 0                 | Clear on Read |

|              | 1: Open load                   |                   |               |

|              | Short Detection (OFF State):   |                   |               |

| [5]          | 0: No Fault                    | 0                 | Clear on Read |

|              | 1: Short Detected              |                   |               |

|              | Solenoid ADC Mismatch monitor: |                   |               |

| [4]          | 0: No Fault                    | 0                 | Clear on Read |

|              | 1: Mismatch Fault Detected     |                   |               |

|              | LS Clamp Active (ON state):    |                   |               |

| [3]          | 0: No Fault                    | 0                 | Clear on Read |

|              | 1: LS Clamp Activated          |                   |               |

|              | HS Over Current (ON State)     |                   |               |

| [2]          | 0: No Fault                    | 0                 | Clear on Read |

|              | 1: HS Over Current             |                   |               |

|              | LS Over Current (ON State)     |                   |               |

| [1]          | 0: No Fault                    | 0                 | Clear on Read |

|              | 1: LS Over Current             |                   |               |

|              | T_SD: (Thermal Shutdown)       |                   |               |

| [0]          | 0: No Fault                    | 0                 | Clear on Read |

|              | 1: Thermal Shutdown Fault      |                   |               |

#### 2.1.1 Load\_solX pin short to VBATP

General test case settings:

SR for Vload\_solX voltage: CONFIGURATION1, D[1:0] =  $11 \rightarrow 8V/\mu s$

Current set point for each channel 0.4 A, SETPOINT, D[12:0] = 640h: total current in the load 0.8 A

PWM control frequency = 8 KHz (7.692 KHz), CTRLCFG, D[10:0] = 0Dh

Case A: Short to VBATP executed on Load\_solX of master channel CHX.

No power-on reset occurs.

As soon as Vload\_solX is shorted to VBATP, DUT master (CHX) and slave (CHX+1) channels go into Low Side Over Current protection.

The parallel couple of channels other than the faulty one (i.e. 'X') keep working according to their configurations. Master channel X registers:

- LS OC is set

- DriveState\_CHX [1:0] is set '01' → CHX tristate

Registers CHX\_CONFIGURATION1, CHX\_SETPOINT and CHX\_CFG are kept with their value (not reset). Slave channel X+1 registers:

- LS OC is set

- DriveState CHX+1 [1:0] is set '01' → CHX+1 tristate

Registers CHX+1\_CONFIGURATION1, CHX+1\_SETPOINT and CHX+1\_CFG are kept with their value (not reset).

If both channels are attempted to be re-enabled before removing short to VBATP fault, LS\_OC bit is set only for master channel and both channels are tri-stated.

When both master and slave channels LS OC bit is set, there can be 2 scenarios:

AN5672 - Rev 1 page 13/36

- After short to VBATP fault is removed, if master Channel X EXCEPTIONS1 register is not read and both Channel X and Channel X+1 are attempted to be re-enabled, both master and slave channel are kept tri-stated, until master channel EXCEPTIONS1 register is read and LS\_OC cleared. After Master channel LS OC bit is cleared on read, the couple CHX (master) and CHX+1 (slave) operate properly.

- After short to VBATP fault is removed, If slave Channel X+1 EXCEPTIONS1 register is not read and both

Channel X and Channel X+1 are attempted to be re-enabled, slave Channel X+1 remains tri-stated, while

master channel CHX is re-enabled and it provides load with global couple setpoint + 100 mA current

(NOK). Slave channel remains tri-stated and provides no current until its EXCEPTIONS1 register is read and

LS\_OC cleared. After Slave channel LS\_OC bit is cleared on read, the couple CHX (master) and CHX+1

(slave) operate properly.

After short fault is removed, both Channel X and Channel X+1 EXCEPTIONS1 register must be read and then DUT channel X and channel X+1 needs to be re-enabled by microcontroller, before they can operate again. DUT is class C provided that it is managed by microcontroller, otherwise it is functional class D. No damages on DUT, so after test DUT is still working as before.

Table 11. OVC test A, monitored variables

| Measurement          | Result      | Expected by set-up | Product ISO 16750 class                   |

|----------------------|-------------|--------------------|-------------------------------------------|

| PWM frequency        | 0-7.696 kHz | 7.692kHz           | Class C with micro/ Class D without micro |

| nPOR_flag            | Not set     | Not set            | Class A                                   |

| Charge_Pump_UV       | Not set     | Not set            | Class A                                   |

| FAULTn               | set         | set                | Class C with micro/ Class D without micro |

| LS_OC                | set         | set                | Class C with micro/ Class D without micro |

| DriveState_CHX [1:0] | '01'        | '01'               | Class C with micro/ Class D without micro |

AN5672 - Rev 1 page 14/36

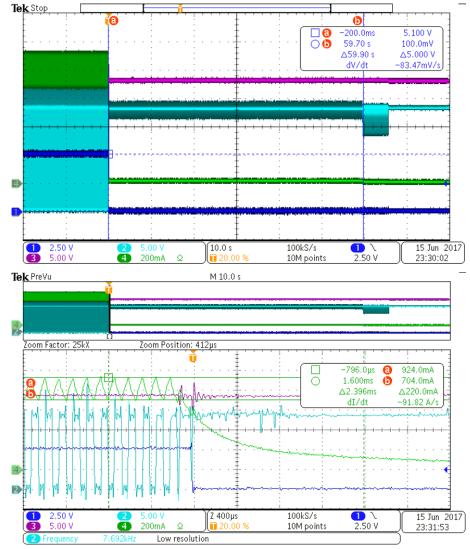

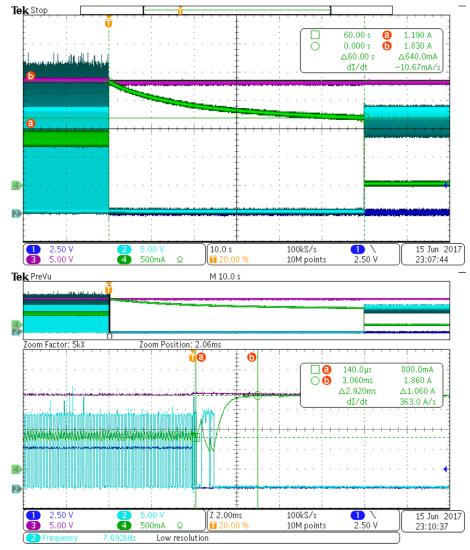

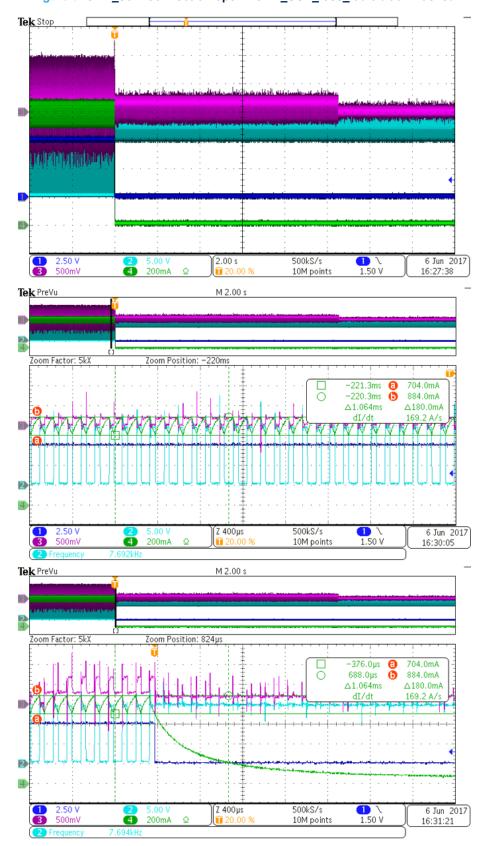

Figure 2. Vload\_sol0 short to VBATP - Load current

Legenda: Ch1: FAULTn, Ch2: Vload sol0, Ch3: VBATP, Ch4: Iload

Case B: Short to VBATP executed on Load\_solX+1 of master channel CHX+1.

No power-on reset occurs.

As soon as Vload\_solX is shorted to VBATP, DUT master (CHX) and slave (CHX+1) channels go into Low Side Over Current protection.

The parallel couple of channels other than the faulty one (i.e. 'X') keep working according to their configurations. Master channel X registers:

- LS\_OC is not set

- DriveState\_CHX [1:0] is set '01' → CHX tristate

Registers CHX\_CONFIGURATION1, CHX\_SETPOINT and CHX\_CFG are kept with their value (not reset). Slave channel X+1 registers:

- · LS OC is set

- DriveState CHX+1 [1:0] is set '01' → CHX+1 tristate

Registers CHX+1\_CONFIGURATION1, CHX+1\_SETPOINT and CHX+1\_CFG are kept with their value (not reset).

If both channels are attempted to be re-enabled before removing short to VBATP fault, LS\_OC bit is set for both master and slave channels and they are tri-stated.

AN5672 - Rev 1 page 15/36

When both master and slave channels LS\_OC bit is set, there can be 2 scenarios:

- After short to VBATP fault is removed, if master Channel X EXCEPTIONS1 register is not read and both Channel X and Channel X+1 are attempted to be re-enabled, both master and slave channel are kept tri-stated, until master channel EXCEPTIONS1 register is read and LS\_OC cleared. After Master channel LS\_OC bit is cleared on read, the couple CHX (master) and CHX+1 (slave) operate properly.

- After short to VBATP fault is removed, If slave Channel X+1 EXCEPTIONS1 register is not read and both Channel X and Channel X+1 are attempted to be re-enabled, slave Channel X+1 remains tri-stated, while master channel CHX is re-enabled and it provides load with global couple setpoint + 100 mA current (NOK). Slave channel remains tri-stated and provides no current until its EXCEPTIONS1 register is read and LS\_OC cleared. After Slave channel LS\_OC bit is cleared on read, the couple CHX (master) and CHX+1 (slave) operate properly.

After short fault is removed, both Channel X and Channel X+1 EXCEPTIONS1 register must be read and then DUT channel X and channel X+1 need to be re-enabled by microcontroller, before they can operate again properly.

DUT is class C provided that it is managed by microcontroller, otherwise it is functional class D. No damages on DUT, so after test DUT is still working as before.

Table 12. OVC test B, monitored variables

| Measurement          | Result      | Expected by set-up | Product ISO 16750 class                   |

|----------------------|-------------|--------------------|-------------------------------------------|

| PWM frequency        | 0-7.696 kHz | 7.692kHz           | Class C with micro/ Class D without micro |

| nPOR_flag            | Not set     | Not set            | Class A                                   |

| Charge_Pump_UV       | Not set     | Not set            | Class A                                   |

| FAULTn               | set         | set                | Class C with micro/ Class D without micro |

| LS_OC                | set         | set                | Class C with micro/ Class D without micro |

| DriveState_CHX [1:0] | '01'        | '01'               | Class C with micro/ Class D without micro |

AN5672 - Rev 1 page 16/36

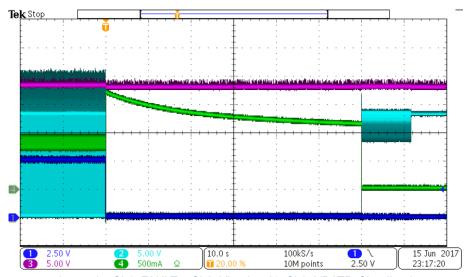

Figure 3. Vload\_sol1 short to VBATP - Load current

Legenda: Ch1: FAULTn, Ch2: Vload\_sol1, Ch3: VBATP, Ch4: Iload

#### 2.1.2 Load\_solX pin short to ground

General test case settings:

- SR for Vload solX voltage: CONFIGURATION1, D[1:0] =  $11 \rightarrow 8V/\mu s$

- Current set point for each channel 0.4 A, SETPOINT, D[12:0] = 640h: total current in the load 0.8 A

- PWM control frequency = 8 KHz (7.692 KHz), CTRLCFG, D[10:0] = 0Dh

Case A: Short to GND executed on Load\_solX of master channel CHX.

No power-on reset occurs.

As soon as Vload\_solX is shorted to GND, DUT master (CHX) and slave (CHX+1) channels go into High Side Over Current protection.

The parallel couple of channels other than the faulty one (i.e. 'X') keep working according to their configurations. Master channel X registers:

- HS OC is set

- DriveState\_CHX [1:0] is set '01' → CHX tristate

Registers CHX\_CONFIGURATION1, CHX\_SETPOINT and CHX\_CFG are kept with their value (not reset). Slave channel X+1 registers:

AN5672 - Rev 1 page 17/36

- HS\_OC is not set

- DriveState\_CHX+1 [1:0] is set '01' → CHX+1 tristate

Registers CHX+1\_CONFIGURATION1, CHX+1\_SETPOINT and CHX+1\_CFG are kept with their value (not reset).

If both channels are attempted to be re-enabled before removing short to GND fault, HS\_OC bit is set for both master and slave channels and they are tri-stated.

When both master and slave channels HS OC bit is set, there can be 2 scenarios:

- After short to GND fault is removed, if master Channel X EXCEPTIONS1 register is not read and both

Channel X and Channel X+1 are attempted to be re-enabled, both master and slave channel are kept

tri-stated, until master channel EXCEPTIONS1 register is read and HS\_OC cleared. After Master channel

HS\_OC bit is cleared on read, the couple CHX (master) and CHX+1 (slave) operate properly.

- After short to GND fault is removed, If slave Channel X+1 EXCEPTIONS1 register is not read and both Channel X and Channel X+1 are attempted to be re-enabled, slave Channel X+1 remains tri-stated, while master channel CHX is re-enabled and it provides load with global couple setpoint+100mA current (NOK).

Slave channel remains tri-stated and provides no current until its EXCEPTIONS1 register is read and HS\_OC cleared. After Slave channel HS\_OC bit is cleared on read, the couple CHX (master) and CHX+1 (slave) operate properly.

After short fault is removed, both Channel X and Channel X+1 EXCEPTIONS1 register must be read and then DUT channel X and channel X+1need to be re-enabled by microcontroller, before they can operate again properly.

DUT is class C provided that it is managed by microcontroller, otherwise it is functional class D. No damages on DUT, so after test DUT is still working as before.

| Measurement          | Result      | Expected by set-up | Product ISO 16750 class                   |

|----------------------|-------------|--------------------|-------------------------------------------|

| Weasurement          | Result      | Expected by Set-up | Froduct 150 To750 class                   |

| PWM frequency        | 0-7.696 kHz | 7.692kHz           | Class C with micro/ Class D without micro |

| nPOR_flag            | Not set     | Not set            | Class A                                   |

| Charge_Pump_UV       | Not set     | Not set            | Class A                                   |

| FAULTn               | set         | set                | Class C with micro/ Class D without micro |

| HS_OC                | set         | set                | Class C with micro/ Class D without micro |

| DriveState_CHX [1:0] | '01'        | '01'               | Class C with micro/ Class D without micro |

Table 13. STG test A, monitored variables

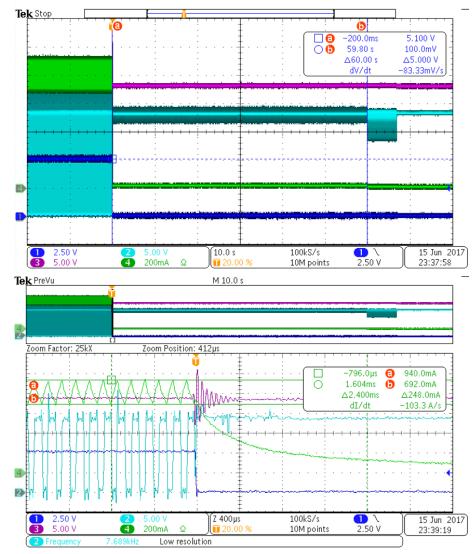

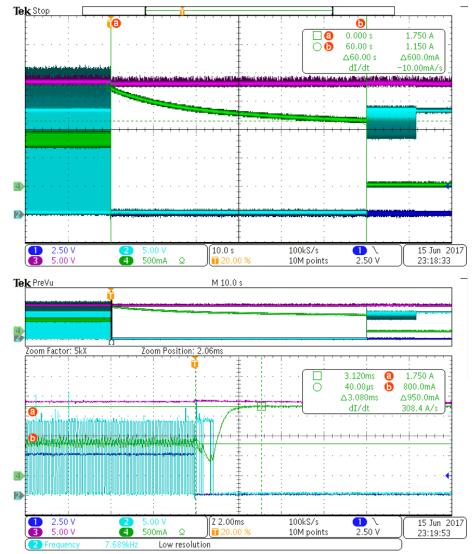

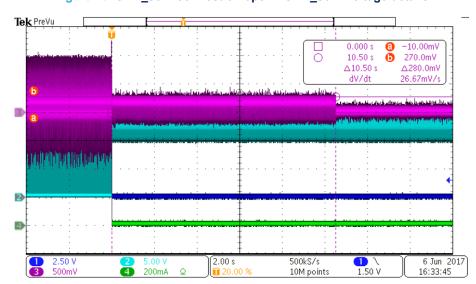

Legenda: Ch1: FAULTn, Ch2: Vload\_sol0, Ch3: VBATP, Ch4: Iload

AN5672 - Rev 1 page 18/36

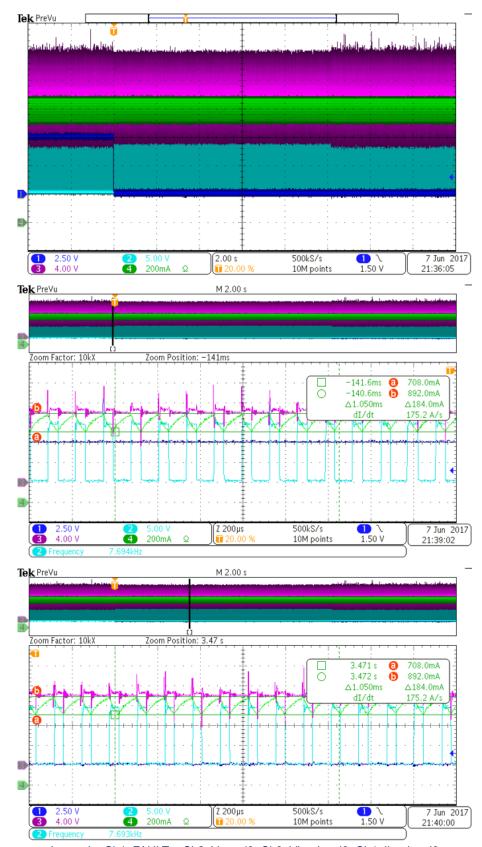

Figure 5. Vload\_sol0 short to GND - Load current details

Legenda: Ch1: FAULTn, Ch2: Vload\_sol0, Ch3: VBATP, Ch4: Iload

Case B: Short to GND executed on Load solX+1 of slave channel CHX+1.

No power-on reset occurs.

As soon as Vload\_solX is shorted to GND, DUT master (CHX) and slave (CHX+1) channels go into High Side Over Current protection.

The parallel couple of channels other than the faulty one (i.e. 'X') keep working according to their configurations. Master channel X registers:

- HS OC is not set

- DriveState\_CHX [1:0] is set '01' à CHX tristate

Registers CHX\_CONFIGURATION1, CHX\_SETPOINT and CHX\_CFG are kept with their value (not reset). Slave channel X+1 registers:

- HS\_OC is set

- DriveState\_CHX+1 [1:0] is set '01' à CHX+1 tristate

Registers CHX+1\_CONFIGURATION1, CHX+1\_SETPOINT and CHX+1\_CFG are kept with their value (not reset).

If both channels are attempted to be re-enabled before removing short to GND fault, HS\_OC bit is set for both master and slave channels and they are tri-stated.

AN5672 - Rev 1 page 19/36

When both master and slave channels HS\_OC bit is set, there can be 2 scenarios:

- After short to GND fault is removed, if master Channel X EXCEPTIONS1 register is not read and both

Channel X and Channel X+1 are attempted to be re-enabled, both master and slave channel are kept

tri-stated, until master channel EXCEPTIONS1 register is read and HS\_OC cleared. After Master channel

HS\_OC bit is cleared on read, the couple CHX(master) and CHX+1(slave) operate properly.

- After short to GND fault is removed, If slave Channel X+1 EXCEPTIONS1 register is not read and both

Channel X and Channel X+1 are attempted to be re-enabled, slave Channel X+1 remains tri-stated,

while master channel CHX is re-enabled and it provides load with global couple setpoint+100mA current

(NOK). Slave channel remains tri-stated and provides no current until its EXCEPTIONS1 register is read

and HS\_OC cleared. After Slave channel HS\_OC bit is cleared on read, the couple CHX(master) and

CHX+1(slave) operate properly.

After short fault is removed, both Channel X and Channel X+1 EXCEPTIONS1 register must be read and then DUT channel X and channel X+1need to be re-enabled by microcontroller, before they can operate again properly.

DUT is class C provided that it is managed by microcontroller, otherwise it is functional class D. No damages on DUT, so after test DUT is still working as before.

| Measurement          | Result      | Expected by set-up | Product ISO 16750 class                   |

|----------------------|-------------|--------------------|-------------------------------------------|

| PWM frequency        | 0-7.696 kHz | 7.692kHz           | Class C with micro/ Class D without micro |

| nPOR_flag            | Not set     | Not set            | Class A                                   |

| Charge_Pump_UV       | Not set     | Not set            | Class A                                   |

| FAULTn               | set         | set                | Class C with micro/ Class D without micro |

| HS_OC                | set         | set                | Class C with micro/ Class D without micro |

| DriveState_CHX [1:0] | '01'        | '01'               | Class C with micro/ Class D without micro |

Table 14. STG test B, monitored variables

Legenda: Ch1: FAULTn, Ch2: Vload\_sol1, Ch3: VBATP, Ch4: Iload

AN5672 - Rev 1 page 20/36

Figure 7. Vload\_sol1 short to GND - Load current details

Legenda: Ch1: FAULTn, Ch2: Vload sol1, Ch3: VBATP, Ch4: Iload

## 2.2 Low Side Clamping protection

When a solenoid channel is configured for low side operation, current recirculation occurs through the internal high side transistor. If the supply Vs\_solX of the high side driver is lost, the voltage at LOAD\_SOLx pin can become unpredictable and possibly exceed the absolute rating of the device. To prevent this condition from damaging the device, the low side driver has an integrated clamping circuit to limit the peak voltage.

Should the low side clamping structure be activated during normal operation (i.e. solenoid supply line within normal operating range), the channel is put in tri-state (setting the Solenoid Driver Status bits to 01) and the Low Side Clamp Active fault flag D[3] is set in the EXCEPTIONS1 register. To restart the channel, the MCU must clear the fault by reading the EXCEPTIONS1 register and re-enable the channel.

The involved SPI register for LS Clamping protection is still EXCEPTIONS1 (refer to description in Section 2.1 Overcurrent Protection).

In order to analyze LS Clamping protection the scenario of Vs\_solX loss during parallel mode operation has been considered.

AN5672 - Rev 1 page 21/36

#### 2.2.1 Loss of Vs\_solX connection - parallel solenoid driver channels configuration

General test case settings:

- SR for Vload\_solX voltage: CONFIGURATION1, D[1:0] = 11 → 8V/µs

- Current set point for each channel 0.4 A, SETPOINT, D[12:0] = 640h: total current in the load 0.8 A

- PWM control frequency = 8 KHz (7.692 KHz), CTRLCFG, D[10:0] = 0Dh

**Case A**: Open fault executed on Vs\_solX connection of the master channel (CHX) of the solenoid driver couple. Solenoid load is provided with a total current around 850 mA.

In master channel CHX:

- In CHX EXCEPTIONS1 Solenoid ADC Mismatch bit is set '1'

- In CHX\_EXCEPTIONS2 HS-LS\_Compare\_fault bit is set '1'

- AVGCUR register returns a current around 300 mA

- PWM SENSE register returns a 130 µs as a PWM period

#### In slave channel CHX+1:

- In CHX+1 EXCEPTIONS1 Solenoid ADC Mismatch bit is set '1'

- In CHX+1 EXCEPTIONS2 HS-LS Compare fault bit is set '1'

- In CHX+1 EXCEPTIONS2 Out of Regulation fault bit is set '1'

- AVGCUR register returns a current around 550 mA

- PWM\_SENSE register returns a 130 μs as a PWM period

Once the connection on Vs\_solX of the master channel (CHX) is restored, the solenoid driver couple get back working automatically as before the fault was injected.

**Case B**: Open fault executed on Vs\_solX connection of the slave channel (CHX+1) of the solenoid driver couple. Solenoid load is provided with a total current around 850 mA.

In master channel CHX:

- In CHX EXCEPTIONS2 HS-LS Compare fault bit is set '1'

- AVGCUR register returns a current around 550 mA

- PWM SENSE register returns a 130 μs as a PWM period

#### In slave channel CHX+1:

- In CHX+1 EXCEPTIONS1 Solenoid ADC Mismatch bit is set '1'

- In CHX+1 EXCEPTIONS2 HS-LS Compare fault bit is set '1'

- AVGCUR register returns a current around 300 mA

- PWM\_SENSE register returns a 130 μs as a PWM period

Once the connection on Vs\_solX of the master channel (CHX+1) is restored, the solenoid driver couple get back working automatically as before the fault was injected.

**Case C**: Open fault executed on Vs\_solX connection of both master (CHX) and slave channel (CHX+1) of the solenoid driver couple. Both master and slave driver channels of the couple under test are tri-stated (SOLENDR DriverState\_CHx[1:0] = '01'. Solenoid load driven by the couple under test is provided with a total current around 0 mA.

Solenoid driver couple other than the tested one keep on operating correctly.

In master channel CHX:

- In CHX EXCEPTIONS1 Solenoid ADC Mismatch bit is set '1'

- In CHX\_EXCEPTIONS1 LS\_Clamp Active is set '1'

- In CHX\_EXCEPTIONS2 HS-LS\_Compare\_fault bit is set '1'

- AVGCUR register returns a current around 0 mA

- PWM\_SENSE register returns a PWM period around 130 µs depending on the time frame when open fault has been executed

- TMOUT bit is set '1' sometimes

#### In slave channel CHX+1:

- In CHX+1 EXCEPTIONS1 Solenoid ADC Mismatch bit is set

- In CHX+1\_EXCEPTIONS1 LS\_Clamp\_Active is set '1'

AN5672 - Rev 1 page 22/36

- In CHX+1\_EXCEPTIONS2 HS-LS\_Compare\_fault bit is set

- AVGCUR register returns a current around 300 mA

- PWM\_SENSE register returns a PWM period around 130 µs depending on the time frame when open fault has been executed

- TMOUT bit is set '1' sometimes

Once the connection on Vs\_solX of both master (CHX) and slave channel (CHX+1) is restored, user should read LS\_Clamp\_Active bit in EXCEPTIONS1 register of both master (CHX) and slave channel (CHX+1) and then set DriveState\_CHX[1:0] and DriveState\_CHX+1[1:0] to '10', in order to the solenoid driver couple get back working as before the fault was injected.

- If only master channel CHX LS\_Clamp\_Active bit in EXCEPTIONS1 register is read and both channels are attempted to be re-enabled → master channel is re-enabled and it provides load with global couple setpoint + 100 mA current (NOK).

- Slave channel remains tri-stated and provides no current until its LS\_Clamp\_Active bit is read and cleared. After slave channel LS\_Clamp\_Active bit is cleared on read, the couple CHX (master) and CHX+1 (slave) operate properly.

- If only slave channel CHX+1 LS\_Clamp\_Active bit in EXCEPTIONS1 register is read and both channels are attempted to be re-enabled → both channels of the couple cannot be re-enabled and are kept tri-stated, until master channel CHX LS\_Clamp\_Active bit in EXCEPTIONS1 register is read and cleared.

- After master channel LS\_Clamp\_Active bit is cleared on read, the couple CHX (master) and CHX+1 (slave) operate properly.

When only Vs\_solX connection of master (CHX) channel is restored:

- If only master channel CHX LS\_Clamp\_Active bit in EXCEPTIONS1 register is read and both channels are attempted to be re-enabled → master channel is re-enabled and it provides load with global couple setpoint + 100 mA current (NOK).

- Slave channel remains tri-stated and provides no current until its LS\_Clamp\_Active bit is read and cleared. After slave channel LS\_Clamp\_Active bit is cleared on read, the couple CHX (master) and CHX+1 (slave) operate as in **Case B**.

- If only slave channel CHX+1 LS\_Clamp\_Active bit in EXCEPTIONS1 register is read and both channels are attempted to be re-enabled → both channels of the couple cannot be re-enabled and are kept tri-stated, until master channel CHX LS\_Clamp\_Active bit in EXCEPTIONS1 register is read and cleared. After master channel LS\_Clamp\_Active bit is cleared on read, the couple CHX(master) and CHX+1(slave) operate the same as in Case B.

When only Vs\_solX connection of slave (CHX+1) channel is restored:

- If only master channel CHX LS\_Clamp\_Active bit in EXCEPTIONS1 register is read and both channels are attempted to be re-enabled → master channel is re-enabled and it provides load with global couple setpoint + 100 mA current (NOK).

- Slave channel remains tri-stated and provides no current until its LS\_Clamp\_Active bit is read and cleared. After slave channel LS\_Clamp\_Active bit is cleared on read, the couple CHX (master) and CHX+1 (slave) operate as in **Case A**.

- If only slave channel CHX+1 LS\_Clamp\_Active bit in EXCEPTIONS1 register is read and both channels are attempted to be re-enabled → both channels of the couple cannot be re-enabled and are kept tri-stated, until master channel CHX LS\_Clamp\_Active bit in EXCEPTIONS1 register is read and cleared. After master channel LS\_Clamp\_Active bit is cleared on read, the couple CHX (master) and CHX+1 (slave) operate the same as in Case A.

AN5672 - Rev 1 page 23/36

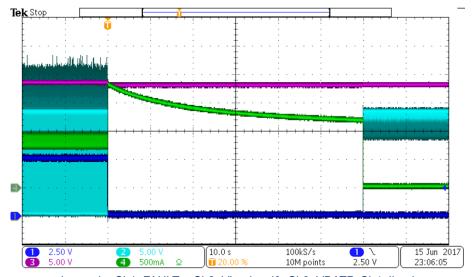

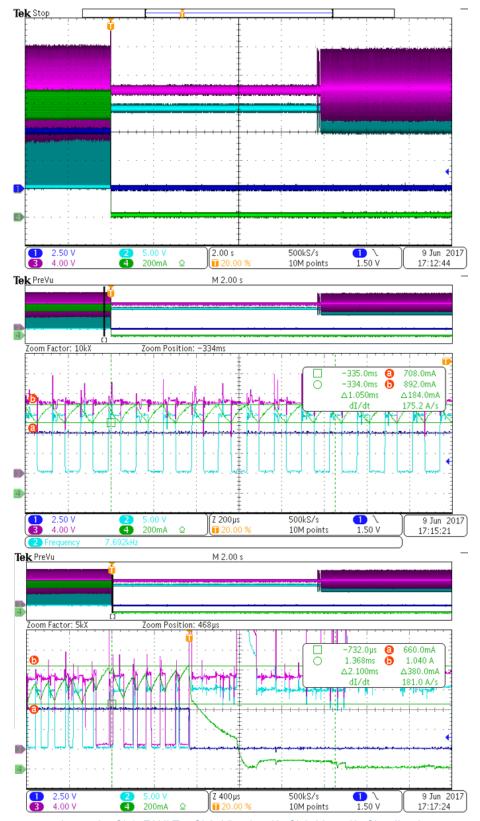

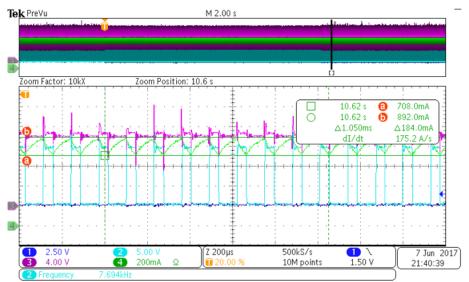

Figure 8. Vs\_solX connection open on both master and slave channels - LS\_Clamp\_Active bit unmasked

Legenda: Ch1: FAULTn, Ch2: Vload\_sol0, Ch3: Vs\_sol0, Ch4: Iload

AN5672 - Rev 1 page 24/36

## 2.3 Loss of load ground connection diagnostic

In the following analysis the loss of GND\_solX pin will be considered while L9305 is operating parallel mode. The following SPI register is involved for such a diagnostic.

**Exceptions 2 - EXCEPTIONS2**

Address Channel\_X\_BaseAddress + 0x01

Type Read Only

Description Solenoid Driver Fault Status

Table 15. EXCEPTIONS2 register detail

| Register bit | Field name/description                  | Default values | Туре          |  |

|--------------|-----------------------------------------|----------------|---------------|--|

| [15:6]       | Unused                                  | All "0"        | Read          |  |

|              | GND_SOL Loss Self Test Status           |                |               |  |

| [5]          | 0: Test Complete                        | 0              | Clear on Read |  |

|              | 1: Test Running                         |                |               |  |

|              | Out of regulation                       |                |               |  |

| [4]          | 0: No Fault                             | 0              | Clear on Read |  |

|              | 1: Out of Regulation After 8 PWM Cycles |                |               |  |

| [3]          | GND_SOL loss fault                      |                |               |  |

|              | 0: No Fault                             | 0              | Clear on Read |  |

|              | 1: Solenoid Ground Loss Detected        |                |               |  |

|              | RAM CRC error                           |                |               |  |

| [2]          | 0: No Fault                             | 0              | Clear on Read |  |

|              | 1: CRC Fault Detected on RAM Read       |                |               |  |

|              | HS/LS compare Fault:                    |                |               |  |

| [1]          | 0: No Fault                             | 0              | Clear on Read |  |

|              | 1: Fault Detected                       |                |               |  |

| [0]          | Configuration Register Monitor:         |                |               |  |

|              | 0: No Fault                             | 0              | Clear on Read |  |

|              | 1: Fault Detected                       |                |               |  |

## 2.3.1 Loss of GND\_solX Connection - parallel solenoid driver channels configuration

General test case settings:

- SR for Vload\_solX voltage: CONFIGURATION1, D[1:0] = 11  $\rightarrow$  8 V/ $\mu$ s

- Current set point for each channel 0.4 A, SETPOINT, D[12:0] = 640h: total current in the load 0.8 A

- PWM control frequency = 8 KHz (7.692 KHz), CTRLCFG, D[10:0] = 0Dh

When solenoid load ground loss is induced on either master (CHX) or slave (CHX+1) channel of the couple, the following scenario occurs in both cases.

• Channel X and Channel X+1 (couple of channels under test) currents go to 0 A, as soon as GND\_solX connection is broken; other couple of channels go on operating normally.

AN5672 - Rev 1 page 25/36

- During GND\_solX interruption:

- For the couple of channels under test SOLENDR register DriverState\_CHX and DriverState\_CHX+1

are set '01' → CHX and CHX+1 of the same couple are put tristate

- For the couple of channels under test, CHX\_AVGCUR = 0 DEC (0 HEX) fix and CHX+1\_AVGCUR = 0 DEC (0 HEX) fix → a current of 0 mA is internally sensed

- CHX\_PWMSENSE and CHX+1\_PWMSENSE return a PWM period, which is randomly different every time the test is repeated, but it is fix if PWM period readings are repeated more times during the same test (NOK). This is due to the fact that by construction asynchronous open GND\_solX or GND\_solX+1 event occurs during PWM and affects PWM period calculation.

- TMOUT bit is set for both channels of the couple under test.

- By monitor circuit architecture, GND\_SOL\_loss\_fault bit is set, but it is cleared on read even if GND\_solX connection is still broken (NOK).

Nevertheless there is the following difference when the load ground loss fault is injected on either the master channel or the slave channel of the couple.

When load GND loss test is executed on master solenoid driver channel of the couple (CHX):

- If GND\_solX connection is still broken and only slave solenoid driver channel is attempted to be re-enabled before or after reading GND\_SOL\_loss\_fault bit of master channel, slave channel CHX+1 is re-enabled and it provides load with only its set-point current (**NOK**).

- If GND\_solX connection is still broken, both channels of the couple cannot be re-enabled even if the GND\_SOL\_loss\_fault bit has been read: when re-enable of both channel of the couple is attempted, none of the channels of the couple is enabled and master channel GND\_SOL\_loss\_fault bit is set again even if it has been cleared on read.

- Master channel CHX GND\_SOL\_loss\_fault bit is set again even if it has been cleared on read and both channels are kept tristate.

- After the connection is restored, Channel X needs GND\_SOL\_loss\_fault bit to be read and DriverState\_CHX/CHX+1 to be set '10', in order to the couple CHX and CHX+1 operate parallel mode properly.

When GND loss test is executed on slave solenoid driver channel of the couple (CHX+1):

- If GND\_solX+1 connection is still broken and only master solenoid driver channel is attempted to be re-enabled before or after reading GND\_SOL\_loss\_fault bit of slave channel, master channel is re-enabled and it provides load with only its setpoint current (**NOK**).

- If GND\_solX+1 connection is still broken and both channels of the couple are attempted to be re-enabled before or after the GND\_SOL\_loss\_fault bit has been cleared on read: master channel is re-enabled and it provides load with global couple setpoint + 100 mA current (NOK).

- Slave channel GND\_SOL\_loss\_fault bit is set again even if it has been cleared on read and if it is read, master channel is put tristate again.

- If GND\_solX+1 connection is restored and both channels of the couple are attempted to be re-enabled before the GND\_SOL\_loss\_fault bit has been cleared on read: master channel is re-enabled and it provides load with global couple setpoint + 100 mA current (NOK). Slave channel remains tri-stated and provides no current until its GND\_SOL\_loss\_fault bit is read and cleared.

- After Slave channel GND\_SOL\_loss\_fault bit is cleared on read, the couple CHX (master) and CHX+1 (slave) operate properly.

- After the connection is restored, Channel X+1 needs GND\_SOL\_loss\_fault bit to be read and DriverState\_CHX/CHX+1 to be set '10', in order to the couple CHX and CHX+1 operate properly.

In order to guarantee proper operation of the parallel solenoid driver channels couple, external MCU must always read GND\_SOL\_loss\_fault bit before and after each couple re-enable attempt.

If GND\_SOL\_loss\_fault bit is unmasked, then FAULTn goes low when GND\_solX is unconnected: it needs GND\_SOL\_loss\_fault bit to be read for FAULTn getting back high.

AN5672 - Rev 1 page 26/36

Figure 9. GND\_solX connection open - GND\_SOL\_loss\_fault bit unmasked

Legenda: Ch1: FAULTn, Ch2: GND\_sol0, Ch3: Vload\_sol0, Ch4: Iload\_sol0

AN5672 - Rev 1 page 27/36

Figure 10. GND\_solX connection open - GND\_solX voltage details

Legenda: Ch1: FAULTn, Ch2: GND sol0, Ch3: Vload sol0, Ch4: Iload sol0

#### 2.4 Loss of load connection

Loss of load connection during parallel mode operation is analyzed, when driver channels are on. There is no ON Diagnostic managing open load connection.

#### 2.4.1 Loss of load connection - parallel solenoid driver channels

General test case settings:

- SR for Vload\_solX voltage: CONFIGURATION1, D[1:0] = 11 → 8 V/µs

- Current set point for each channel 0.4A, SETPOINT, D[12:0] = 640h: total current in the load 0.8 A

- PWM control frequency = 8KHz (7.692KHz), CTRLCFG, D[10:0] = 0Dh

Case A: Open fault executed on Load\_solX connection of the master channel (CHX) of the solenoid driver couple.

Master Channel X current goes to 0 A, as soon as load connection is broken and the whole load driver couple current is sustained by the slave channel (CHX+1); other couple channels go on operating normally.

During load connection interruption, for master CHX:

- CHX AVGCUR =  $4 \div 16380$  DEC (3FFC HEX) fix  $\rightarrow$  a current of -1 $\div 1$  mA is internally sensed

- PWM period of 130 is sensed by CHX\_PWMSENSE

- TMOUT bit is not set

During load connection interruption, for slave CHX+1:

- PWM period of 130 is sensed by CHX+1\_PWMSENSE

- TMOUT bit is not set

- · Out of regulation bit is set

After the connection is restored, Channel X automatically re-starts operating the same way as before interruption without any re-enabling step.

Case B: Open fault executed on Load\_solX+1 connection of the slave channel (CHX+1) of the solenoid driver couple.

Slave Channel X+1 current goes to 0 A, as soon as load connection is broken and the whole load driver couple current is sustained by the master channel CHX; other couple channels go on operating normally.

During load connection interruption, for master CHX:

- CHX AVGCUR≈3200 DEC (C80 HEX) --> a current around 800 mA is internally sensed

- PWM period of 130 is sensed by CHX\_PWMSENSE

AN5672 - Rev 1 page 28/36

TMOUT bit is not set

During load connection interruption, for slave CHX+1:

- CHX+1\_AVGCUR =  $4\div16380$  DEC (3FFC HEX) fix  $\rightarrow$  a current of -1 $\div1$  mA is internally sensed

- PWM period of 130 is sensed by CHX+1\_PWMSENSE

- TMOUT bit is not set

- Out of regulation bit is set

After the connection is restored, Channel X+1 automatically re-starts operating the same way as before interruption without any re-enabling step.

In both cases Out of regulation bit is set on slave CH\_X+1 EXCEPTIONS2 register.

If Out\_of\_regulation bit is unmasked, then FAULTn goes low when Fail Safe switch is unconnected: it needs Out\_of\_regulation bit to be read for FAULTn getting back high.

AN5672 - Rev 1 page 29/36

Figure 11. Load connection open - Out\_of\_regulation bit unmasked

Legenda: Ch1: FAULTn, Ch2: Vs\_sol0, Ch3: Vload\_sol0, Ch4: Iload\_sol0

AN5672 - Rev 1 page 30/36

Figure 12. Load connection open restored - Out\_of\_regulation bit unmasked

Legenda: Ch1: FAULTn, Ch2: Vs\_sol0, Ch3: Vload\_sol0, Ch4: Iload\_sol0

AN5672 - Rev 1 page 31/36

# **Revision history**

Table 16. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 28-Apr-2021 | 1       | Initial release. |

AN5672 - Rev 1 page 32/36

# **Contents**

| 1  | Sole   | noid dr  | iver channels parallel mode operation                                         | 2  |

|----|--------|----------|-------------------------------------------------------------------------------|----|

|    | 1.1    |          | el registers configuration details                                            |    |

|    | 1.2    | Setup    | recommendations                                                               | 9  |

|    |        | 1.2.1    | Minimum Current Setpoint calculation                                          | 9  |

|    | 1.3    | Operat   | tive hints                                                                    | 10 |

|    |        | 1.3.1    | Channel enabling                                                              | 10 |

|    |        | 1.3.2    | Load connection                                                               | 10 |

| 2  | Para   | illel mo | de operation - faults and diagnostic management details                       | 12 |

|    | 2.1    | Overcu   | urrent Protection                                                             | 12 |

|    |        | 2.1.1    | Load_solX pin short to VBATP                                                  | 13 |

|    |        | 2.1.2    | Load_solX pin short to ground                                                 | 17 |

|    | 2.2    | Low Si   | ide Clamping protection                                                       | 21 |

|    |        | 2.2.1    | Loss of Vs_solX connection - parallel solenoid driver channels configuration  | 22 |

|    | 2.3    | Loss o   | f load ground connection diagnostic                                           | 25 |

|    |        | 2.3.1    | Loss of GND_solX Connection - parallel solenoid driver channels configuration | 25 |

|    | 2.4    | Loss o   | f load connection                                                             | 28 |

|    |        | 2.4.1    | Loss of load connection - parallel solenoid driver channels                   | 28 |

| Re | vision | history  |                                                                               | 32 |

AN5672 - Rev 1 page 33/36

# **List of tables**

| Table 1.  | SERVENA register detail         |

|-----------|---------------------------------|

| Table 2.  | SETPOINT register detail        |

| Table 3.  | CTRLCFG register detail         |

| Table 4.  | KGAINS register detail          |

| Table 5.  | KFREQCTRL register detail       |

| Table 6.  | DITHPGM1 register detail        |

| Table 7.  | DITHPGM2 register detail        |

| Table 8.  | CONFIGURATION1 register detail  |

| Table 9.  | CONFIGURATION2 register detail  |

| Table 10. | EXCEPTIONS1 register detail     |

| Table 11. | OVC test A, monitored variables |

| Table 12. | OVC test B, monitored variables |

| Table 13. | STG test A, monitored variables |

| Table 14. | STG test B, monitored variables |

| Table 15. | EXCEPTIONS2 register detail     |

| Table 16. | Document revision history       |

# **List of figures**

| Figure 1.  | Load connection in parallel mode                                                         | 10 |

|------------|------------------------------------------------------------------------------------------|----|

| Figure 2.  | Vload_sol0 short to VBATP - Load current                                                 | 15 |

| Figure 3.  | Vload_sol1 short to VBATP - Load current                                                 | 17 |

| Figure 4.  | Vload_sol0 short to GND                                                                  | 18 |

| Figure 5.  | Vload_sol0 short to GND - Load current details                                           | 19 |

| Figure 6.  | Vload_sol1 short to GND                                                                  | 20 |

| Figure 7.  | Vload_sol1 short to GND - Load current details                                           | 21 |

| Figure 8.  | Vs_solX connection open on both master and slave channels - LS_Clamp_Active bit unmasked | 24 |

| Figure 9.  | GND_solX connection open - GND_SOL_loss_fault bit unmasked                               | 27 |

| Figure 10. | GND_solX connection open - GND_solX voltage details                                      | 28 |

| Figure 11. | Load connection open - Out_of_regulation bit unmasked                                    | 30 |

| Figure 12. | Load connection open restored - Out_of_regulation bit unmasked                           | 31 |

AN5672 - Rev 1 page 35/36

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2021 STMicroelectronics - All rights reserved

AN5672 - Rev 1 page 36/36