# Design recommendations for the EMC reduction due to SMPS on SPC58 Lines

#### Introduction

STMicroelectronics SPC58 device lines can use either a 3.3 or 5 V operating supply, which is fed by all the high voltage pins (the ones named VDD\_HV\_\*). A number of different voltage regulators can provide the 1.2 V power supply (VDD\_LV) used by the digital portion of the device. This application note will analyse the use of switched-mode regulators available in the SPC58 E Line (only eLQFP176) and SPC58 N Line only, and provide general recommendations for the component design.

SMPS is *by far* the biggest contributor to the electromagnetic emissions of a system, so most of the optimization aims at reducing the emissions at the expense of conversion efficiency. Some constraints to drive the choice of the components value will be presented, but the process of fine-tuning the electromagnetic compatibility (EMC) is largely an empiric one. The best approach is to leave on the printed circuit board some open spots where different components can be soldered, and then measure their impact on system performance.

### 1 Basic Reference Circuit

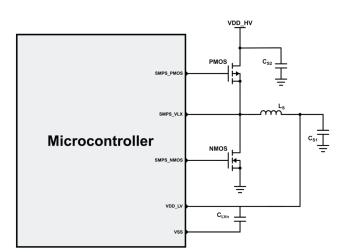

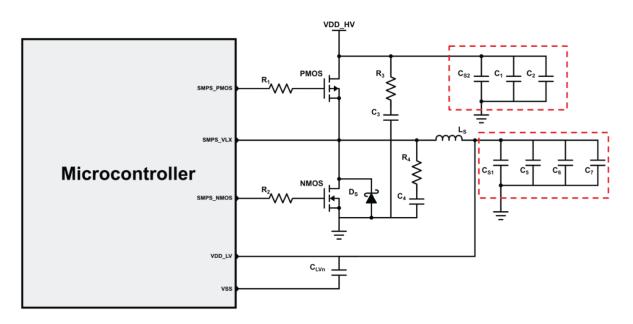

The Figure 1 shows the minimal external network needed to have a working SMPS.

Figure 1. Basic reference circuit

Table 1. Recommended values

| Symbol   | Parameter                            | Min.        | Тур.  | Max. | Unit |

|----------|--------------------------------------|-------------|-------|------|------|

| PMOS     | Recommended PMOS transistor          | PMPB100XPEA |       |      |      |

| NMOS     | Recommended NMOS transistor          | PMPB55XNEA  |       |      |      |

| CS2      | External capacitance on HV supply(1) | -50%        | 47(2) | 35%  | μF   |

| Option A |                                      |             |       |      |      |

| CS1      | External capacitance on LV supply(1) | -50%        | 2×10  | 35%  | μF   |

| LS       | External inductance                  | -30%        | 10    | 30%  | μΗ   |

| Option B |                                      |             |       |      |      |

| CS1      | External capacitance on LV supply(3) | -35%        | 3×10  | 35%  | μF   |

| LS       | External inductance                  | -30%        | 4.7   | 30%  | μΗ   |

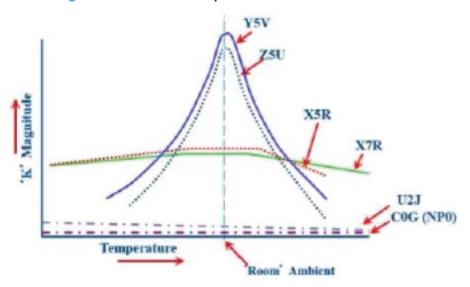

The Figure 2 shows how the operating temperature affects the capacitance of some notable classes of components. The capacitors used for CS1 and CS2 should have a reasonably good stability over temperature, so a Class 2 part (either an X7R or an X5R ceramic capacitor) is recommended.

AN5516 - Rev 2 page 2/13

Figure 2. Variance over temperature for several device classes

The value given for CS2 is a ballpark recommendation, and the application designer should tweak it basing on the external regulator and the EMC requirements.

AN5516 - Rev 2 page 3/13

#### 2 General EMC considerations

The two external transistors in the Figure 1 continuously switch between saturation and cut-off states, where dissipation is low, and spend very little time in the high dissipation active state, which minimizes wasted energy. However, this constant switching causes voltage and current spikes, that provoke high electromagnetic emissions. To comply with EMC restrictions, it is usually necessary to make the transition between saturation and cut-off smoother, at the expense of a reduced power efficiency.

The SMPS circuit is *by far* the main source of electromagnetic emissions in a typical design, so special attention is necessary to minimize them. As a general note, *connections should be kept as short as possible*, in order to keep the parasitic impedance as low as possible. In particular, CS2 should be as close as possible to the SoC.

#### 2.1 Limiting injected noise

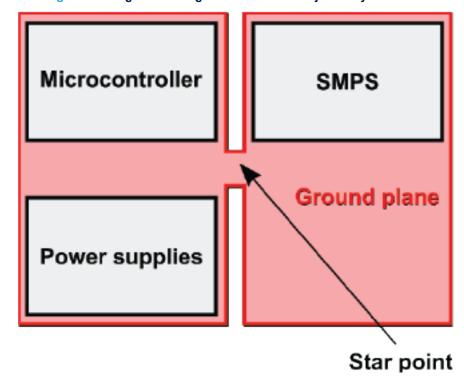

Circuit boards usually use a very large ground plane rather than thin strips among ground connections, as the latter can act as antennas and emit or receive an unacceptable amount of electromagnetic waves. A ground plane also offers a very low impedance, so that all ground pins are at a very close potential. However, a single ground plane will also allow the noise generated by constant SMPS switching to flow freely into other power sources.

To limit the amount of injected noise, it is recommended to use galvanic separation of the ground planes, joining them in a single point. This technique is known as *star routing*. The common ground or *star point* must be on the NMOS source.

Figure 3. Using star routing to limit the noise injected by the SMPS

#### 2.2 Some assembly required

All connections should be kept very short, in order to limit their parasitic impedance. In particular, CS2 should be as close as possible to the SoC.

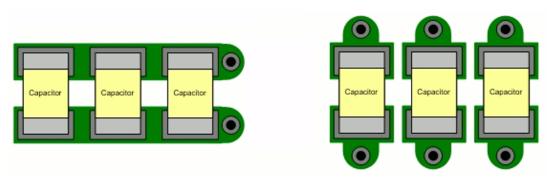

To reduce the assembly inductance of the capacitors, multi-vias connections should be preferred. The Figure 4 shows a single-via connection on the left and a multi-vias one on the right:

AN5516 - Rev 2 page 4/13

Figure 4. Single-via vs multi-vias connection

The SMPS components should be surrounded by a guard ring extended on all the PCB layers, with frequent vias connecting the layers. This will act as a Faraday cage to shield the rest of the coplanar conductors.

The VLX and the MOSFET gate traces should also be shielded. The topology of the board usually makes a full guard ring unfeasible, but placing some grounded traces that run in parallel can help.

AN5516 - Rev 2 page 5/13

## 3 Improving the circuit

To improve the EMC performance of an SMPS design, more components can be added to the board, so that noise is filtered and spikes are limited. This will cause increased cost and less efficiency, so the best approach is usually to try several combinations of components and measure the resulting emissions and the dissipated power. Then choose the cheapest solution that still meets the EMC targets. However, some guidelines are useful to have a starting point.

The Figure 5 shows a reference circuit with a number of improvements that will be discussed in this chapter:

Figure 5. Circuit with improvements for EMC

The value of the capacitance at the input and output of the regulator should still abide the one given in Table 1. Recommended values, so that the total value of the capacitors in the dashed boxes must be the same as the one given in the datasheet for CS1 and CS2.

#### 3.1 Reactive components

The first problem to be addressed is to prevent **ground bouncing**, which occurs when the rush of current on any change in state of the transistors causes the source voltage to rise.

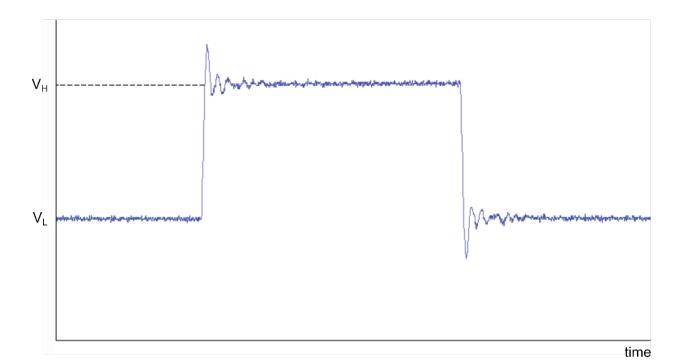

This may briefly lower the VGS, causing some spurious state switches before the system settles down:

AN5516 - Rev 2 page 6/13

Figure 6. Ground bounces can cause oscillations when transistors change state

In order to reduce the ground bounces, the loops embracing the two transistors must have the same impedance, considering the parasitic effects as well. Each loop goes from the output of the SMPS circuit to the ground through the source terminal of each MOSFET: $C_{S2} + C_{PMOS} + C_L + C_{S1} = C_{NMOS} + C_L + C_{S1} \Rightarrow C_{S2} + C_{PMOS} = C_{NMOS}$

In the previous equation, CPMOS and CNMOS are the parasitic capacitance between source and drain of the transistors, and CL is the parasitic capacitance of the inductor LS.

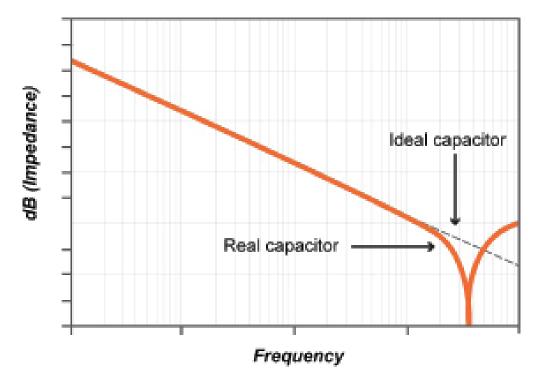

The capacitors in parallel with CS1 and CS2 are used to filter out the high frequency components, so they need to have a *self-resonance frequency* as high as possible. Ideally, the impedance of a capacitor will decrease linearly as frequency increases, but at some point the impedance due to the parasitic inductance of the component becomes prevalent, and the value starts rising again. The self-resonance frequency is the frequency where the total impedance of the component is the lowest.

AN5516 - Rev 2 page 7/13

Figure 7. Impedance as a function of frequency in an ideal vs. real capacitor

These capacitors usually have sizes between 47 and 100 nF and very low equivalent series resistance and inductance, possibly less than 5 m $\Omega$  and 600 pH, respectively.

#### 3.2 Resistive components

The resistors R1 and R2 placed at the gate of each MOSFET form an RC filter with their own parasitic capacitance, which limits the slew rate of the voltage. This improves the EMC performance at the expense of an increased dissipation. The value of these resistors depends on the specifics of the board design, but it is usually between 10 and 100  $\Omega$ .

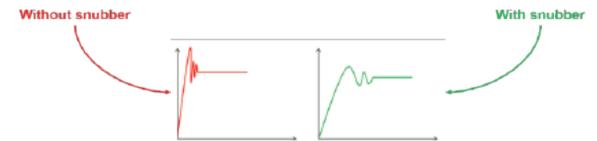

The RC branches and the Schottky diode form a snubber circuit that lowers the amplitude and frequency of the voltage spike that occurs as the device turns on and off. The RC filters reduce the efficiency of the SMPS circuit but are usually necessary. The Schottky diode is often omitted in typical SPC58x family applications.

Figure 8. Impact of the snubber network on the slew rate at the drain of the MOSFETs

The values of the snubber components depend on the parasitic values of the layout board and are often determined with an empiric trial-and-fix procedure. Some reasonable values to start from are 10–100  $\Omega$  for the resistors and 470 pF–2.2 nF for the capacitors.

AN5516 - Rev 2 page 8/13

## **Revision history**

**Table 2. Document revision history**

| Date        | Version | Changes                      |

|-------------|---------|------------------------------|

| 11-Feb-2021 | 1       | Initial release.             |

| 04-May-2022 | 2       | Updated title in cover page. |

| 04-Way-2022 |         | Updated Introduction.        |

AN5516 - Rev 2 page 9/13

## **Contents**

| 1   | Basi  | c Reference Circuit     | . 2 |

|-----|-------|-------------------------|-----|

| 2   | Gene  | eral EMC considerations | . 4 |

|     |       | Limiting injected noise |     |

|     | 2.2   | Some assembly required  | 4   |

| 3   | Impr  | oving the circuit       | . 6 |

|     | 3.1   | Reactive components     | 6   |

|     | 3.2   | Resistive components    | 8   |

| Rev | ision | history                 | 9   |

## **List of tables**

| Table 1. | Recommended values        | 2 |

|----------|---------------------------|---|

| Table 2. | Document revision history | ć |

AN5516 - Rev 2 page 11/13

# **List of figures**

| Figure 1. | Basic reference circuit                                                    | 2 |

|-----------|----------------------------------------------------------------------------|---|

| Figure 2. | Variance over temperature for several device classes                       | 3 |

| Figure 3. | Using star routing to limit the noise injected by the SMPS                 | 4 |

| Figure 4. | Single-via vs multi-vias connection                                        | 5 |

| Figure 5. | Circuit with improvements for EMC                                          | 6 |

| Figure 6. | Ground bounces can cause oscillations when transistors change state        | 7 |

| Figure 7. | Impedance as a function of frequency in an ideal vs. real capacitor        | 8 |

| Figure 8. | Impact of the snubber network on the slew rate at the drain of the MOSFETs | 8 |

AN5516 - Rev 2 page 12/13

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics – All rights reserved

AN5516 - Rev 2 page 13/13