# How to implement adaptive synchronous rectification in flyback converters using STM32 MCUs

#### Introduction

Synchronous Rectification (SR) is widely used in power supply converters to improve efficiency, reduce conduction losses and thermal dissipation, improving user experience in high power applications as well as in portable or hand-held devices.

Flyback converters have relatively high peak and RMS currents, which may cause high conduction losses in the output diode rectifier. Synchronous Rectification can reduce these losses and improve the efficiency of the overall power supply.

Substituting diode rectifiers with power MOSFETs in SR reduces power losses and thermal heating in converters because of their very low R<sub>DSON</sub> compared with the voltage drop across diodes, including Schottky diodes.

SR, however, requires additional electronics to drive the MOSFETs: a sensing network to detect when the MOSFET must be turned on or a dedicated IC to control MOSFET switching, and an on-board microcontroller for digital solutions.

## Synchronous rectification in flyback topology

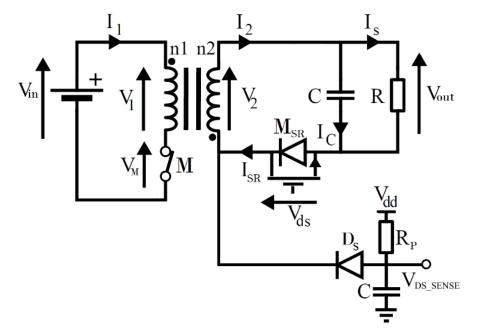

The following figure shows the synchronous rectification technique applied in flyback topology, using a power MOSFET as the rectifier and corresponding  $V_{DS}$  sensing circuitry with a filter capacitor.

Figure 1. Synchronous rectification and V<sub>DS</sub> sense circuitry operating principle

When the flyback converter primary switch is turned off, the voltage across the transformer reverses, the  $M_{SR}$  drain voltage drops quickly decreases to negative and the  $M_{SR}$  body diode starts conducting.

The synchronous rectification control logic is triggered by the falling edge of the  $M_{SR}$   $V_{DS}$  and generates a signal to turn  $M_{SR}$  on, thus reducing conduction losses as the current flows through the MOSFET channel with a lower impedance path. After MOSFET turn-on, the  $V_{DS}$  signal changes from the body diode forward voltage to the drop across the MOSFET channel resistance  $R_{DS}$  ON.

When the current flowing through the MOSFET channel decreases to zero, the  $V_{DS}$  voltage rises again and triggers the MOSFET turn-off.

Noise sources such as spikes from active components or flyback transformer leakage inductance can interfere with the  $V_{DS}$  signal and consequently trigger undesired transitions in the SR MOSFET. To increase reliability and avoid short-circuits, a delay is generated before turning the MOSFET on to ensure a safe diode conduction time. Similarly, the MOSFET is turned off to allow the diode conduct briefly before  $V_{DS}$  voltage inversion.

The MOSFET  $T_{ON}$  period should be maximized to reduce the diode conduction time and increase the overall converter efficiency. In this way, SR conduction losses are significantly reduced as the output current flows through the MOSFET channel instead of the rectification diode for most of the time. The power loss therefore decreasea from  $P_{loss\_diode} = V_d \cdot I_{out}$  to  $P_{loss\_MOSFET} = R_{ds\_on} \cdot I_{out}^2$ , where  $R_{ds\_on}$  is very low for SR MOSFETs.

The power converter continues to work even if the SR MOSFET is not driven, as rectification is ensured by the MOSFET body diode.

Appropriate MOSFET driving when the body diode is forward biased can generally improve system peak efficiency by 3% to 4%.

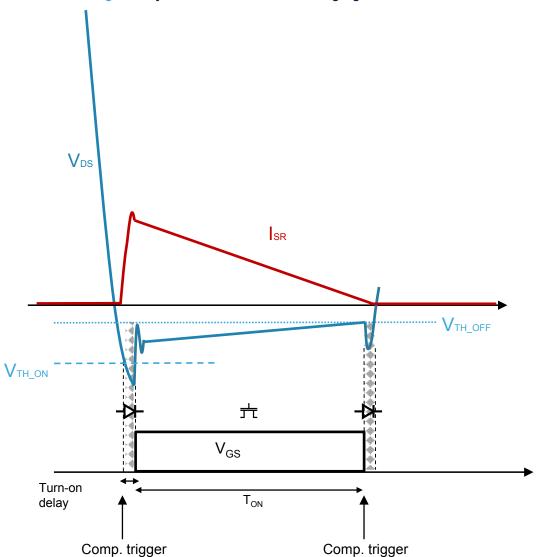

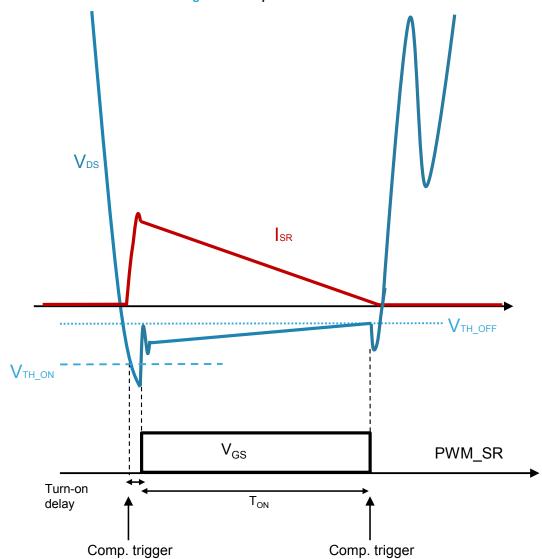

The figure below shows the relative  $V_{DS}$  and  $I_{SR}$  waveforms involved in SR driving, as well as the  $V_{GS}$  signal used to drive  $M_{SR}$ .

AN5499 - Rev 1 page 2/20

Figure 2. Synchronous rectification driving signal waveforms

## 1.1 V<sub>DS</sub> sensing circuit

A sensing circuit for  $V_{\mbox{\footnotesize{DS}}}$  voltage is required to properly drive the MOSFET:

- when the current flows through the body diode and the V<sub>DS</sub> voltage goes negative, the MOSFET must be turned on;

- when the current falls to zero and the V<sub>DS</sub> increases again, the MOSFET must be turned off.

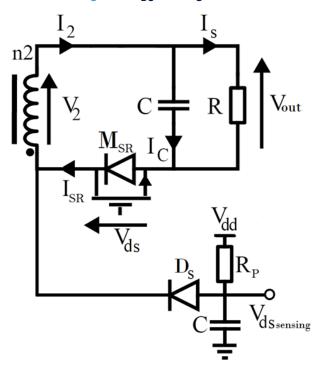

The sensing network shown below can be implemented with a fast Schottky diode and a pull-up resistor connected to the MCU supply voltage:

- when the SR MOSFET drain voltage is greater than V<sub>DD</sub> (the MCU operating voltage), the Schottky diode is reverse biased and the sensed voltage is pulled up to V<sub>DD</sub>

- when the drain voltage is below  $V_{DD}$ , the Schottky diode is forward biased and the sensed voltage is equal to  $V_{DS}$  plus the diode voltage drop that generates a positive voltage shift

AN5499 - Rev 1 page 3/20

Figure 3.  $V_{DS}$  sensing circuit

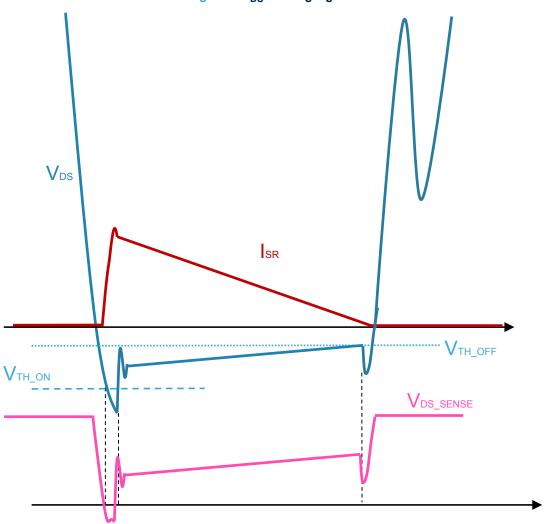

The output of this sensing stage is shown below: the  $V_{DS\_SENSING}$  amplitude is limited to  $V_{DD}$  range and the section where the body diode is forward biased is appropriately shifted and suitable for being sensed.

AN5499 - Rev 1 page 4/20

Figure 4. V<sub>DS</sub> sensing signals

The pull-up resistor limits the current during the diode forward biasing: the pull-up and its associated capacitor (see Figure 1) create a discrete low pass filter that can be used to filter noise on the sensing network.

Two comparators are usually used to detect the beginning and the end of body diode conduction: the first is triggered by the falling edge of  $V_{DS}$  voltage and the second is used to detect the  $V_{DS}$  rise due to a falling  $I_{SR}$ .

As a result, two thresholds could be defined to correctly drive the power MOSFET:

- $\bullet \qquad \text{when $V_{DS}$ decreases below the $V_{TH\_ON}$ threshold, the first comparator is triggered} \\$

- when the second comparator rises above the V<sub>TH OFF</sub> threshold, the MOSFET turns off

During the turn-on time,  $V_{DS} = I_{SR}*R_{DS}$  on and is linear for a flyback converter.

AN5499 - Rev 1 page 5/20

Figure 5. Comparator thresholds

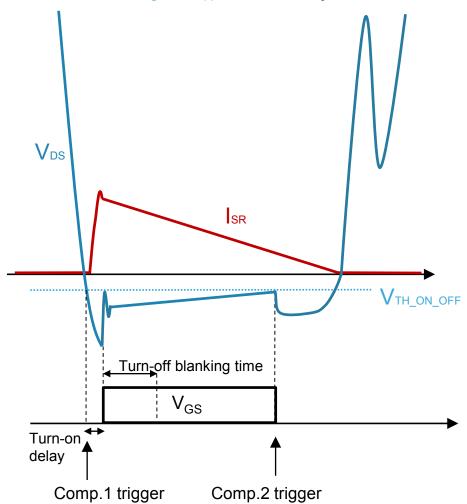

## 1.2 Blanking windows

Once the first comparator has been triggered, the  $V_{GS}$  gate drive output rises to turn  $M_{SR}$  on and performs active rectification. Undesired noises from spikes or oscillations due to commutation can trigger the second comparator and cause erroneous MOSFET switch-off events. A blanking window on the second comparator responsible for  $M_{SR}$  turn-off can be added to avoid false triggering after MOSFET turn-on due to rising voltage, ensuring a minimum turn-on time of the MOSFET.

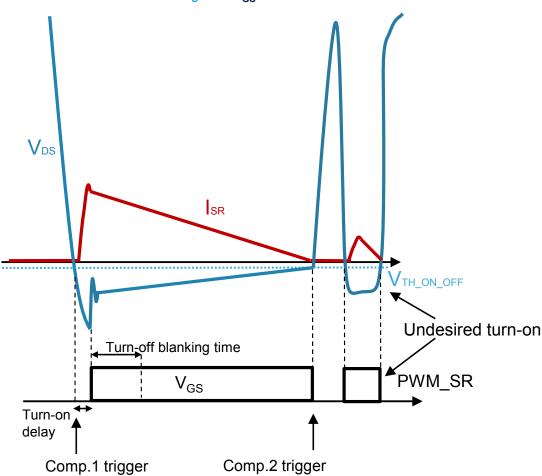

Similar behavior can occur after MOSFET turn-off: the  $V_{DS}$  may fall due to the body diode activation, and voltage ringing could trigger an undesired turn-on due to discontinuous conduction mode at light load, causing the output capacitor to discharge. A blanking window on the first comparator (responsible for  $M_{SR}$  turn-on) can be added after the second (turn-off) trigger event, ensuring a minimum turn-off time.

If blanking windows are properly defined, the same threshold value can be used for both comparators  $(V_{TH\ ON}=V_{TH\ OFF}=V_{TH\ ON\ OFF})$ .

AN5499 - Rev 1 page 6/20

## 2 Adaptive SR algorithm

If the turn-off threshold is too low,  $V_{GS}$  is turned off too early and the positive current causes body conduction to lower the efficiency.

If the turn-off threshold is too high,  $V_{GS}$  is turned off too late and the MOSFET is forced to conduct even if the diode is reverse biased, causing shoot-through and voltage ringing that can cause the diode to turn on again (as well as an undesired PWM turn-on if the blanking time is not properly set) and possible damage to the devices involved.

Figure 6. V<sub>GS</sub> turned off too early

AN5499 - Rev 1 page 7/20

Figure 7. V<sub>GS</sub> turned off too late

In flyback converters, signal shapes and timing may vary according to many parameters, including output load and voltage, input voltage and switching frequency. Fixed frequency flyback converters may change operation from discontinuous conduction mode (DCM) operation at light loads to continuous conduction mode (CCM) operation at heavier loads. Variable frequency converters during quasi resonant (QR) operation (with or without valley skipping) are subject to resonance due to primary inductance and total parasitic capacitance across the primary switch after transformer demagnetization.

Most controllers on the market also use operating frequency modulation to optimize EMI filters.

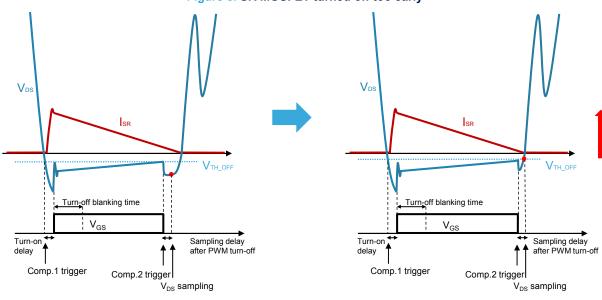

An adaptive synchronous rectification (ASR) algorithm minimizes body diode conduction time and maximizes converter efficiency. In this ST patented adaptive algorithm, the MOSFET  $T_{ON}$  duration is automatically maximized regardless of the parametric tolerances and load variations.

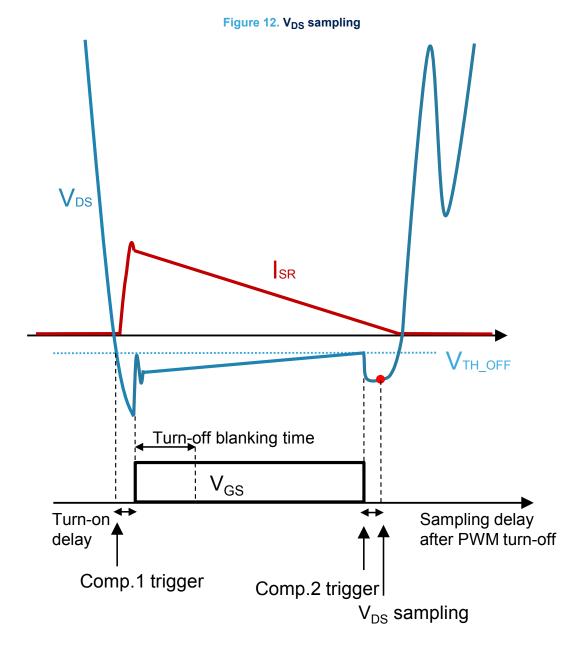

It is possible to determine whether the turn-off threshold setting is appropriate by sampling the  $V_{DS}$  from  $V_{GS}$  turn-off, after a delay which is used to correctly sense the  $V_{DS}$  after the MOSFET turn-off. A threshold on the  $V_{DS}$  value can be used:

- if the acquired V<sub>DS</sub> value is lower than the threshold, the SR MOSFET is turned off too early, allowing the diode conduct and consequently losing efficiency, as shown in Figure 8

- if the acquired V<sub>DS</sub> value is higher than the threshold, the SR MOSFET is turned off too late, forcing it to conduct more than necessary, as shown in Figure 9

AN5499 - Rev 1 page 8/20

Figure 8. SR MOSFET turned off too early

Figure 9. SR MOSFET turned off too late VDS  $V_{\text{DS}}$ Isr Turn-off blanking time Turn-off blanking time  $V_{GS}$  $V_{\rm GS}$ Sampling delay after PWM turn-off Turn-on delay Sampling delay after PWM turn-off Turn-on delay Comp.2 trigger  $V_{DS}$  sampling Comp.1 trigger Comp.1 trigger Comp.2 trigger  $\bar{V}_{DS}$  sampling

AN5499 - Rev 1 page 9/20

#### 3 Adaptive synchronous rectification setup

The SR algorithm requires several parameters, including thresholds, timing, MCU peripheral parameters, and V<sub>DS</sub> sensing circuit components associated with the flyback configuration.

The steps below are general guidelines that should be adapted to your specific application.

- Step 1. Set the flyback converter up according to required specifications (output voltage, current, etc.)

- Step 2. Choose the same voltage rating of the Schottky diode of V<sub>DS</sub> sensing network, as the maximum V<sub>DS</sub> and the maximum MOSFET V<sub>DS</sub> on the secondary side are fixed by the flyback topology.

- Step 3. Turn the converter on without any load to determine V<sub>DS</sub> and V<sub>DS\_SENSING</sub> voltages and to tune the sensing circuit (pull-up resistor and filter capacitor).

Note:

Follow this step to also adjust RC parameters and estimate the comparator turn-on threshold and the turn-off blanking time according to  $V_{DS}$  residual ringing.

- Step 4. Turn the TIM\_SR timer on and set a maximum turn-on time equal to or lower than the turn-off blanking time.

- The MOSFET is turned on for a short amount of time regardless of the turn-off threshold.

- Step 5. Gradually increase the turn-on time to reach  $V_{DS}$ , as shown in Figure 2. The turn-off threshold is identified.

- Step 6. Activate the second comparator with the threshold identified in the previous step.

- Step 7. Set the blanking time for the first comparator equal to the turn-off blanking time, taking the V<sub>DS</sub> waveform as reference.

- Step 8. Repeat steps 4-7 with a different output voltage, if available, and for different loads up to the maximum available to check all time parameters and identify turn-off threshold ranges, blanking times, T<sub>ON</sub> range.

- Step 9. Before turning off the adaptive algorithm, check the V<sub>DS</sub> shape and set the time to trigger ADC conversions after MOSFET turn-off.

#### Important:

The adaptive SR algorithm must always start with the lowest turn-off threshold to ensure the safest operating condition, that is  $T_{ON}$  is not optimized and the body diode is conducting for a long period after MOSFET turn-off.

Note: The adaptive SR algorithm can periodically run.

AN5499 - Rev 1 page 10/20

#### 4 Adaptive SR implementation with STM32

The sensing circuit shown in Figure 1 and described in Section 1.1 can provide a V<sub>DS\_SENSING</sub> signal with an amplitude suitable for an MCU domain. This signal must be connected to an analog pin and is connected to the MCU internal comparators, as shown in Figure 10. One or two comparators can be used on the basis of the STM32 comparator availability or user requirements.

When using two comparators, assume the two relevant thresholds ( $V_{TH\_ON}$  and  $V_{TH\_OFF}$ ) are translated into MCU  $V_{DD}$  domain.

The two comparators must be configured in window mode to share the same non-inverting input. The corresponding thresholds are applied to detect the two trigger conditions:

- the V<sub>DS</sub> decreasing below V<sub>TH ON</sub>

- the V<sub>DS</sub> increasing above V<sub>TH OFF</sub>, which means current falling to zero

As shown in Figure 10, the first comparator detects the falling edge and the second detects the turn-off condition.

V<sub>DS\_SENSE</sub>

+ 1° Trigger

V<sub>TH\_OFF</sub>

2° Trigger

Figure 10. Comparator setup

The two thresholds can be generated by the STM32 internal DAC as well as by the available internal reference voltage if suitable.

To actively control the SR MOSFET, the timer (TIM\_SR) PWM output is used and configured in one-pulse mode (OPM). This mode allows starting the counter and generating a single pulse with a programmable length (maximum MOSFET turn-on time) after a programmable delay that corresponds to the turn-on delay.

The first comparator resets and triggers the TIM\_SR that works as the slave. [Reset] reinitializes the counter whereas [Trigger] starts it.

The second trigger output drives the OCxREF\_clr signal to force PWM output to idle state until the end of the programmed period or the next update event: once the second trigger has occurred, the output channel is low until the next update event (SR MOSFET turn-off).

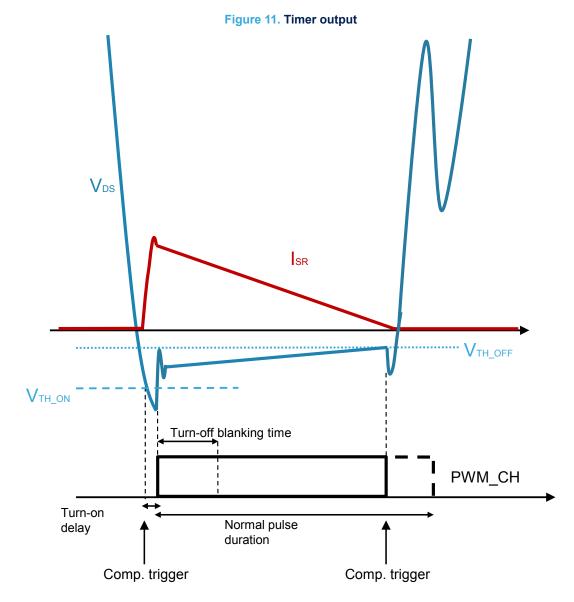

With this timer configuration, each time  $V_{DS}$  falls below  $V_{TH\_ON}$ , it triggers a new PWM signal driving the SR MOSFET up to the second trigger event (see Figure 11. Timer output). The timer and output channel registers (Prescaler, Capture, etc.) must be configured to ensure the longest  $T_{ON}$  period exposed by the flyback converter.

Note: This PWM signal assures that the MOSFET is put in idle state even if comparator events are not detected.

AN5499 - Rev 1 page 11/20

TIM\_SR drives the SR MOSFET using:

- TRG\_CH channel as a trigger to start the counter

- PWM CH channel to drive the SR MOSFET

- OCxREF\_clr signal to clear PWM\_CH channel

If only one comparator is used, set the hardware up to use only one threshold for edge detection to avoid changing the threshold. The comparator output setup can be updated after each trigger event using the available DMA or IRQ as the comparator outputs are internally connected to the EXTI controller.

#### 4.1 Blanking windows in the adaptive SR implementation

As described in Section 1.2 Blanking windows, blanking windows ensure overall robustness and damage prevention. Blanking action must be performed on comparators.

If the STM32 used has no blanking features on the comparators, IRQ handler function called by trigger interrupt must be activated to apply blanking features to the comparator through a dedicated code.

Note: Use a small amount of code (or DMA transfers) as these routines are called upon each trigger event.

If the on-board comparators offer blanking features, they are usually linked to timer channels: an additional channel of TIM\_SR can be used for blanking features. You should set the appropriate period to perform blanking on the comparator by detecting the second trigger event as shown in Figure 11.

AN5499 - Rev 1 page 12/20

When using a channel from the same timer, the blanking time for SR MOSFET turn-on and turn-off are synchronized.

If TIM\_SR also performs the second comparator blanking, it uses:

- TRG\_CH channel as a trigger to start the counter

- PWM CH channel to drive the SR MOSFET

- BLANK2 CH channel to blank the second comparator

- OCxREF signal to clear PWM\_CH channel

Turning the blanking time on avoids undesired MOSFET activation due to  $V_{DS}$  ringing after MOSFET turn-off, by using a second timer (TIM OFF).

Like the TIM\_SR timer, the TIM\_OFF timer should be configured in one-pulse mode (OPM). The trigger output of the second comparator should be used to reset and start it. One channel of this timer can perform a blanking window on the first comparator, focusing on the time duration to ensure the correct setup of turn-on triggers.

TIM\_OFF uses:

- TRG\_CH channel as a trigger to start the counter

- · BLANK1\_CH channel to blank the first comparator

#### 4.2 Adaptive SR algorithm

As described in Section 2 Adaptive SR algorithm, MOSFET body diode conduction time must be minimized to ensure better performance. The optimum MOSFET T<sub>ON</sub> duration can be achieved with an adaptive synchronous rectification (ASR) algorithm regardless of parametric tolerance and load variations.

In the patented ST implementation, MOSFET turn-off is driven by a second comparator using the turn-off threshold ( $V_{TH\_OFF}$ ). It is possible to determine whether turn-off threshold is set correctly by sampling the  $V_{DS}$  after a programmed delay from  $V_{GS}$  turn-off.

A third channel of the TIM\_OFF timer can be used. The timer is triggered by the turn-off event, so you can set another channel to trigger ADC conversion after a specified amount of time. You have to set the appropriate time delay to obtain samples on the first rising edge of the  $V_{DS}$ , avoiding meaningless values sampled on the ringing  $V_{DS}$ . The  $V_{DS}$  voltage suffers from noise and oscillations whose amplitude and frequency depend on too many variables, including hardware setup, load conditions, voltage output, etc. Wrong  $V_{DS}$  samples may prohibit the adaptive algorithm from converging.

When the adaptive SR algorithm is running, the time delay represents the safe diode conduction time after MOSFET turn-off.

If TIM\_OFF also triggers the ADC, it uses:

- TRG\_CH channel as a trigger to start the counter

- BLANK1 CH channel to blank the first comparator

- ADC TRG CH channel to trigger ADC acquisition

AN5499 - Rev 1 page 13/20

AN5499 - Rev 1 page 14/20

### 5 Example of implementation

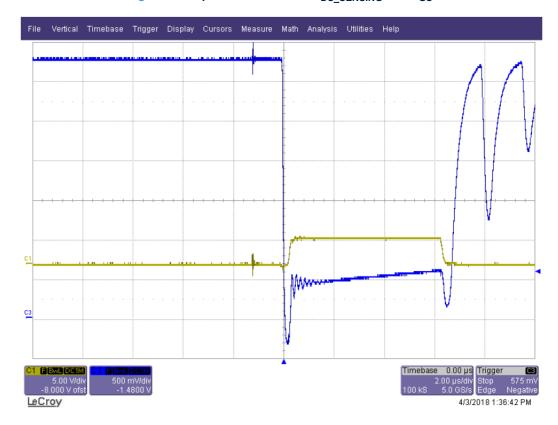

Figure 13 shows an SR cycle of  $V_{DS}$  and  $V_{GS}$  signals in a real use case implementation.

When the  $V_{DS\_SENSING}$  is falling, the TIM\_SR starts and, after the turn-on delay, the PWM signal (in yellow in the figure below) turns the SR MOSFET on. When the MOS is turned on, the voltage drop is lower than the forward voltage drop of the internal body diode. After that, the  $V_{DS}$  and the  $V_{DS\_SENSING}$  (in blue in the figure below) decrease.

To prevent slight oscillation from causing undesired turn-off, the first blanking window is applied.

The current flowing through the device decreases and lowers  $V_{DS}$  and  $V_{DS\_SENSING}$ , approaching the turn-off threshold that drives the TIM\_SR to stop the PWM.

Once the MOS is turned off, enabling the body diode to conduct again, a glitch occurs in the  $V_{DS\_SENSING}$  signal, due to the diode forward voltage.

To avoid MOS turn-on by the glitch and other oscillations in the  $V_{DS}$ , a blanking window at turn-off is applied.

Figure 13. Experimental results: V<sub>DS\_SENSING</sub> and V<sub>GS</sub>

AN5499 - Rev 1 page 15/20

#### 6 Conclusions

The implementation of the Synchronous Rectification algorithm on specific STM32 MCUs with appropriate peripherals can help deliver higher power efficiency, and lower conduction losses and thermal dissipation in end applications.

To fulfill all operating conditions, an adaptive algorithm ensures the best possible performance.

The following elements are key to successful implementation:

- V<sub>DS</sub> sensing stage used to monitor MOSFET operating conditions

- · appropriate comparators used to get triggering events

- the timer driving the SR MOSFET

- blanking windows to protect the application against malfunction

AN5499 - Rev 1 page 16/20

## **Revision history**

**Table 1. Document revision history**

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 23-Jun-2020 | 1       | Initial release. |

AN5499 - Rev 1 page 17/20

## **Contents**

| 1   | Syn    | chronous rectification in flyback topology         | 2  |

|-----|--------|----------------------------------------------------|----|

|     | 1.1    | V <sub>DS</sub> sensing circuit                    | 3  |

|     | 1.2    | Blanking windows                                   | 6  |

| 2   | Ada    | ptive SR algorithm                                 | 7  |

| 3   | Ada    | ptive synchronous rectification setup              | 10 |

| 4   | Ada    | ptive SR implementation with STM32                 | 11 |

|     | 4.1    | Blanking windows in the adaptive SR implementation | 12 |

|     | 4.2    | Adaptive SR algorithm                              | 13 |

| 5   | Exa    | mple of implementation                             | 15 |

| 6   | Con    | clusions                                           | 16 |

| Rev | vision | history                                            | 17 |

## **List of figures**

| Figure 1.  | Synchronous rectification and V <sub>DS</sub> sense circuitry operating principle | . 2 |

|------------|-----------------------------------------------------------------------------------|-----|

| Figure 2.  | Synchronous rectification driving signal waveforms                                | . 3 |

| Figure 3.  | V <sub>DS</sub> sensing circuit                                                   | . 4 |

| Figure 4.  | V <sub>DS</sub> sensing signals                                                   | . 5 |

| Figure 5.  | Comparator thresholds                                                             | . 6 |

| Figure 6.  | V <sub>GS</sub> turned off too early                                              | . 7 |

| Figure 7.  | V <sub>GS</sub> turned off too late                                               | . 8 |

| Figure 8.  | SR MOSFET turned off too early                                                    | . 9 |

| Figure 9.  | SR MOSFET turned off too late                                                     | . 9 |

| Figure 10. | Comparator setup                                                                  | 11  |

| Figure 11. | Timer output                                                                      |     |

| Figure 12. | $V_{DS}$ sampling                                                                 | 14  |

| Figure 13. | Experimental results: V <sub>DS</sub> <sub>SENSING</sub> and V <sub>GS</sub>      | 15  |

|            |                                                                                   |     |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2020 STMicroelectronics - All rights reserved

AN5499 - Rev 1 page 20/20