# L9945 H-Bridge direction switching recommendations

#### Introduction

This document provides recommendation about the timing constraints to be fulfilled in order to allow a smooth direction switching when operating L9945 in H-Bridge configuration.

# 1 DIR switching recommendations

This section contains the description of L9945 H-Bridge controller and its behavior in response to DIR and NPWM input variations. Detailed recommendations about the timing relations between the two signals will be provided, along with recommendations to follow in order to ensure the best switching performances.

AN5402 - Rev 1 page 2/13

### 1.1 Output behavior following DIR & NPWM transitions

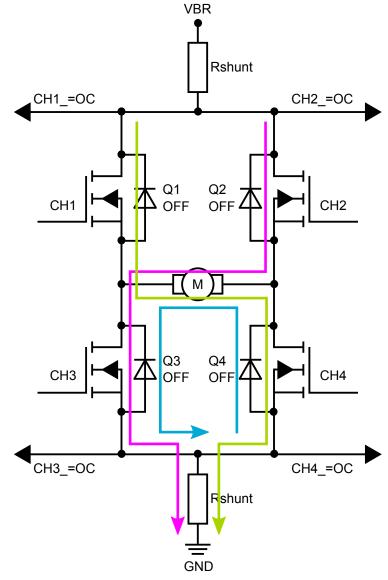

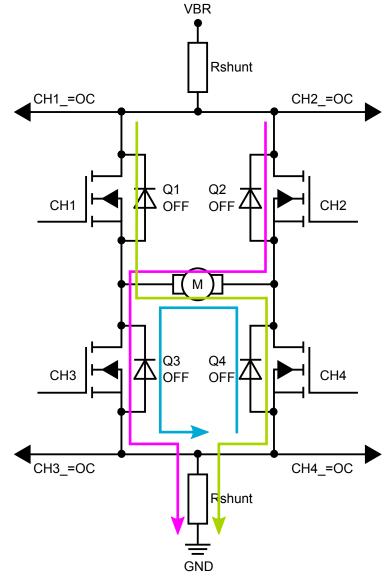

**VBR** Rshunt CH2\_=OC Q1 OFF CH1 OFF 4 CH2 Q3 OFF Q4 CH3 OFF  $\angle$ CH4 CH3\_=OC CH4\_=OC Rshunt **GND**

Figure 1. H-Bridge schematic

Table 1. Output response in case of DIR transition

| DIR transition | Q1/Q5                                                                                               | Q2/Q6                                                                                               | Q3/Q7                           | Q4/Q8                           |

|----------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|

| 0 → 1          | Turns ON after HBx_dead_time, if NPWM was "0" before DIR switch and did not toggle during dead time | Turns OFF immediately                                                                               | Turns OFF immediately           | Turns ON after<br>HBx_dead_time |

| 1 → 0          | Turns OFF immediately                                                                               | Turns ON after HBx_dead_time, if NPWM was "0" before DIR switch and did not toggle during dead time | Turns ON after<br>HBx_dead_time | Turns OFF immediately           |

AN5402 - Rev 1 page 3/13

Note:

NPWM sholud be stable before applying the DIR transition, and it should not be switched during the dead-time due to DIR switch. Otherwise, once dead-time for DIR switch event has expired, the dead-time for NPWM transition will start, resulting in twice the dead-time applied.

The dead timers also operate during NPWM switching activity. Transitions are described in the following table.

Table 2. Output response in case of NPWM transition

|                    | DIR = 1                                                                           | DIR = 0                                                 | DIR = 1        |                                                           | DIR = 0        |                                                           |

|--------------------|-----------------------------------------------------------------------------------|---------------------------------------------------------|----------------|-----------------------------------------------------------|----------------|-----------------------------------------------------------|

| NPWM<br>transition | Q1/Q5                                                                             | Q2/Q6                                                   | Q3/Q7          |                                                           | Q4/Q8          |                                                           |

|                    |                                                                                   |                                                         | HBx_AFW<br>= 0 | HBx_AFW = 1                                               | HBx_AFW<br>= 0 | HBx_AFW = 1                                               |

| 0 → 1              | Turns OFF after<br>HBx_dead_time if<br>NPWM is still "1"                          | Turns OFF immediately                                   | Kept OFF       | Turns ON after<br>2*HBx_dead_time if<br>NPWM is still "1" | Kept OFF       | Turns ON after<br>2*HBx_dead_time if<br>NPWM is still "1" |

| 1 → 0              | Turns OFF immediately. Then, it turns ON after HBx_dead_time if NPWM is still "0" | Turns ON after<br>HBx_dead_time if<br>NPWM is still "0" | Kept OFF       | Turns OFF immediately                                     | Kept OFF       | Turns OFF immediately                                     |

Note:

in case NPWM is switched with a very high frequency, which is incompatible with HBx\_dead\_time, the HS will be kept OFF. This happens because every time NPWM toggles  $1 \rightarrow 0$ , the HS output is rset to its default value of "0". However, this condition should be avoided by choosing switching frequency and duty-cycle in order to allow dead-time to expire after both transitions.

AN5402 - Rev 1 page 4/13

### 1.2 DIR switching (normal behavior)

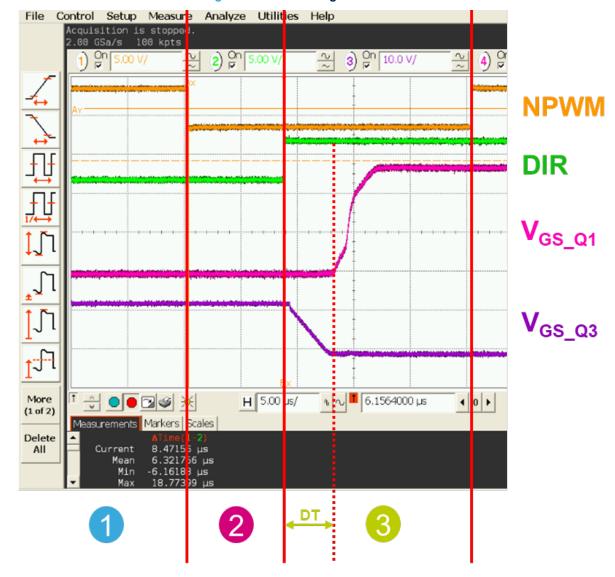

Figure 2. DIR switching: normal behavior

AN5402 - Rev 1 page 5/13

Figure 3. Current paths during H-Bridge direction switching in normal operation

- 1 Active freewheeling on Q4.

- 2 DT upon NPWM transition: passive freewheeling on Q4, then Q2 ON.

- 3 DIR switching. Q2 and Q3 immediatly OFF. Q1 and Q4 ON after DT.

AN5402 - Rev 1 page 6/13

### 1.3 DT management according DIR pin

DT is implemented through a timer having both start and reset control input

- DT START pulse is generated when either NPWM or DIR toggles

- It causes the DT timer to start counting

- DT RESET pulse is generated when either NPWM or DIR toggles, and the counter is still running

- It causes the DT timer value to be reset to the default value, thus overriding any ongoing DT

- DT EXPIRED pulse is generated when counter reaches the programmed DT threshold

- It causes the safe turn ON of the involved FET, avoiding cross-conduction

In case both DT RESET and DT EXPIRED pulses occur simultaneously, the latter has higher priority and a DT EXPIRED condition is considered as valid

Up to 5 clock periods might be necessary to generate either of the two pulses, accounting for synchronization delays

AN5402 - Rev 1 page 7/13

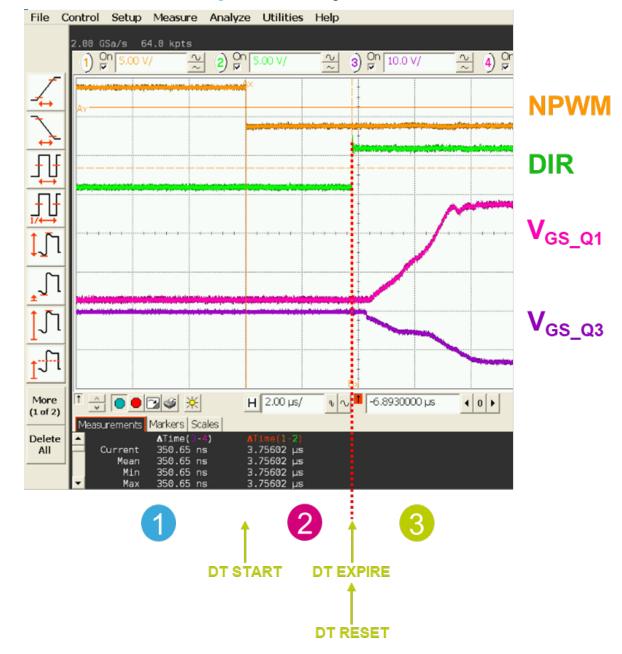

#### 1.4 DIR switching (cross-conduction)

Figure 4. DIR switching: cross conduction

AN5402 - Rev 1 page 8/13

Figure 5. Current paths during H-Bridge direction switching in cross-conduction

- 1 Active freewheeling on Q4.

- 2 DT upon NPWM transition: passive freewheeling on Q4, then Q2 ON.

- 3 DIR switching. Q2 and Q3 immediatly OFF. The DT EXPIRE pulse is aligned to the DT RESET event. This causes the immediate turn ON of Q1, skipping the additional DT.

AN5402 - Rev 1 page 9/13

#### 1.5 Recommended DIR operation in respect to NPWM

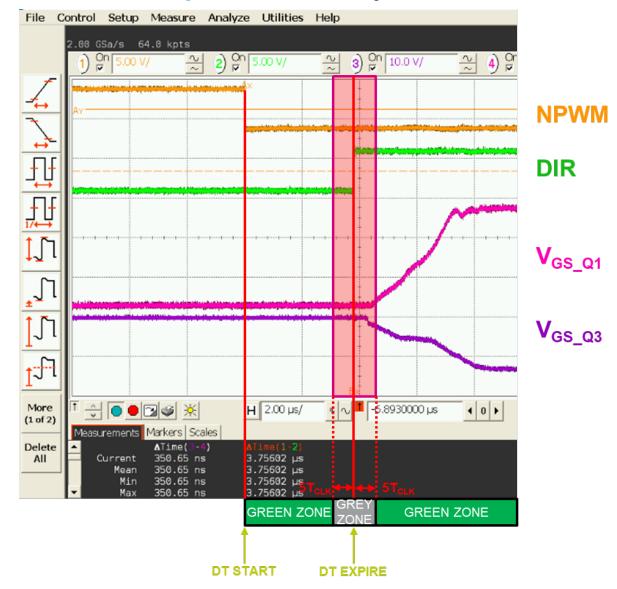

Figure 6. Definition of DIR switching forbidden zone

To avoid inadvertent cross-conduction due to the overlapping of DT EXPIRE and DT RESET pulses, it is recommended to avoid switching the DIR input within the GREY ZONE.

The recommended GREY ZONE window is:

$$t_{GREY} = t_{NPWM\_SWITCH} + HB_{x\_dead\_time} \pm \frac{5}{f_{MAIN\_CLK1}}$$

(1)

#### Where:

- t<sub>NPWM SWITCH</sub> is the time instant where NPWM signal is toggled;

- HB<sub>x\_dead\_time</sub> is the DT configured via SPI;

- f<sub>MAIN\_CLK1</sub> is the main oscillator frequency (10 MHz typ).

To add design robustness, 600 ns grey zone semi-amplitude is recommended.

AN5402 - Rev 1 page 10/13

## **Revision history**

Table 3. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 14-Oct-2019 | 1       | Initial release. |

AN5402 - Rev 1 page 11/13

## **Contents**

| 1   | DIR switching recommendations |                                                  |     |

|-----|-------------------------------|--------------------------------------------------|-----|

|     | 1.1                           | Output behavior following DIR & NPWM transitions | . 2 |

|     | 1.2                           | DIR switching (normal behavior)                  | . 4 |

|     | 1.3                           | DT management according DIR pin                  | . 7 |

|     | 1.4                           | DIR switching (cross-conduction)                 | . 8 |

|     | 1.5                           | Recommended DIR operation in respect to NPWM     | . 9 |

| Rev | rision                        | history                                          | 11  |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, please refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2019 STMicroelectronics - All rights reserved

AN5402 - Rev 1 page 13/13