## RHFL6000 application note

#### Introduction

The characteristics of the voltage transient on the output of a voltage regulator, as a consequence the transfer of energy related to an ion strike with the silicon, is a very critical issue in space applications. Large undershoots can cause erratic operation in memories and microprocessors, while overshoots of excessive amplitude can lead to the degradation - or even the destruction - of CMOS devices. As an example, for most FPGA the recommended operating voltage is 1.5 V and the max. limit 1.6 V (in some applications restricted to 1.575 V to keep further safety margin). This latter applies to both static and dynamic operating conditions.

The RHFL6000 is a low-drop linear regulator designed to be immune to the single events at its output. This feature is achieved through a dedicated internal circuitry embedded for minimizing the transient at the output and the adoption of particular layout rules. However, these steps are not sufficient to achieve the mentioned target. A properly designed PCB and the selection of parts having particular characteristics is essential.

This document provides guidelines about the rules that users should comply with to get output single events < 3.3% of the absolute  $V_{OUT}$  value with the RHFL6000. In particular, these rules refer to:

- · The PCB design

- · The selection of the parts mounted on it

## 1 PCB guidelines

For a voltage regulator, the generation of pulsed currents on the output, either long or short, is among the most salient effects consequent to the single events. These currents can in turn cause voltage spikes whose amplitude is dependent on the amount and nature of the PCB impedance of the paths they flow in. In this respect, the most critical path is the one to ground. According to Section B References the duration of the worst case SET arising into the RHFL6000 is limited to 300 nsec. During this interval, one of the main causes of variation of the output is the ground bouncing caused by the currents spikes (originated by the single event in question) flowing across the ground stray inductance. Therefore, it is essential in designing a PCB to take into account the mentioned effect with a layout aiming at minimizing the parasitic impedance of the connections to GND highlighted in the scheme of fig.1 (LWix, LWox, LWgnd) On the other hand, the inductances on V<sub>OUT</sub>, LW<sub>OUT</sub>, these, according to qualitative simulations, act along with C<sub>OUTX</sub> as a low pass filter for the load and can thus be beneficial.

About the reduction of LWix, LWox, LWgnd, the best recommended practice is the adoption of a ground plane (at least). As it will be discussed in the Appendix, even better results can be achieved by splitting the ground in two separate planes, one for the power connections (POWER GND) and another for the Kelvin sense (SENSE GND). These two planes meet only close to the GND pin of the voltage regulator (that is thus assumed to be the "reference ground" of the system board).

For the second stray inductance considered, according to some qualitative simulations, a LWout of even some tens of nH, along with a suitable Cout, can significantly contribute to the SET mitigation for the load. An LWout of this value can be implemented on board by drawing the PCB track connecting the OUT pins to Cout1, Cout2 and Load properly.

Finally, a third rule concerns the selection of parts: these must be SMD.

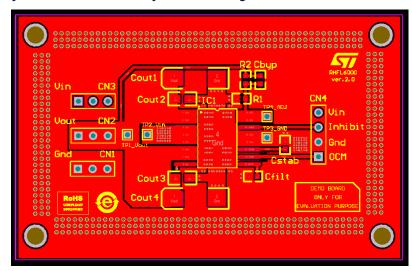

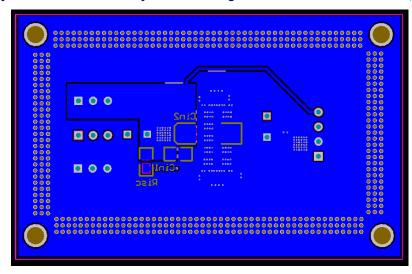

A possible application scheme optimized according to the above indications is shown below. This is the board used by ST for testing the single events. Please notice that the PCB in figures 2/3 doesn't have a power GND as the Power Supply and the Load are supposed to be connected externally through the header connectors (CN1, CN2, CN3).

Not on ST's PCB 1 Vo 16 NC 2 Vo 15 ADJ LOAD < 14 Inhibit - CN4-3 3 Vin R1 4 Vin 13 GND LWgnd LWI Cin2 Cin1 5 Vin 12 GND LWi1 LWi2 Cfilt Cout4 Cout3 7 Vo 10 OCM \_\_\_\_ CN4-1 LWo4 LWo3 8 Isc 9 FiltC Sense/Reference Ground for PCB

Figure 1. Schematic of the board used by ST for the single event tests of the RHFL6000

Board used by ST for the single event tests of the RHFL6000: schematic see figures below, top and bottom view.

AN5175 - Rev 1 page 2/11

Figure 2. Layout of the board used by ST for the single event tests of the RHFL6000, top view

Figure 3. Layout of the board used by ST for the single event tests of the RHFL6000, bottom view

For the specific target of single event < 3.3% absolute  $V_{out}$  variation, additional rules to comply with are:

- 1. connect at each output port a 47 μF tantalum capacitor

- 2. in parallel to each bulk capacitor, connect a 100 nF, low-ESL capacitor for decoupling

- 3. at the output, the 100 nF cap should be mounted close to the load and, for C<sub>in</sub>, close to the voltage regulator

AN5175 - Rev 1 page 3/11

## 2 Guidelines on parts selection

In line with the goal of limiting the stray inductances on GND, an important step concerns the parts selection. In this respect, table 1 shows the suggested BOM list of the components. This was adopted for the buildup of the testing PCB shown in and . In alternative, elements having similar characteristics are also suitable.

Radiospares Ordering information Manufactured **Part** Value - package **Function** Ref CIN1, Multilayer ceramic COUT2, 100 nF - 1206 12065F104K4T2A AVX 698-3695 capacitors - SMD COUT3 COUT1, 47 μF - ESR 35 mΩ -Tantalum Capacitor -T520D476M016ATE035 692-5807 Kemet COUT4 7343-31 SMD  $100 \, \mu F$  - ESR  $35 \, m\Omega$  -Tantalum Capacitor -TPME107K020R0035 CIN2 AVX 548-3494 7343-31 **SMD** Multilayer ceramic **CBYP** 47 nF - 1210 1210J5000473KXT Syfer Technology 774-0597 capacitors - SMD Multilayer ceramic **CFILT** 22 nF - 1206 1206J5000223KXT Syfer Technology 774-0556 capacitors - SMD 8.2 kΩ - 1% - 0603 ERJP03F8201V Resistor - SMD Risc Panasonic 721-7410

Table 1. Suggested BOM

#### Additional guidelines

For a given capacitor, the ESL is made by two components: the first one is intrinsic, whilst the second is dependent on the mount on board (because it is related to the patterns followed on PCB by the single-event currents generated).

Therefore, in order to minimize the SETs, the following additional rules should be adopted:

- The capacitors should have the smallest possible physical size (meaning the highest possible capacitanceto-bulk volume ratio);

- Output capacitors must be physically soldered as close as possible to the output load

- Input capacitor must be located as close as possible to the chip;

#### In addition:

- for each I/O power terminal, it is essential to have a pair of capacitors the first of which for stability and energy storing (bulk cap.), the second for high-frequency signals bypassing;

- Finally note that, compared to a single element, an array of capacitors in parallel at both input/output terminals is expected to work better because the Equivalent Series Inductance is reduced.

For more information about the single event performances of this device, see Section B References.

AN5175 - Rev 1 page 4/11

## A Appendix

### A.1 Guidelines for grounding strategy for an optimum PCB

The generation of pulsed currents, either long or short, is among the most salient effects brought by a single event. In turn, any current exiting from the device can produce voltage spikes, depending on the amount of impedance seen on the pcb path crossed by it.

For this reason, some voltage spikes of considerable amplitude may arise during a single event.

A possible solution to minimize unwanted spikes is to split the ground plane in two: the sense GND and the power GND.

Ideally, the sense GND should be the one "clean" from noise, all low-power terminations should be connected to it. The power GND instead should be used to connect the power source(s).

- To achieve a good GND sensing, it is necessary to comply with the following rules:

- Every node from which critical currents are expected to flow out during a single event (as the GND current originated by SE flowing out from the voltage regulator) should go to the GND reference node directly with the shortest path (also through multiple vias). This minimizes any spurious bouncing on the GND sense plane;

- Vias buildup: in case vias are made of copper, an array of multiple structures works better compared to a single big one because of the resulting lower stray impedance;

- Input/output capacitors: the terminals should be connected to the reference GND;

- BOM: as already mentioned, use of good low-ESR, low-ESL parts.

AN5175 - Rev 1 page 5/11

# **B** References

TRAD: Heavy Ions test report of RHFL6000 from STMicroelectronics, Sept 23, 2014.

AN5175 - Rev 1 page 6/11

# **Revision history**

Table 2. Document revision history

| Date        | Version | Changes          |

|-------------|---------|------------------|

| 27-Aug-2018 | 1       | Initial release. |

AN5175 - Rev 1 page 7/11

# **Contents**

| 1            | PCB                           | guidelines                                           | 2 |  |

|--------------|-------------------------------|------------------------------------------------------|---|--|

| 2            | Guidelines on parts selection |                                                      |   |  |

| A            |                               |                                                      |   |  |

|              | <b>A.1</b>                    | Guidelines for grounding strategy for an optimum PCB | 5 |  |

| B References |                               | erences                                              | 6 |  |

| Rev          | ision                         | history                                              | 7 |  |

# **List of tables**

| Table 1. | Suggested BOM             | ļ |

|----------|---------------------------|---|

| Table 2. | Document revision history | 7 |

AN5175 - Rev 1 page 9/11

# **List of figures**

| Figure 1. | Schematic of the board used by ST for the single event tests of the RHFL6000           | 2 |

|-----------|----------------------------------------------------------------------------------------|---|

| Figure 2. | Layout of the board used by ST for the single event tests of the RHFL6000, top view    | 3 |

| Figure 3. | Layout of the board used by ST for the single event tests of the RHFL6000, bottom view | 3 |

AN5175 - Rev 1 page 10/11

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

AN5175 - Rev 1 page 11/11