## Criteria for configuring L9945 diagnostic parameters in automotive switching applications

## Introduction

The aim of this application note is to provide the criteria for configuring L9945 diagnostic parameters in automotive switching applications. The present analysis can be exploited to obtain a robust fault detection in different scenarios.

Independently of the application, this document aims at providing a set of information, equations and criteria useful to choose the correct values for the diagnostic filter times and currents, thus avoiding false detection and/or failure miss. This paper also covers the advanced diagnostic features implemented on this IC, along with their impact on application robustness. The L9945, an 8-channel configurable HS/LS pre-driver, is considered as the reference device to be used in several applications (P&H, H-Bridge, HS/LS). The ST STD105N10F7AG NMOS and ST STD10PF06T4 PMOS transistors are taken as an example of driver used in power applications.

## 1 Diagnostic summary

## 1.1 How to enable and read diagnostics

Diagnostics can be enabled/disabled by programming the **ENABLE\_DIAGNOSTIC** bit via COMMAND 0, as shown in Figure 1. Diagnostic report for all channels is readable via SPI, after having issued the **0x9AAA0001** frame on MOSI line (SDI). The diagnostic status of each channel is encoded in 3 bits (**diag\_xx[2-0]**), as shown in Table 1.

Table 1. Diagnostic codes

| Channel Status                  | diag_xx[2-0] | Priority |

|---------------------------------|--------------|----------|

| OC pin failure (see note below) | 000          | 1        |

| OC failure                      | 001          | 2        |

| STG/STB failure                 | 10           | 3        |

| OL failure                      | 11           | 4        |

| No failure                      | 100          | 5        |

| No OC failure                   | 101          | 6        |

| No OL/STG/STB failure           | 110          | 7        |

| No diagnostic done              | 111          | 8        |

Note:

The code OC pin failure, corresponding to the code "000" is available only for channels operating in Peak & Hold. This code is unused in other configurations.

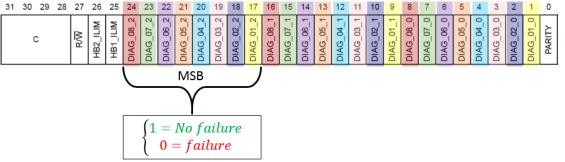

Figure 2 shows how diagnostic codes are partitioned in RESPONSE 9 frame. For an immediate fault detection, the MSB of the diagnostic code can be evaluated. An MSB equal to zero indicates that a failure occurred.

Figure 1. COMMAND 0 frame

| 31 | 30 | 29 | 28 | 27  | 26              | 25                | 24               | 23               | 22               | 21               | 20               | 19               | 18               | 17               | 16              | 15              | 14              | 13              | 12              | 11              | 10              | 9               | 8             | 7             | 6             | 5             | 4             | 3             | 2             | 1             | 0      |

|----|----|----|----|-----|-----------------|-------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|---------------|--------|

|    | ,  | ပ  |    | R/W | SPREAD_SPECTRUM | ENABLE_DIAGNOSTIC | SPI_INPUT_SEL_08 | SPI_INPUT_SEL_07 | SPI_INPUT_SEL_06 | SPI_INPUT_SEL_05 | SPI_INPUT_SEL_04 | SPI_INPUT_SEL_03 | SPI_INPUT_SEL_02 | SPI_INPUT_SEL_01 | PROT_DISABLE_08 | PROT_DISABLE_07 | PROT_DISABLE_06 | PROT_DISABLE_05 | PROT_DISABLE_04 | PROT_DISABLE_03 | PROT_DISABLE_02 | PROT_DISABLE_01 | SPI_ON_OUT_08 | SPI_ON_OUT_07 | SPI_ON_OUT_06 | SPI_ON_OUT_05 | SPI_ON_OUT_04 | SPI_ON_OUT_03 | SPI_ON_OUT_02 | SPI_ON_OUT_01 | PARITY |

GADG1309170948PS

AN5078 - Rev 1 page 2/41

Figure 2. RESPONSE 9 frame

GADG1309170958PS

## 1.2 ON state diagnostics

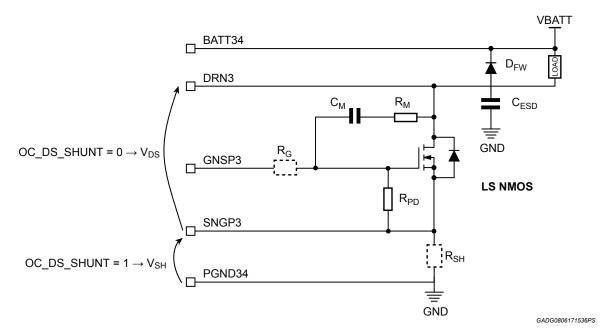

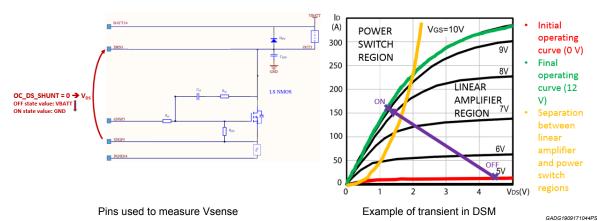

L9945 protects the external FET against overcurrent (OC) during the ON phase. Sensing is performed measuring the voltage drop on an external element and comparing it to the programmed threshold. Refer to Table 4 for OC threshold selection. The external element can be either a shunt resistor or the FET itself: selection can be done by programming the OC\_DS\_SHUNT bit in the COMMANDx frame (x = channel index), as shown in the figure here below.

Figure 3. OC detection method selection (example on a LS NMOS)

The following diagnostic codes can be set while in ON state:

- The diagnostic code corresponding to normal operation is "No OC failure" (101)

- The "No failure" (100) code will be reported only once, after an OFF->ON transition, assuming that "No OL/STG/STB failure" latch was set while in OFF state and "No OC failure" is detected

- The "OC failure" (001) or "OC pin failure" (000) codes will be reported in case of overcurrent detection

Three filter times are involved in ON diagnostics:

t<sub>BLANK\_OC</sub> (programmable via SPI, see Table 2): this timer is started when the output is commanded ON, that is upon NONx 1→0 transition detection. In case t<sub>BLANK\_OC</sub> expires (no OC event stopped the counter), the "No OC failure" code is latched. The value for t<sub>BLANK\_OC</sub> can be selected independently of each channel by programming the T\_BLANK\_OC\_xx[2-0] field in the COMMANDx frame (x = index of the channel).

AN5078 - Rev 1 page 3/41

- t<sub>FIL\_ON</sub> (fixed value, see Table 3): this is a deglitch filter to avoid false OC detection. It suppresses spikes on

the OC comparator output due to the noise when the current is close to the programmed OC threshold. If the

OC comparator output is high for a time interval longer than t<sub>FIL\_ON</sub>, the t<sub>OC</sub> filter timer is started

- t<sub>OC</sub> (fixed value, see Table 3): this is a filter time for OC detection. An OC event (previously deglitched by t<sub>FIL\_ON</sub>) lasting more than t<sub>OC</sub> causes the related output to be immediately switched OFF in order to protect the external FET

## 1.2.1 ON state diagnostics involved parameters

Table 2. No overcurrent filter time: available values

| T_BLANK_OC_xx[2-0] | Min. | Тур.  | Max.  | Unit |

|--------------------|------|-------|-------|------|

| 000                | 10   | 11.1  | 12.2  | μs   |

| 001                | 14   | 15.6  | 17.1  | μs   |

| 010                | 18   | 20    | 22    | μs   |

| 011                | 28   | 31.1  | 34.2  | μs   |

| 100                | 39   | 42.2  | 46.5  | μs   |

| 101                | 48   | 53.3  | 58.7  | μs   |

| 110                | 88   | 97.8  | 107.6 | μs   |

| 111                | 128  | 142.2 | 156.5 | μs   |

Table 3. Fixed filter times for OC detection

| Parameter           | Min. | Max. | Unit |

|---------------------|------|------|------|

| toc                 | 2    | 3    | μs   |

| t <sub>FIL_ON</sub> | 0.6  | 1    | μs   |

Table 4. OC threshold selection

| OC_config_xx[5-0] | Min. | Max. | Min. | Max.  | Unit |

|-------------------|------|------|------|-------|------|

| OO_comig_xx[3-0]  |      | LS   | ŀ    | Offic |      |

| 0                 | 53   | 67   | 53   | 69    | mV   |

| 1                 | 68   | 82   | 68   | 85    | mV   |

| 2                 | 83   | 97   | 83   | 101   | mV   |

| 3                 | 97   | 113  | 99   | 117   | mV   |

| 4                 | 113  | 128  | 113  | 133   | mV   |

| 5                 | 128  | 143  | 129  | 150   | mV   |

| 6                 | 142  | 158  | 144  | 166   | mV   |

| 7                 | 157  | 173  | 159  | 182   | mV   |

| 8                 | 172  | 188  | 172  | 198   | mV   |

| 9                 | 186  | 204  | 189  | 214   | mV   |

| 10                | 201  | 220  | 204  | 231   | mV   |

| 11                | 216  | 235  | 219  | 247   | mV   |

AN5078 - Rev 1 page 4/41

|                   | Min. | Max. | Min. | Max. |      |

|-------------------|------|------|------|------|------|

| OC_config_xx[5-0] |      | LS   |      | HS   | Unit |

| 12                | 231  | 250  | 234  | 263  | mV   |

| 13                | 246  | 266  | 248  | 279  | mV   |

| 14                | 261  | 281  | 264  | 295  | mV   |

| 15                | 275  | 296  | 278  | 311  | mV   |

| 16                | 290  | 311  | 290  | 326  | mV   |

| 17                | 305  | 327  | 305  | 341  | mV   |

| 18                | 320  | 343  | 320  | 356  | mV   |

| 19                | 334  | 358  | 338  | 375  | mV   |

| 20                | 349  | 374  | 351  | 391  | mV   |

| 21                | 364  | 389  | 367  | 407  | mV   |

| 22                | 379  | 405  | 382  | 423  | mV   |

| 23                | 393  | 420  | 397  | 439  | mV   |

| 24                | 408  | 436  | 412  | 455  | mV   |

| 25                | 423  | 451  | 427  | 471  | mV   |

| 26                | 438  | 467  | 442  | 488  | mV   |

| 27                | 453  | 482  | 456  | 504  | mV   |

| 28                | 467  | 498  | 472  | 520  | mV   |

| 29                | 482  | 513  | 486  | 536  | mV   |

| 30                | 497  | 529  | 501  | 552  | mV   |

| 31                | 512  | 544  | 515  | 568  | mV   |

| 32                | 526  | 559  | 525  | 579  | mV   |

| 33                | 541  | 575  | 545  | 595  | mV   |

| 34                | 556  | 590  | 560  | 612  | mV   |

| 35                | 570  | 606  | 575  | 628  | mV   |

| 36                | 585  | 621  | 590  | 644  | mV   |

| 37                | 600  | 637  | 604  | 660  | mV   |

| 38                | 614  | 653  | 619  | 676  | mV   |

| 39                | 629  | 668  | 634  | 693  | mV   |

| 40                | 644  | 684  | 649  | 708  | mV   |

| 41                | 658  | 699  | 663  | 724  | mV   |

| 42                | 673  | 715  | 679  | 740  | mV   |

| 43                | 688  | 730  | 693  | 756  | mV   |

| 44                | 702  | 746  | 708  | 772  | mV   |

| 45                | 717  | 761  | 723  | 788  | mV   |

| 46                | 732  | 777  | 738  | 804  | mV   |

| 47                | 746  | 792  | 753  | 821  | mV   |

| 48                | 761  | 808  | 767  | 836  | mV   |

| 49                | 776  | 823  | 782  | 852  | mV   |

| 50                | 791  | 839  | 797  | 868  | mV   |

AN5078 - Rev 1 page 5/41

| OC config vivis 01 | Min. | Max. | Min. | Max. | I I mid |

|--------------------|------|------|------|------|---------|

| OC_config_xx[5-0]  |      | LS   | ŀ    | ls . | Unit    |

| 51                 | 806  | 854  | 812  | 885  | mV      |

| 52                 | 820  | 870  | 827  | 900  | mV      |

| 53                 | 835  | 885  | 842  | 916  | mV      |

| 54                 | 849  | 900  | 856  | 933  | mV      |

| 55                 | 864  | 916  | 871  | 949  | mV      |

| 56                 | 878  | 931  | 886  | 964  | mV      |

| 57                 | 893  | 947  | 900  | 981  | mV      |

| 58                 | 908  | 962  | 916  | 997  | mV      |

| 59                 | 922  | 977  | 930  | 1013 | mV      |

| 60                 | 937  | 992  | 946  | 1029 | mV      |

| 61                 | 951  | 1008 | 960  | 1045 | mV      |

| 62                 | 967  | 1023 | 975  | 1061 | mV      |

| 63                 | 982  | 1038 | 987  | 1078 | mV      |

Table 5. Gate turn on current I<sub>ON</sub>: constant configuration options

| GCC_config_xx | Nominal | Min. | Max. | Unit |

|---------------|---------|------|------|------|

| NMOS          |         |      |      |      |

| 01            | 20      | 19.6 | 32.4 | mA   |

| 10            | 5       | 4    | 8.6  | mA   |

| 11            | 1       | 1.1  | 1.88 | mA   |

| PMOS          |         |      |      |      |

| 01            | 20      | 16.8 | 27.4 | mA   |

| 10            | 5       | 3.8  | 7.4  | mA   |

| 11            | 1       | 0.75 | 1.9  | mA   |

## 1.3 OFF state diagnostics

L9945 detects open load (OL), short to ground (STG) on LS, and short to battery (STB) on HS during the OFF phase. Refer to Table 6 for the fault detection definition. The following diagnostic codes can be set while in OFF state:

- The diagnostic code corresponding to normal operation is "No OL/STG/STB failure" (110)

- The "No failure" (100) code will be reported only once, after an ON->OFF transition, assuming that "No OC failure" latch was set while in ON state and "No OL/STG/STB failure" is detected

- The "OL failure" (011) or "STG/STB failure" (010) codes will be reported respectively in case of open load and short to ground/battery failures

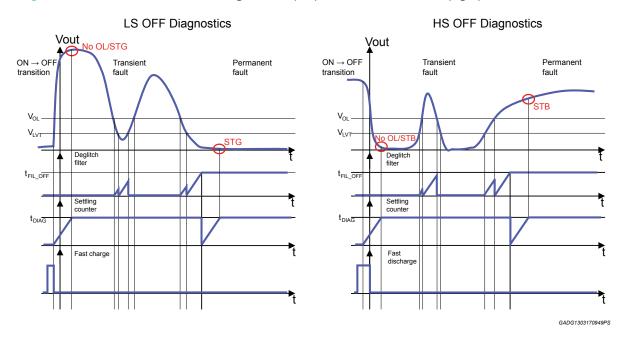

Two filter times are involved in OFF diagnostics (refer to Figure 4):

- t<sub>DIAG</sub> (programmable via SPI, see Table 7): this timer is started when the output is commanded OFF, that is upon NONx → 1 transition detection. When t<sub>DIAG</sub> expires, the voltage Vout on the pin connected to the load is compared to the fault thresholds VOL and VLVT (see Table 8) in order to determine the output status. If no failure is detected, the "No OL/STG/STB failure" code is latched. The value for t<sub>DIAG</sub> can be selected independently on each channel by programming the TDIAG\_CONFIG\_xx[1-0] field in the COMMANDx frame (x = index of the channel)

- t<sub>FIL\_OFF</sub> (fixed value, see Table 8): this is a deglitch filter to avoid false OL/STB/STG detection. It suppresses spikes on the OL/STB/STG comparators outputs due to the noise when V<sub>out</sub> is close to the V<sub>OL</sub>/V<sub>LVT</sub>

AN5078 - Rev 1 page 6/41

thresholds. If a  $V_{LVT}$  or  $V_{OL}$  comparator flags a failure for a time interval longer than  $t_{FIL\_OFF}$ , the  $t_{DIAG}$  timer is reset and restarted.

Figure 4. Filter times for OFF state diagnostics: (left) STG detection on LS; (right) STB detection on HS

Table 6. Fault detection definition for OFF state diagnostics

| FET Side | Condition                           | Diagnostic code                                     |

|----------|-------------------------------------|-----------------------------------------------------|

|          | V <sub>out</sub> < V <sub>LVT</sub> | "No OL/STG/STB failure" (110) or "No failure" (100) |

| HS       | $V_{LVT} < V_{out} < V_{OL}$        | "OL failure" (011)                                  |

|          | V <sub>out</sub> > V <sub>OL</sub>  | "STG/STB failure" (010)                             |

|          | V <sub>out</sub> < V <sub>LVT</sub> | "STG/STB failure" (010)                             |

| LS       | $V_{LVT} < V_{out} < V_{OL}$        | "OL failure" (011)                                  |

|          | V <sub>out</sub> > V <sub>OL</sub>  | "No OL/STG/STB failure" (110) or "No failure" (100) |

Note:

*V*<sub>out</sub> corresponds to DRNx pin for LS NMOS and HS PMOS configurations, while corresponds to SNGPx pin for HS NMOS configuration.

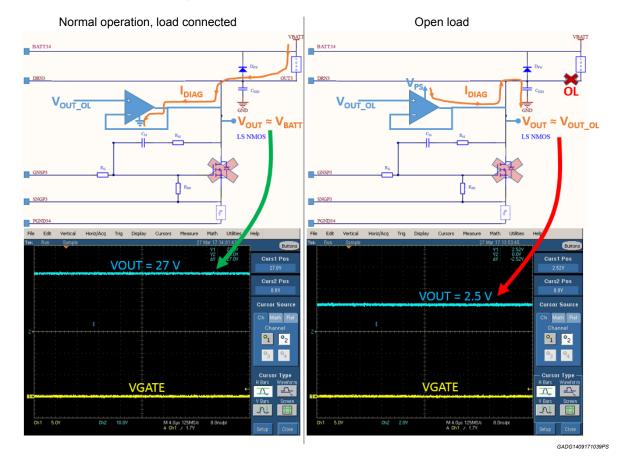

Each channel features an internal regulator with limited current capability that tries regulating the output node voltage  $V_{out}$  around  $V_{OUT\_OL}$ , which falls in the  $[V_{LVT}; V_{OL}]$  range. During normal operation, while in OFF state, the effect of the regulator current on the load is negligible due to its limited value. However, in case of open load failure, Vout will be effectively brought to  $V_{OUT\_OL}$ , thus allowing OL failure detection. Refer to Figure 5 for an example.

Regulator current capability  $I_{DIAG}$  can be programmed via **diag\_i\_config\_xx** bit in the COMMANDx frame (x = channel index), as shown in Table 9.

A higher current capability allows compensating the leakage of external devices (FET, recirculation diodes, etc.) The current limitation feature allows distinguishing between OL and STB/STG faults:

- In case of open load, the regulator is able to drive V<sub>out</sub> around V<sub>OUT\_OL</sub> and the OL fault is flagged

- In case of STB/STG fault, due to the limited current capability, the regulator has no effect on V<sub>out</sub>. Therefore, output node voltage stays below V<sub>LVT</sub> (STG on LS) or above V<sub>OL</sub> (STB on HS)

AN5078 - Rev 1 page 7/41

Figure 5. Example of OL detection on LS NMOS

In order to reliably detect a fault, the V<sub>out</sub> voltage must be stable before the settling time t<sub>DIAG</sub> expires:

- In case of STB/STG faults, high current capability of battery and ground supplies guarantees fast V<sub>out</sub> settling.

- In case of open load, V<sub>out</sub> must be brought in the [V<sub>LVT</sub>; V<sub>OL</sub>] range before t<sub>DIAG</sub> expires in order to guarantee fault detection. L9945 implements internal fast charge/discharge currents in order to allow the settling of V<sub>out</sub> in a time suitable for detection:

- When HS transistor is switched OFF, a fast discharge current I<sub>FAST\_DIS</sub> rapidly decreases V<sub>out</sub> down to V<sub>OL</sub> to help the OL regulator detect an eventual open load fault (see Figure 4). I<sub>FAST\_DIS</sub> is enabled in case:

- The HS channel has been just switched OFF

- The settling time t<sub>DIAG</sub> is still running

- $_{\circ}$  V<sub>out</sub> is below V<sub>LVT</sub>

- When LS transistor is switched OFF, a fast charge current I<sub>FAST\_CHG</sub> rapidly increases V<sub>out</sub> up to V<sub>LVT</sub> to help the OL regulator detect an eventual open load fault (see Figure 4). I<sub>FAST\_DIS</sub> is enabled in case:

- The LS channel has been just switched OFF

- The settling time t<sub>DIAG</sub> is still running

- V<sub>out</sub> is above V<sub>OL</sub>

Value of fast charge/discharge current depends on FET side and type, as shown in Table 11.

AN5078 - Rev 1 page 8/41

## 1.3.1 OFF state diagnostics involved parameters

Table 7. OFF state diagnostic filter time: available values

| TDIAG_CONFIG_xx[1-0]                           | Min.                             | Тур.  | Max.  | Unit |  |  |  |  |  |  |

|------------------------------------------------|----------------------------------|-------|-------|------|--|--|--|--|--|--|

| Available for all configurations               | Available for all configurations |       |       |      |  |  |  |  |  |  |

| 00                                             | 23                               | 25.6  | 28.2  | μs   |  |  |  |  |  |  |

| 01                                             | 55                               | 61.2  | 67.4  | μs   |  |  |  |  |  |  |

| 10                                             | 95                               | 105.6 | 116.2 | μs   |  |  |  |  |  |  |

| 11                                             | 135                              | 150   | 165   | μs   |  |  |  |  |  |  |

| Available only for H-Bridge when HBx_TDIAG_EXT | _CONFIG = 0                      |       |       |      |  |  |  |  |  |  |

| 00                                             | 10                               | 11.2  | 12.4  | μs   |  |  |  |  |  |  |

| 01                                             | 26                               | 28.9  | 31.8  | μs   |  |  |  |  |  |  |

| 10                                             | 36                               | 40    | 44    | μs   |  |  |  |  |  |  |

| 11                                             | 46                               | 51.2  | 56.4  | μs   |  |  |  |  |  |  |

Table 8. Fixed parameters for OFF state diagnostics

| Parameter            | Min. | Max. | Unit |

|----------------------|------|------|------|

| t <sub>FIL_OFF</sub> | 0.3  | 0.5  | μs   |

| V <sub>OL</sub>      | 2.8  | 3.4  | V    |

| V <sub>LVT</sub>     | 1.9  | 2.3  | V    |

Table 9. Vout regulator current capability IDIAG

| diag_i_config_xx | Min. | Max. | Unit |

|------------------|------|------|------|

| 0                | 60   | 100  | μΑ   |

| 1                | 0.6  | 1    | mA   |

Table 10. Vout voltage in case of Open Load failure

| VOUT_OL                                       | Min. | Тур. | Max. | Unit |

|-----------------------------------------------|------|------|------|------|

| V <sub>out</sub> voltage in case of Open Load | 2.25 | 2.5  | 2.75 | V    |

Table 11. Fast charge/discharge current generator electrical characteristics

| Symbol                  | Parameter                                                | Min. | Max. | Unit |

|-------------------------|----------------------------------------------------------|------|------|------|

| I <sub>FAST_CHG</sub>   | V <sub>out</sub> node fast charge current for LS NMOS    | 2.4  | 3.8  | mA   |

| I <sub>FAST_DIS_P</sub> | V <sub>out</sub> node fast discharge current for HS PMOS | 8    | 13   | mA   |

| I <sub>FAST_DIS_N</sub> | V <sub>out</sub> node fast discharge current for HS NMOS | 9    | 15   | mA   |

AN5078 - Rev 1 page 9/41

Table 12. Gate turn off current  $I_{\mbox{OFF}}$ : constant configuration options

| GCC_config_xx | Nominal | Min. | Max. | Unit |

|---------------|---------|------|------|------|

| NMOS          |         |      |      |      |

| 01            | 20      | 16.8 | 27.4 | mA   |

| 10            | 5       | 3.8  | 7.4  | mA   |

| 11            | 1       | 0.75 | 1.9  | mA   |

| PMOS          |         |      |      |      |

| 01            | 20      | 19.6 | 32.4 | mA   |

| 10            | 5       | 4    | 8.6  | mA   |

| 11            | 1       | 0.55 | 1.85 | mA   |

AN5078 - Rev 1 page 10/41

## 2 How to select the right filter time for OFF state diagnostics (t<sub>DIAG</sub>)

Two key aspects must be accounted for a robust fault detection while in OFF state. Considering a PWM signal controlling a generic output channel, the following points must be verified:

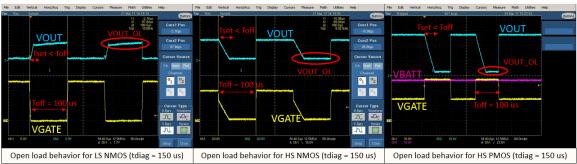

- The t<sub>DIAG</sub> filter must be smaller than the PWM OFF time t<sub>OFF</sub>. In fact, if the channel is switched ON before t<sub>DIAG</sub> has expired, the OFF diagnostics are not performed at all. The diagnostic latches will hold the last value determined from ON state diagnostics. Refer to Figure 6 as an example of missed OL failure. In the example, the output node is stable at V<sub>OUT\_OL</sub> before t<sub>OFF</sub> expires. Hence, OL fault could be correctly detected if a proper t<sub>DIAG</sub> had been selected. However, since t<sub>DIAG</sub> > t<sub>OFF</sub> had been intentionally programmed, the diagnostic code reported for the channel under analysis was "No OC failure" (101), that is the last valid diagnostic code referred to the ON state.

- As a consequence, a corner value for PWM t<sub>OFF</sub> is represented by the smallest programmable t<sub>DIAG</sub>, corresponding to 23 μs (consider a 20% additional margin for a robust behavior). A control signal with a t<sub>OFF</sub> below this threshold may be correctly processed by L9945, but OFF diagnostics are not guaranteed and the external microcontroller must take care of catching eventual OL/STG/STB faults.

- The t<sub>DIAG</sub> filter must be higher than the V<sub>out</sub> settling time t<sub>SET\_OFF</sub>. If this constraint is not verified, wrong diagnostics will be reported. Referring to Figure 6, if the constraint related to settling time is not fulfilled, the sampled V<sub>out</sub> might be lower than V<sub>LVT</sub> in case of LS NMOS, leading to a false STG detection. In case of HS NMOS/PMOS, programming a t<sub>DIAG</sub> < t<sub>SET\_OFF</sub> means sampling a V<sub>out</sub> greater than V<sub>OL</sub>, leading to a false STB detection.

- As a consequence, t<sub>SET\_OFF</sub> evaluation represents a critical aspect for a correct t<sub>DIAG</sub> selection. The t<sub>SET\_OFF</sub> is strongly dependent on the failure type and the chosen external components.

- In case of STG/STB failures, transition on the V<sub>out</sub> is almost immediate, due to the high current capability of the battery and ground supplies. Hence, failure will be detected independently on the chosen t<sub>DIAG</sub> value (provided that t<sub>DIAG</sub> < t<sub>OFF</sub>).

- In case of OL, t<sub>SET\_OFF</sub> depends on many application related parameters, thus representing the real boundary for the t<sub>DIAG</sub> range evaluation.

- As shown in Figure 6, settling time is significantly lower for LS NMOS configuration, due to the smaller voltage swing of the output node.

- For a LS NMOS, in case of open load, V<sub>out</sub> must be charged from GND to V<sub>OUT\_OL</sub>, thus implying a small output transition.

- For a HS NMOS/PMOS, in case of open load, V<sub>out</sub> must be discharged from V<sub>BATT</sub> down to V<sub>OUT\_OL</sub>, thus implying a much wider output transition. This explains why the fast discharge currents are considerably higher than the fast charge one, as shown in Table 11.

The next figure shows an example of missed OL failure when the programmed  $t_{DIAG}$  is greater than the PWM  $t_{OFF}$ : OL on LS NMOS configuration (left); OL on HS NMOS configuration (center); OL on HS PMOS configuration (right).

Figure 6. Example of missed OL failure

GADG2209171318PS

AN5078 - Rev 1 page 11/41

Summarizing the first part of our analysis, the criterion to ensure robust OFF state diagnostics is described by the following equation:

#### Eq: General criterion for choosing the correct filter time for OFF state diagnostics

$$t_{SET\ OFFmax} < t_{DIAGmin} < t_{OFFmin}$$

(1)

#### Where:

- t<sub>OFFmin</sub> depends on the PWM control signal and its minimum value must be considered

- t<sub>SET\_OFFmax</sub> is the output settling time in case of open load failure (worst case for settling time) and its maximum value must be considered

- t<sub>DIAGmin</sub> is the OFF state diagnostic filter whose minimum corner is still greater than the worst output settling time (see Table 7)

Because  $t_{OFF}$  is a PWM related parameter, it is supposed to vary along with the duty-cycle. Hence, a key point in order to allow smaller values for  $t_{OFF}$  without compromising diagnostics is to minimize the output settling time  $t_{SET}$  OFF. In fact, the smaller the  $t_{SET}$  OFF, the lower the  $t_{DIAG}$  and the wider the  $t_{OFF}$  range, as stated by Eq. (1).

## 2.1 Evaluation of the output settling time (t<sub>SET\_OFF</sub>)

As discussed in Section 2 How to select the right filter time for OFF state diagnostics (tDIAG), the output settling time evaluation plays a key role in the  $t_{DIAG}$  selection. It is also clear that  $t_{SET\_OFF}$  evaluation strongly depends on FET side. Before elaborating the analysis more in detail for each case, a common criterion for settling time estimation can be summarized by the following equation:

Eq: Output settling time estimation for ON to OFF transition: general criterion

$$\begin{cases} t_{SET\_OFF} = t_{FET\_OFF} + t_{CHARGE} & for LS \\ t_{SET\_OFF} = t_{FET\_OFF} + t_{DISCHARGE} & for HS \end{cases}$$

(2)

In Eq. (2), contributions are the following:

- t<sub>FET\_OFF</sub> is the time needed to turn OFF the external FET. In fact, there is a delay between the NONx 0 to 1 transition and the time instant t<sub>FET\_OFF</sub> when the transistor can be considered OFF. Voltage on the output node will be stable to the ON state value until the external FET is turned OFF. Such a delay is due to several contributions:

- Internal Digital paths: asynchronous digital input synchronization stages and propagation through the disable paths

- Internal Analog paths: switching time of the output current generators in the pre-driver stage

- External paths: switching time of the external FET used as power driver

The sum of internal digital and analog paths represents a negligible aliquot of the final  $t_{FET\_OFF}$ , due to the high clock frequency (10 MHz typical) and the small capacitance of the internal analog nodes (in the fF/pF order of magnitude). Hence,  $t_{FET\_OFF}$  can be reasonably approximated with the external path delay, whose entity depends on several application related parameters that will be analyzed in detail case by case.

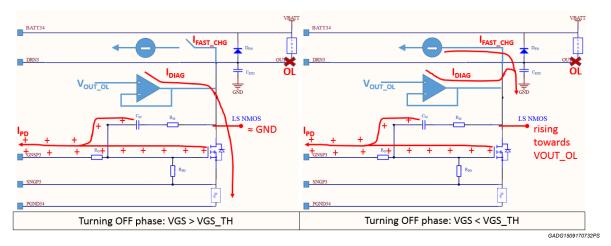

- t<sub>CHARGE</sub> is the time needed in a LS configuration to charge the output node from GND up to VOUT\_OL. This

time depends on the following parameters:

- Fast charge current I<sub>FAST\_CHG</sub> (refer to Table 11): this current generator works in parallel to the OL regulator diagnostic current I<sub>DIAG</sub> and it is considerably higher in respect to the latter in order to allow fast V<sub>out</sub> settling time. Such a generator is activated once the external FET reaches the ON threshold voltage V<sub>GS\_TH</sub> and it's turned OFF when V<sub>out</sub> reaches the [V<sub>LVT</sub>; V<sub>OL</sub>] range.

- OL regulator diagnostic current I<sub>DIAG</sub> (refer to Table 9): the OL regulator is enabled upon digital input NONx 0 to 1 transition and stays ON for the whole PWM OFF time (t<sub>OFF</sub>)

- Output node capacitance C<sub>OUT</sub>: usually an ESD capacitor is mounted on the DRNx output pin in order to prevent L9945 and FET damage due to injected charge spikes. Such a component limits the output transition speed

Note: The actual bound for OL detection is represented by the lower bound of the  $[V_{LVT}; V_{OL}]$  range. However, a more conservative approach is recommended and therefore  $V_{OUT-OL}$  is considered when evaluating the output swing.

AN5078 - Rev 1 page 12/41

- t<sub>DISCHARGE</sub> is the time needed in a HS configuration to discharge the output node from VBATT down to V<sub>OUT</sub> OL. This time depends on the following parameters:

- Fast discharge current I<sub>FAST\_DIS\_N</sub>/I<sub>FAST\_DIS\_P</sub> (refer to Table 11): this current generator works in parallel to the OL regulator diagnostic current I<sub>DIAG</sub> and it is considerably higher in respect to the latter in order to allow fast Vout settling time. Such a generator is activated once the external FET reaches the ON threshold voltage V<sub>GS\_TH</sub> and it's turned OFF when Vout reaches the [V<sub>LVT</sub>; V<sub>OL</sub>] range.

- OL regulator diagnostic current I<sub>DIAG</sub> (refer to Table 9): the OL regulator is enabled upon digital input NONx 0 to 1 transition and stays ON for the whole PWM OFF time (t<sub>OFF</sub>)

- Output node capacitance C<sub>OUT</sub>: usually an ESD capacitor is mounted on the SNGPx/DRNx output pin in order to prevent L9945 and FET damage due to injected charge spikes. Such a component limits the output transition speed

Note: The actual bound for OL detection is represented by the upper bound of the  $[V_{LVT}; V_{OL}]$  range. However, a more conservative approach is recommended and therefore  $V_{OUT-OL}$  is considered when evaluating the output swing.

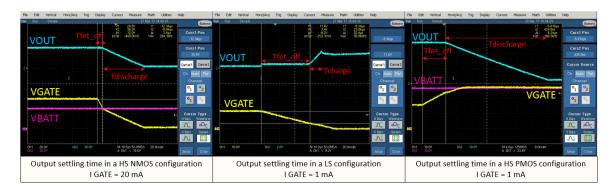

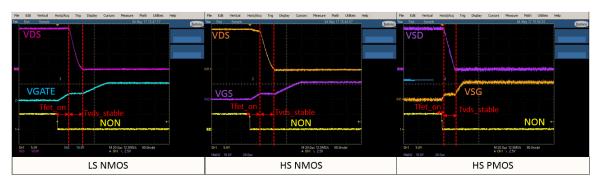

The figure below can be considered as a graphical reference for  $t_{\text{FET\_OFF}}$ ,  $t_{\text{CHARGE}}$  and  $t_{\text{DISCHARGE}}$  individuation during the output transient.

Figure 7. Graphic example of  $t_{\text{FET\_OFF}}$ ,  $t_{\text{CHARGE}}$  and  $t_{\text{DISCHARGE}}$

In general, LS configuration allows much faster settling times in respect to the HS one. This is due to the reduced output swing for the former configuration. In the example shown in Figure 7, a LS configuration with a gate discharge current equal to 1 mA features almost the same settling time of a HS configuration with a gate discharge current programmed to 20 mA. More details about settling time evaluation will be provided in the following paragraphs.

#### 2.1.1 Output settling time for a LS NMOS configuration

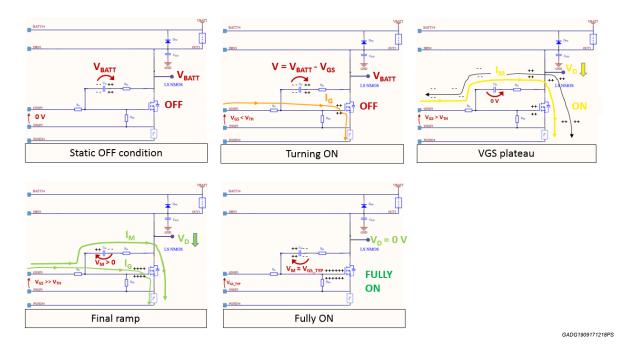

The turn OFF phase of a LS NMOS can be divided into two sub-intervals, as shown in Figure 7 and Figure 8:

#### First sub-interval

In the initial phase, both Miller and  $C_{GS}$  capacitors are discharged through a constant current  $I_{OFF}$ . While  $V_{GS}$  is greater than the ON threshold  $V_{GS\_TH}$ , the drain voltage is almost equal to GND, because the transistor is still turned ON, and the IDIAG won't charge the ESD capacitor on the output. During such an interval, the  $t_{FET\_OFF}$  mentioned in Eq. (2) can be evaluated considering that  $C_M$  and  $C_{GS}$  are in parallel.

## Eq: t<sub>FET OFF</sub> estimation for a LS NMOS configuration

$$I_{OFF} = (C_{GS} + C_M) \frac{\Delta V_{GS}}{\Delta t} \Rightarrow t_{FET\_OFF} = (C_{GS} + C_M) \frac{V_{GS\_ON} - V_{GS\_TH}}{I_{OFF}}$$

(3)

Where:

$I_{\text{OFF}}$  is the programmed constant gate discharge current, that can be chosen among the values listed in Table 12 (only constant current options are considered);

$V_{GS\_ON}$  is the ON gate-to-source voltage, whose range is [10 - 14] V for L9945;

AN5078 - Rev 1 page 13/41

V<sub>GS TH</sub> is the external FET ON threshold voltage, whose range is [2.5 - 4.5] V for STD105N10F7AG.

#### Second sub-interval

Once  $t_{\text{FET\_OFF}}$  has expired, the transistor is turned OFF and  $I_{\text{FAST\_CHG}}$  is activated. Hence, the output node is charged with a total current equal to the sum of  $I_{\text{DIAG}}$  and  $I_{\text{FAST\_CHG}}$ . Charging phase lasts until  $V_{\text{out}}$  reaches  $V_{\text{OUT\_OL}}$ . The  $t_{\text{CHARGE}}$  mentioned in Eq. (2) can be evaluated considering the linear charge of the output ESD capacitor.

Eq: Estimation of  $t_{CHARGE}$  in a LS NMOS configuration.

$$I_{DIAG} + I_{FAST\_CHG} = C_{ESD} \frac{\Delta V_{out}}{\Delta t} \Rightarrow t_{CHARGE} = C_{ESD} \frac{V_{OUT\_OL}}{I_{DIAG} + I_{FAST\_CHG}}$$

(4)

Where:

I<sub>DIAG</sub> is the programmed OL regulator current capability (refer to Table 9);

I<sub>FAST CHG</sub> is the fast charge current (refer to Table 11);

$V_{OUT\ OL}$  is the target voltage for the OL regulator, whose range is [2.25 – 2.75] V for L9945;

C<sub>ESD</sub> is the external ESD capacitor mounted on the DRNx pin.

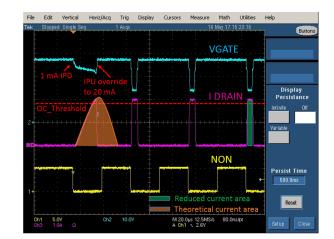

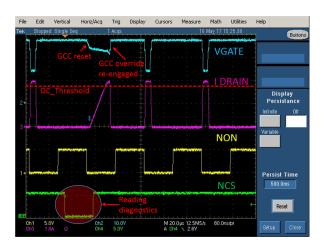

Figure 8. LS turn OFF transition

Figure 9. LS output settling time when different gate discharge currents are programmed

GADG1509170746PS

The above figure shows how output settling time varies according to the programmed gate discharge current. Actually, the  $I_{OFF}$  acts only on  $t_{FET\_OFF}$ , while  $t_{CHARGE}$  depends on  $I_{DIAG}$  and  $I_{FAST\_CHG}$ . Hence,  $t_{SET\_OFF}$  is extremely variable among different applications/settings. The final criterion to evaluate the output settling time is described by the following equation:

AN5078 - Rev 1 page 14/41

Eq: Final formula for  $t_{\mbox{\footnotesize SET\_OFF}}$  estimation in a LS NMOS configuration.

$$t_{SET} = \left(C_{GS} + C_{M}\right) \frac{V_{GS\_ON} - V_{GS\_TH}}{I_{OFF}} + C_{ESD} \frac{V_{OUT\_OL}}{I_{DIAG} + I_{FAST\_CHG}} \tag{5}$$

Because  $t_{SET\_OFF}$  represents the lower bound in Eq. (1), then its maximum corner must be considered in order to operate a robust choice for  $t_{DIAG}$ .

Eq: Corner case for the output settling time estimation in a LS NMOS configuration.

$$t_{SET\_OFF_{max}} = (C_{GS_{max}} + C_{Mmax}) \frac{V_{GS\_ON_{max}} - V_{GS\_TH_{min}}}{I_{OFF_{min}}}$$

$$+ C_{ESD_{max}} \frac{V_{OUT\_OL_{max}}}{I_{DIAG_{min}} + I_{FAST\_CHG_{min}}}$$

$$(6)$$

Eventually,  $t_{SET\_OFF\_MAX}$  might be multiplied by a tolerance margin (1 + TM%) in order to be even more conservative. However, it is not recommend since it might represent an unrealistic constraint. It makes sense using the TM% when evaluating settling time using Eq. (5) and assuming typical values for all involved parameters.

Having evaluated  $t_{SET\_OFF\_MAX}$ , Eq. (1) states that the safest choice for  $t_{DIAG}$  is the nominal value from Table 7, whose minimum corner is still greater than  $t_{SET\_OFF\_MAX}$ .

Since a very conservative approach has been used when estimating  $t_{SET\_OFF\_MAX}$ , borderline cases where  $t_{SET\_OFF\_MAX}$  is greater than  $t_{DIAG\_min}$  by a really small amount, might still lead to choose the lower bound for  $t_{DIAG\_min}$ . In fact, referring to Eq. (6), nine uncorrelated parameters assuming their worst case value is definitely unlikely to occur.

Differently from HS configuration, choosing different values for OL regulator current capability  $I_{DIAG}$  can lead to significant variations of  $t_{SET\_OFF\_MAX}$ . In fact, in Eq. (6)  $I_{DIAG\_MIN}$  must be compared to  $I_{FAST\_CHG\_MIN}$  whose value is only 2.4 mA, due to the reduced output swing. Hence, switching  $I_{DIAG\_MIN}$  from 60  $\mu$ A to 600  $\mu$ A through diag\_i\_config\_xx bit might have a visible impact on  $t_{SET\_OFF\_MAX}$ .

Regarding  $I_{OFF\_MIN}$ , switching between 1 mA, 5 mA and 20 mA options through the **GCC\_CONFIG\_xx** bit will have a huge impact on  $t_{SET\_MAX}$ .

All these elaborations can be verified using the Section 7 L9945 Diagnostic Filter Times calculator.

#### 2.1.2 Output settling time for a HS NMOS configuration

The L9945 IC uses an internal charge pump to efficiently bias HS NMOS transistors and to obtain the same VGS as in LS configuration.

The turn OFF phase of a HS NMOS can be divided into two sub-intervals, as shown in Figure 7 and Figure 10:

#### First sub-interval

In the initial phase, both Miller and  $C_{GS}$  capacitors are discharged through a constant current  $I_{OFF}$ . While  $V_{GS}$  is greater than the ON threshold  $V_{GS\_TH}$ , the source voltage is almost equal to VBATT, because the transistor is still turned ON, and the  $I_{DIAG}$  won't discharge the ESD capacitor on the output. During such an interval, the  $t_{FET\_OFF}$  mentioned in Eq. (2) can be evaluated considering that  $C_{M}$  and  $C_{GS}$  are in parallel.

Eq: t<sub>FET\_OFF</sub> estimation for a HS NMOS configuration.

$$I_{OFF} = \left(C_{GS} + C_M\right) \frac{\Delta V_{GS}}{\Delta t} \Rightarrow t_{FET\_OFF} = \left(C_{GS} + C_M\right) \frac{V_{GS\_ON} - V_{GS\_TH}}{I_{OFF}} \tag{7}$$

Where:

I<sub>OFF</sub> is the programmed constant gate discharge current, that can be chosen among the values listed in Table 12 (only constant current options are considered);

V<sub>GS ON</sub> is the ON gate-to-source voltage, whose range is [10 - 14] V for L9945;

V<sub>GS TH</sub> is the external FET ON threshold voltage, whose range is [2.5 - 4.5] V for STD105N10F7AG.

#### Second sub-interval

Once  $t_{FET\_OFF}$  has expired, the transistor is turned OFF and  $t_{FAST\_DIS\_N}$  is activated. Hence, the output node is discharged with a total current equal to the sum of  $t_{DIAG}$  and  $t_{FAST\_DIS\_N}$ . Discharging phase lasts until  $t_{Out}$

AN5078 - Rev 1 page 15/41

reaches  $V_{OUT\_OL}$ . The  $t_{DISCHARGE}$  mentioned in Eq. (2) can be evaluated considering the linear discharge of the output ESD capacitor.

Eq: Estimation of  $t_{\mbox{\scriptsize DISCHARGE}}$  in a HS NMOS configuration.

$$I_{DIAG} + I_{FAST\_DIS\_N} = C_{ESD} \frac{\Delta V_{out}}{\Delta t} \Rightarrow t_{DISCHARGE} = C_{ESD} \frac{V_{BATT} - V_{OUT\_OL}}{I_{DIAG} + I_{FAST\_DIS\_N}} \tag{8}$$

Where:

$I_{DIAG}$  is the programmed OL regulator current capability (refer to Table 9);

$I_{FAST\_DIS\_N}$  is the fast discharge current for HS NMOS configuration (refer to Table 11);

V<sub>OUT</sub> OL is the target voltage for the OL regulator, whose range is [2.25 – 2.75] V for L9945;

C<sub>ESD</sub> is the external ESD capacitor mounted on the SNGPx pin;

Turning OFF phase: VGS > VGS\_TH

V<sub>BATT</sub> is the battery supply voltage.

Figure 10. HS NMOS turn OFF transition

GADG1509171308PS

Turning OFF phase: VGS < VGS\_TH

GADG1809171508PS

The above figure shows how output settling time varies according to the programmed gate discharge current. Actually, the I<sub>OFF</sub> acts only on t<sub>FET\_OFF</sub>, while t<sub>DISCHARGE</sub> depends on I<sub>DIAG</sub> and I<sub>FAST\_DIS\_N</sub>. Hence, t<sub>SET\_OFF</sub> is extremely variable among different applications/settings. The final criterion to evaluate the output settling time is described by the following equation:

Eq: Final formula for tSET\_OFF estimation in a HS NMOS configuration.

$$t_{SET\_OFF} = \left(C_{GS} + C_M\right) \frac{V_{GS\_ON} - V_{GS\_TH}}{I_{OFF}} + C_{ESD} \frac{V_{BATT} - V_{OUT\_OL}}{I_{DIAG} + I_{FAST\_DIS\_N}} \tag{9}$$

AN5078 - Rev 1 page 16/41

Because  $t_{SET\_OFF}$  represents the lower bound in Eq. (1), then its maximum corner must be considered in order to operate a robust choice for  $t_{DIAG}$ .

Eq: Corner case for the output settling time estimation in a HS NMOS configuration.

$$t_{SET\_OFFmax} = (C_{GSmax} + C_{Mmax}) \frac{V_{GS\_ON_{max}} - V_{GS\_TH_{min}}}{I_{OFFmin}} + C_{ESD_{max}} \frac{V_{BATT} - V_{OUT\_OL_{min}}}{I_{DIAGmin} + I_{FAST\_DIS\_N_{min}}}$$

$$(10)$$

Eventually,  $t_{SET\_OFF\_MAX}$  might be multiplied by a tolerance margin (1 + TM%) in order to be even more conservative. However, ST doesn't recommend it since it might represent an unrealistic constraint. It makes sense using the TM% when evaluating settling time using Eq. (9) and assuming typical values for all involved parameters.

It is worth noticing how the settling time in a HS configuration depends on the battery supply voltage. Hence, there is a huge difference between CV and PV applications: in the former, settling times are much higher due to the fact that VBATT is twice the one in the latter.

Having evaluated  $t_{SET\_OFF\_MAX}$ , Eq. (1) states that the safest choice for  $t_{DIAG}$  is the nominal value from Table 7, whose minimum corner is still greater than  $t_{SET\_OFF\_MAX}$ .

Since a very conservative approach has been used when estimating  $t_{SET\_OFF\_MAX}$ , borderline cases where  $t_{SET\_OFF\_MAX}$  is greater than  $t_{DIAG\_min}$  by a really small amount, might still lead to choose the lower bound for  $t_{DIAG\_min}$ . In fact, referring to Eq. (10), nine uncorrelated parameters assuming their worst case value is definitely unlikely to occur.

Differently from LS configuration, choosing different values for OL regulator current capability  $I_{DIAG}$  doesn't lead to significant variations of  $t_{SET\_OFF\_MAX}$ . In fact, in Eq. (10)  $I_{DIAG\_MIN}$  must be compared to  $I_{FAST\_DIS\_N\_MIN}$  whose value is much higher (9 mA), due to the wider output swing. Hence, switching  $I_{DIAG\_MIN}$  from 60  $\mu$ A to 600  $\mu$ A through **diag\_i\_config\_xx** bit might not have a visible impact on  $t_{SET\_OFF\_MAX}$ .

Regarding  $I_{OFF\_MIN}$ , switching between 1 mA, 5 mA and 20 mA options through the **GCC\_CONFIG\_xx** bit will have a huge impact on  $t_{SET\_OFF\_MAX}$ .

All these elaborations can be verified using the Section 7 L9945 Diagnostic Filter Times calculator.

## 2.1.3 Output settling time for a HS PMOS configuration

The turn OFF phase of a HS PMOS can be divided into two sub-intervals, as shown in Figure 7 and Figure 12:

#### First sub-interval

In the initial phase, both Miller and CGS capacitors are charged through a constant current  $I_{PU}$ . While  $V_{SG}$  is greater than the ON threshold  $V_{SG\_TH}$ , the drain voltage is almost equal to VBATT, because the transistor is still turned ON, and the  $I_{DIAG}$  won't discharge the ESD capacitor on the output. During such an interval, the  $t_{FET\_OFF}$  mentioned in Eq. (2) can be evaluated considering that CM and CGS are in parallel.

Eq: t<sub>FET\_OFF</sub> estimation for a HS PMOS configuration.

$$I_{OFF} = (C_{GS} + C_M) \frac{\Delta V_{SG}}{\Delta t} \quad \Rightarrow \quad t_{FET\_OFF} = (C_{GS} + C_M) \frac{V_{SG\_ON} - V_{SG\_TH}}{I_{OFF}}$$

$$\tag{11}$$

Where:

$I_{OFF}$  is the programmed constant gate charge current, that can be chosen among the values listed in Table 12 (only constant current options are considered);

V<sub>SG ON</sub> is the ON source-to-gate voltage, whose range is [10 - 14] V for L9945;

V<sub>SG TH</sub> is the external FET ON threshold voltage, whose range is [2 - 4] V for STD10PF06T4.

#### Second sub-interval

Once  $t_{\text{FET\_OFF}}$  has expired, the transistor is turned OFF and  $t_{\text{FAST\_DIS\_P}}$  is activated. Hence, the output node is discharged with a total current equal to the sum of  $t_{\text{DIAG}}$  and  $t_{\text{FAST\_DIS\_P}}$ . Discharging phase lasts until  $t_{\text{Out}}$  reaches  $t_{\text{OUT\_OL}}$ . The  $t_{\text{DISCHARGE}}$  mentioned in Eq. (2) can be evaluated considering the linear discharge of the output ESD capacitor.

AN5078 - Rev 1 page 17/41

Eq: Estimation of  $t_{\mbox{\scriptsize DISCHARGE}}$  in a HS PMOS configuration.

$$I_{DIAG} + I_{FAST\_DIS\_P} = C_{ESD} \frac{\Delta V_{out}}{\Delta t} \quad \Rightarrow \quad t_{DISCHARGE} = C_{ESD} \frac{V_{BATT} - V_{OUT\_OL}}{I_{DIAG} + I_{FAST\_DIS\_P}} \tag{12}$$

Where:

I<sub>DIAG</sub> is the programmed OL regulator current capability (refer to Table 9);

I<sub>FAST DIS P</sub> is the fast discharge current (refer to Table 11);

V<sub>OUT</sub> OL is the target voltage for the OL regulator, whose range is [2.25 – 2.75] V for L9945;

C<sub>ESD</sub> is the external ESD capacitor mounted on the DRNx pin.

BATTS6

BATTS6

CRATT HS PMOS

CRATT

Figure 12. HS PMOS turn OFF transition

GADG1909170740P

Figure 13. HS PMOS output settling time when different gate charge currents are programmed

image13.png

The above figure shows how output settling time varies according to the programmed gate charge current. Actually, the  $I_{OFF}$  acts only on  $t_{FET\_OFF}$ , while  $t_{DISCHARGE}$  depends on  $I_{DIAG}$  and  $I_{FAST\_DIS\_P}$ . Hence,  $t_{SET\_OFF}$  is extremely variable among different applications/settings. The final criterion to evaluate the output settling time is described by the following equation:

Eq: Final formula for  $t_{\mbox{\footnotesize SET}}$  estimation in a HS PMOS configuration.

$$t_{SET\_OFF} = \left(C_{GS} + C_M\right) \frac{V_{SG\_ON} - V_{SG\_TH}}{I_{OFF}} + C_{ESD} \frac{V_{BATT} - V_{OUT\_OL}}{I_{DIAG} + I_{FAST\_DIS\_P}} \tag{13}$$

Because  $t_{SET\_OFF}$  represents the lower bound in Eq. (1), then its maximum corner must be considered in order to operate a robust choice for  $t_{DIAG}$ .

AN5078 - Rev 1 page 18/41

Eq: Corner case for the output settling time estimation in a HS PMOS configuration.

$$t_{SET\_OFF_{max}} = \left(C_{GS_{max}} + C_{M_{max}}\right) \frac{V_{SG\_ON_{max}} - V_{SG\_TH_{min}}}{I_{OFF_{min}}} \\ + C_{ESD_{max}} \frac{V_{BATT} - V_{OUT\_OL_{min}}}{I_{DIAG_{min}} + I_{FAST\_DIS\_P_{min}}}$$

$$(14)$$

Eventually, t<sub>SET\_OFF\_MAX</sub> might be multiplied by a tolerance margin (1 + TM%) in order to be even more conservative. However, ST doesn't recommend it since it might represent an unrealistic constraint. It makes sense using the TM% when evaluating settling time using Eq. (13) and assuming typical values for all involved parameters.

It is worth noticing how the settling time in a HS configuration depends on the battery supply voltage. Hence, there is a huge difference between CV and PV applications: in the former, settling times are much higher due to the fact that VBATT is twice the one in the latter.

Having evaluated  $t_{SET\_OFF\_MAX}$ , Eq. (1) states that the safest choice for  $t_{DIAG}$  is the nominal value from Table 7, whose minimum corner is still greater than  $t_{SET\_OFF\_MAX}$ .

Since a very conservative approach has been used when estimating  $t_{SET\_OFF\_MAX}$ , borderline cases where  $t_{SET\_OFF\_MAX}$  is greater than  $t_{DIAG\_}$ min by a really small amount, might still lead to choose the lower bound for  $t_{DIAG\_}$ min. In fact, referring to Eq. (14), nine uncorrelated parameters assuming their worst case value is definitely unlikely to occur.

Differently from LS configuration, choosing different values for OL regulator current capability  $I_{DIAG}$  doesn't lead to significant variations of  $t_{SET\_OFF\_MAX}$ . In fact, in Eq. (14)  $I_{DIAG\_MIN}$  must be compared to  $I_{FAST\_DIS\_P\_MIN}$  whose value is much higher (8 mA), due to the wider output swing. Hence, switching  $I_{DIAG\_MIN}$  from 60  $\mu$ A to 600  $\mu$ A through **diag\_i\_config\_xx** bit might not have a visible impact on  $t_{SET\_OFF\_MAX}$ .

Regarding  $I_{OFF\_MIN}$ , switching between 1 mA, 5 mA and 20 mA options through the **GCC\_CONFIG\_xx** bit will have a huge impact on  $I_{SET\_OFF\_MAX}$ .

All these elaborations can be verified using the Section 7 L9945 Diagnostic Filter Times calculator.

AN5078 - Rev 1 page 19/41

# How to select the right filter time for ON state diagnostics (t<sub>BLANK OC</sub>)

Two key aspects must be accounted for a robust fault detection while in ON state. Considering a PWM signal controlling a generic output channel, the following points must be verified:

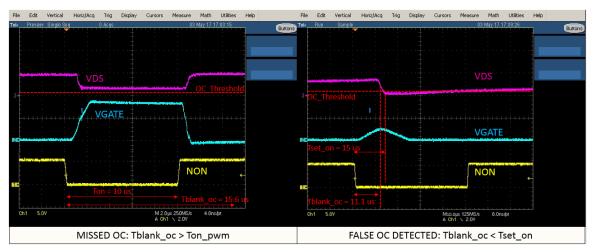

- The t<sub>BLANK\_OC</sub> filter must be smaller than the PWM ON time t<sub>ON</sub>. In fact, if channel is switched OFF before t<sub>BLANK\_OC</sub> has expired, the ON diagnostics are not performed at all. The diagnostic latches will hold the last value determined from OFF state diagnostics. Refer to Figure 16 as an example of missed OC failure. In the example, DSM is used as OC detection method. The external FET VDS is consistently above the OC threshold during the ON time, but the output is switched OFF before t<sub>BLANK\_OC</sub> expires. As a consequence, "No OL/STG/STB" (110) is reported instead of the expected "OC failure" (001). The diagnostic code reported refers in fact to the last valid entry latched during OFF state.

- As a consequence, a corner value for PWM  $t_{ON}$  is represented by the smallest programmable  $t_{BLANK\_OC}$ , corresponding to 11  $\mu$ s (consider a 20% additional margin for a robust behavior). A control signal with a  $t_{ON}$  below this threshold may be correctly processed by L9945, but ON diagnostics are not guaranteed and the external microcontroller must take care of catching eventual OC faults

- The t<sub>BLANK\_OC</sub> filter must be higher than the V<sub>sense</sub> settling time t<sub>SET\_ON</sub>. If this constraint is not verified, wrong diagnostics will be reported. V<sub>sense</sub> depends on the OC detection strategy chosen by programming the OC\_DS\_SHUNT\_xx bit. A huge difference occurs between DSM and Rshunt methods (refer to Figure 14 and Figure 15. OC sensing using DSM method):

- In case R<sub>shunt</sub> method is selected, the Vsense behavior during the OFF to ON transition corresponds to an ascending transient. Hence, in case output current crosses the OC threshold with a positive slope, an actual OC event is really likely to be ongoing. In this case, t<sub>BLANK\_OC</sub> is almost meaningless from a diagnostics point of view. The OC detection will be mainly based on t<sub>FIL\_ON</sub> and t<sub>OC</sub> parameters (see Table 3). The former is a deglitch filter to avoid small overshoots on the shunt resistor due to inductive effects, while the latter represents the actual OC blanking time. Summarizing, an OC event lasting t<sub>FIL\_ON</sub>+t<sub>OC</sub> will be detected and the output switched OFF: the programmed t<sub>BLANK\_OC</sub> will have no effect on the OC reaction time, but it only causes the assertion of the "No OC failure" latch once it expires. Only in case Peak & Hold configuration is selected and the OC event occurs while t<sub>BLANK\_OC</sub> is still running, an "OC pin failure" (000) will be reported instead of simple "OC failure" (001). However, reaction time won't be affected.

BATTS4

| Discolar | Find | Discolar | Part | Discolar | Discolar

Figure 14. OC sensing using Rshunt method

Pins used to measure Vsense

Example of transient

CADC1000170052PS

In case DSM method is selected, the V<sub>sense</sub> behavior during the OFF to ON transition corresponds to a descending transient, whose slope depends on the programmed gate charge/discharge current (GCC\_CONFIG\_xx). Hence, in case t<sub>BLANK\_OC</sub> is smaller than the Vsense settling time, a false OC detection will occur. Referring to Figure 16, the sampled VDS is still higher than the OC threshold when t<sub>BLANK\_OC</sub> expires, resulting in a wrong OC detection that causes the output to be immediately shut OFF. In order to ensure maximum FET protection against critical OC events during blanking time, an OC threshold crossing with a positive slope will stop the t<sub>BLANK\_OC</sub> and engage the t<sub>OC</sub> filter.

AN5078 - Rev 1 page 20/41

Figure 15. OC sensing using DSM method

As a consequence, t<sub>SET\_ON</sub> evaluation represents a critical aspect for a correct t<sub>BLANK\_OC</sub> selection. The t<sub>SET\_ON</sub> is strongly dependent on the programmed gate charge current and the chosen external components.

Figure 16. Example of wrong ON state diagnostics

GADG1909171055PS

#### The figure above shows:

- left side: the programmed t<sub>BLANK</sub> ON is greater than the PWM t<sub>ON</sub>, resulting in a missed OC detection;

- right side: the programmed t<sub>BLANK\_ON</sub> is smaller than the output settling time, resulting in a false OC detection.

Summarizing the first part of our analysis, the criterion to ensure robust ON state diagnostics is described by the following equation:

### Eq: General criterion for choosing the correct filter time for ON state diagnostics

$t_{SET\_ONmax} < t_{BLANK\_OCmin} < t_{ONmin}$ (15)

### Where:

- t<sub>ONmin</sub> depends on the PWM control signal and its minimum value must be considered

- t<sub>SET\_ONmax</sub> is the output settling time in case DSM method is selected for OC detection (worst case for settling time) and its maximum value must be considered

- t<sub>BLANK\_OCmin</sub> is the ON state diagnostic filter whose minimum corner is still greater than the worst output settling time (see Table 2)

AN5078 - Rev 1 page 21/41

Because  $t_{ON}$  is a PWM related parameter, it is supposed to vary along with the duty-cycle. Hence, a key point in order to allow smaller values for  $t_{ON}$  without compromising diagnostics is to minimize the output settling time  $t_{SET\_ON}$ . In fact, the smaller the  $t_{SET\_ON}$ , the lower the  $t_{BLANK\_OC}$  and the wider the  $t_{ON}$  range, as stated by Eq. (15).

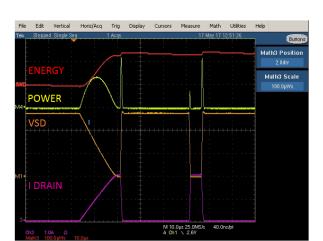

## 3.1 Evaluation of the output settling time $(t_{SET ON})$

As discussed in Section 3 How to select the right filter time for ON state diagnostics (tBLANK\_OC), the output settling time evaluation plays a key role in the  $t_{BLANK\_OC}$  selection when DSM is used. Unlike the ON to OFF transition, where the  $t_{SET\_OFF}$  varies according to FET side and type, the OFF to ON transition features the same VDS transient in all three different configurations, as shown in Figure 17. A common criterion for settling time estimation can be summarized by the following equation:

#### Eq: Output settling time estimation for OFF to ON transition: general criterion

$$t_{SET\_ON} = t_{FET\_ON} + t_{VDS\_STABLE}$$

(16)

In Eq. (16), contributions are the following:

- t<sub>FET\_ON</sub> is the time needed to turn ON the external FET. In fact, there is a delay between the NONx 1 to 0 transition and the time instant t<sub>FET\_ON</sub> when the transistor can be considered ON. The FET VDS will be stable to the OFF state value until the external FET is turned ON. Such a delay is due to several contributions:

- Internal Digital paths: asynchronous digital input synchronization stages and propagation through the disable paths

- Internal Analog paths: switching time of the output current generators in the pre-driver stage

- External paths: switching time of the external FET used as power driver

The sum of internal digital and analog paths represents a negligible aliquot of the final  $t_{FET\_ON}$ , due to the high clock frequency (10 MHz typical) and the small capacitance of the internal analog nodes (in the fF/pF order of magnitude). Hence,  $t_{FET\_ON}$  can be reasonably approximated with the external path delay, whose entity depends on the following parameters:

- Programmed gate charge current

- External FET gate capacitance

- t<sub>VDS\_STABLE</sub> is the time needed for the VDS to switch from the OFF state value (usually VBATT) to the final

value, which is usually very close to 0 V, since the external POWER MOS features a very low on-resistance.

This time depends on the following parameters:

- Programmed gate charge current

- Miller capacitance (usually only the external discrete component is considered, while the FET internal C<sub>GD</sub> is neglected because much smaller)

The figure below can be considered as a graphical reference for t<sub>FET\_ON</sub>, and t<sub>VDS\_STABLE</sub> individuation during the output transient. Observing the plots, it is evident that the external FET can be considered ON when the VGS plateau begins. The VDS will then be discharged.

Figure 17. VDS transients during the OFF to ON switch

GADG1909171148PS

AN5078 - Rev 1 page 22/41

#### 3.1.1 Output settling time for all configurations

Figure 18 and Figure 19 describe in detail the OFF to ON transition. They can be used to understand how the  $t_{\text{FET ON}}$  and  $t_{\text{VDS STABLE}}$  time intervals can be estimated.

File Edit Vertical Horiz/Acq Trig Display Cursors Measure Math Utilities Help

Tel: Run Sample

27 Feb 17 16/36/49

Buttons

N1 0 pp 250MSA 4 0 mosts

N1 0 pp 250MSA 4 0 mosts

Figure 18. VGS transient during transistor OFF to ON switching

GADG1909171154PS

Figure 19. Step by step description of the OFF to ON transition

The turn ON phase of an NMOS can be divided into two sub-intervals:

In the initial phase, the C<sub>GS</sub> capacitor is charged through a constant current I<sub>ON</sub>. While V<sub>GS</sub> is lower than the ON threshold V<sub>GS\_TH</sub>, the drain voltage is still constant and equal to VBATT (OFF state value), because the transistor is still OFF. During such an interval, the t<sub>FET\_ON</sub> mentioned in Eq. (16) can be evaluated considering the linear charge of the C<sub>GS</sub>:

Eq: t<sub>FET\_ON</sub> estimation for an NMOS configuration

$$I_{ON} = C_{GS} \frac{\Delta V_{GS}}{\Delta t} \quad \Rightarrow \quad t_{FET\_ON} = C_{GS} \frac{V_{GS\_TH}}{I_{ON}} \tag{17}$$

AN5078 - Rev 1 page 23/41

#### Where:

- I<sub>ON</sub> is the programmed constant gate charge current, that can be chosen among the values listed in Table 5 (only constant current options are considered)

- V<sub>GS TH</sub> is the external FET ON threshold voltage, whose range is [2.5 4.5] V for STD105N10F7AG

- Once t<sub>FET\_ON</sub> has expired, the transistor is turned ON and the VGS plateau occurs. During such a phase, the charge current flows only through the external Miller capacitance CM mounted between drain and gate. The VDS undergoes a linear discharge with a constant current equal to I<sub>ON</sub>. At the end of the transient, VDS will be close to 0 V, due to the very small on-resistance of the POWER MOS. The t<sub>VDS\_STABLE</sub> mentioned in Eq. (16) can be evaluated as follows:

Eq: Estimation of t<sub>VDS</sub> <sub>STABLE</sub> in an NMOS configuration.

$$\begin{cases} \frac{dV_{DS}}{dt} \Big|_{V_{GS}plateau} = \frac{d(V_{GS} + V_{DG})}{dt} \Big|_{V_{GS}plateau} = \frac{dV_{DG}}{dt} \\ I_{ON} = C_M \frac{\Delta V_{DS}}{\Delta t} \implies t_{VDS\_STABLE} = C_M \frac{V_{BATT}}{I_{ON}} \end{cases}$$

(18)

#### Where:

- I<sub>ON</sub> is the programmed constant gate charge current, that can be chosen among the values listed in Table 5 (only constant current options are considered)

- V<sub>BATT</sub> is the battery supply voltage

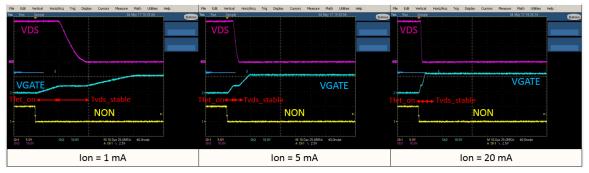

Figure 20. Output settling time when different gate charge currents are programmed

GADG2009170823PS

The above figure shows how output settling time varies according to the programmed gate discharge current. The  $I_{ON}$  acts on both  $t_{FET\_ON}$ , and  $t_{VDS\_STABLE}$ . Hence,  $t_{SET\_ON}$  is extremely variable among different applications/ settings. The final criterion to evaluate the output settling time is described by the following equation:

Eq: Final formula for t<sub>SET ON</sub> estimation:

$$t_{SET\_ON} = \frac{1}{I_{ON}} \left( C_{GS} V_{GS\_TH} + C_M V_{BATT} \right) \tag{19}$$

Because  $t_{SET\_ON}$  represents the lower bound in Eq. (15), then its maximum corner must be considered in order to operate a robust choice for  $t_{BLANK\_OC}$ .

Eq: Corner case for the output settling time estimation

$$t_{SET\_ONmax} = \frac{1}{I_{ONmin}} \left( C_{GSmax} V_{GS\_THmax} + C_{Mmax} V_{BATTmax} \right) \tag{20}$$

Note: All the calculations made for NMOS are also valid in case of PMOS, provided that  $V_{SD}$  and  $V_{SG}$  are considered. Eventually,  $t_{SET\_ON\_MAX}$  might be multiplied by a tolerance margin (1 + TM%) in order to be even more conservative. However, ST doesn't recommend it since it might represent an unrealistic constraint. It makes

Eventually, t<sub>SET\_ON\_MAX</sub> might be multiplied by a tolerance margin (1 + TM%) in order to be even more conservative. However, ST doesn't recommend it since it might represent an unrealistic constraint. It makes sense using the TM% when evaluating settling time using Eq. (19) and assuming typical values for all involved parameters.

AN5078 - Rev 1 page 24/41

Having evaluated  $t_{SET\_ON\_MAX}$ , Eq. (15) states that the safest choice for  $t_{BLANK\_OC}$  is the nominal value from Table 2, whose minimum corner is still greater than  $t_{SET\_ON\_MAX}$ .

Since a very conservative approach has been used when estimating  $t_{SET\_ON\_MAX}$ , borderline cases where  $t_{SET\_ON\_MAX}$  is greater than  $t_{BLANK\_OC\_min}$  by a really small amount, might still lead to choose the lower bound for  $t_{BLANK\_OC\_min}$ . In fact, referring to Eq. (20), five uncorrelated parameters assuming their worst case value is definitely unlikely to occur.

It is worth noticing how the settling time depends on the battery supply voltage. Hence, there is a huge difference between CV and PV applications: in the former, settling times are much higher due to the fact that VBATT is twice the one in the latter.

Regarding ION\_MIN, switching between 1 mA, 5 mA and 20 mA options through the  $GCC\_CONFIG\_xx$  bit will have a huge impact on  $t_{SET\_ON\_MAX}$ .

All these elaborations can be verified using the Section 7 L9945 Diagnostic Filter Times calculator.

AN5078 - Rev 1 page 25/41

## 4 Understanding Open Load Detection

As discussed in OFF state diagnostics, each output channel features an independent voltage regulator with a limited current capability  $I_{DIAG}$ , programmable via SPI bit **DIAG\_I\_CONFIG\_XX**. Such a regulator is active during the channel OFF state and performs OL detection, which occurs when the output node  $V_{out}$  is regulated around  $V_{OUT\ OL}$ .

## 4.1 Tracking thresholds

Both OL and STG/STB detections are based on the output voltage V<sub>out</sub> sensing. In particular, Table 6 defines the conditions that lead to fault detection while in OFF state. In order to avoid thresholds overlapping each other, causing wrong diagnostics (OL detected instead of STG/STB and vice versa), a tracking design technique has been adopted.

The table below shows a comparison between the fault thresholds ( $V_{OL}$  and  $V_{LVT}$ ) and the open load regulator output target. The former has been designed in tracking, so that they both spread in the same direction according to the process tolerance. In other words, when  $V_{OL}$  shows its maximum corner,  $V_{LVT}$  is also equal to its upper bound (and vice versa).

Parameter Min. Max. Unit VOL 2.8 3.4 V VOUT\_OL 2.25 2.75 ٧ **VI VT** 19 23 V

Table 13. Comparison between fault thresholds and Open Load regulator output target

The V<sub>OUT</sub> OL is designed according to the following formula:

Eq:

$$t_{SET\_ON} = \frac{1}{I_{ON}} \left( C_{GS} V_{GS\_TH} + C_M V_{BATT} \right) \tag{21}$$

Hence, the fact that  $V_{OL}$  and  $V_{LVT}$  follow each other guarantees  $V_{OUT\_OL}$  being always positioned in the middle of the [ $V_{OL}$ ;  $V_{LVT}$ ] range. For instance, the case where  $V_{LVT}$  = 2.3 V and  $V_{OUT\_OL}$  = 2.25 V is impossible.

## 4.2 Minimum Load Resistance (R<sub>L OPEN</sub>) for Open Load Detection

In order for a load to be considered "Open", its resistance must be higher than a threshold value  $R_{L\_OPEN}$ . Such a value depends on FET side and selected OL regulator current capability  $I_{DIAG}$ . The latter has been designed in order to guarantee a good trade-off between having fast output settling time (see Section 2 How to select the right filter time for OFF state diagnostics (tDIAG)) and keeping an acceptable  $V_{out}$  ripple in case of open load.

Moreover, an  $I_{DIAG}$  too high may alter the load behavior causing unwanted actuations while in the OFF state. Refer to Table 9 for the available  $I_{DIAG}$  values.

The open load detection occurs when  $V_{out}$  is in the  $[V_{LVT}; V_{OL}]$  range. Detailed description of the fault conditions is available in Table 6.

### 4.2.1 R<sub>L OPEN</sub> evaluation for HS configuration

In a High-Side configuration,  $I_{DIAG}$  flows through the load following the path described in the figure below. Apart from a small leakage aliquot due to external components, it can be stated that  $I_{DIAG} \approx I_{LOAD}$ . In case this is not verified, the stronger  $I_{DIAG}$  must be programmed to compensate for  $I_{LEAK}$ .

AN5078 - Rev 1 page 26/41

VOUT\_OL

VREG

DRN1

HS NMOS

CM

RM

CBATT

CBATT

CBATT

CBATT

CAND

COUTING

CAND

CA

Figure 21. Open Load diagnostic current flowing through the RLOAD in HS configuration

GADG2009171303PS

The Vout in steady state can be calculated according to the following equation.

Eq

$$V_{out} = R_{LOAD} * I_{DIAG}$$

(22)

Referring to Table 6, the turning point between OL and No OL is represented by the condition Vout = VLVT:

Eq

$$V_{out} = V_{LVT} \implies R_{L\_OPEN} = \frac{V_{LVT}}{I_{DIAG}}$$

(23)

Values of load resistance smaller than  $R_{L\_OPEN}$  will cause No OL detection, because the OL regulator current capability is not sufficient to bring the output voltage above the  $V_{LVT}$  threshold by increasing the drop on RL. On the other hand, values of load resistance greater than  $R_{L\_OPEN}$  will cause OL detection, because the OL regulator is able to control the current in the [0 ; IDIAG] range in order to force  $V_{out} = V_{OUT\_OL}$ .

Taking in account the process spread (refer to Table 8 and Table 9), the following corners can be evaluated for  $R_{L\_OPEN}$ :

Eq:

$$\begin{cases} R_{L\_OPENmin} = \frac{V_{LVTmin}}{I_{DIAGmax}} \\ R_{L\_OPENmax} = \frac{V_{LVTmax}}{I_{DIAGmin}} \end{cases} \tag{24} \label{eq:24}$$

Corners will change according to the programmed OL regulator current capability IDIAG. They're summarized in the following table:

Table 14. Minimum load resistance for open load detection RL\_OPEN: corner cases

| Parameter               | Weak I <sub>DIAG</sub> (100 μA) | Strong I <sub>DIAG</sub> (1 mA) | Unit |

|-------------------------|---------------------------------|---------------------------------|------|

| R <sub>L_OPEN_MIN</sub> | 19                              | 1.9                             | kΩ   |

| R <sub>L_OPEN_MAX</sub> | 38.3                            | 3.83                            | kΩ   |

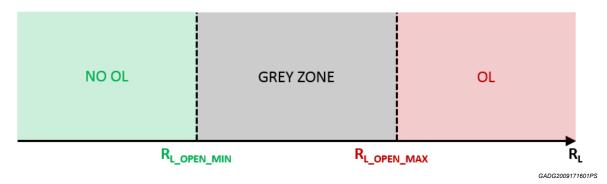

Concluding the analysis for the HS configuration:

AN5078 - Rev 1 page 27/41

- Values of R<sub>LOAD</sub> < R<sub>L OPEN MIN</sub> will never flag OL

- Values of R<sub>LOAD</sub> > R<sub>L\_OPEN\_MAX</sub> will certainly flag OL

The  $[R_{L\_OPEN\_MIN}; R_{L\_OPEN\_MAX}]$  represents a grey zone for OL detection due to process spread

Note: The analysis applies to both NMOS and PMOS FET types.

Figure 22. Summarizing critical values of load resistance for OL detection in HS configuration

## 4.2.2 R<sub>L OPEN</sub> evaluation for LS configuration

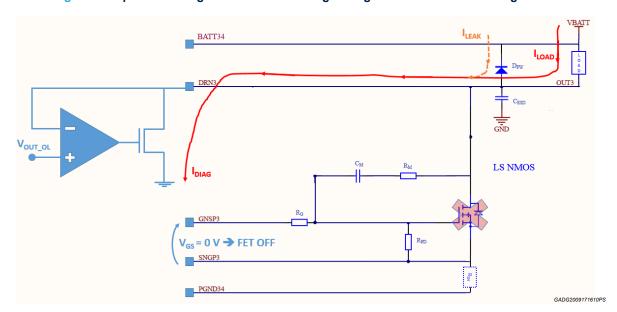

In a Low-Side configuration,  $I_{DIAG}$  flows through the load following the path described in the figure below. Apart from a small leakage aliquot due to external components, it can be stated that  $I_{DIAG} \approx I_{LOAD}$ . In case this is not verified, the stronger  $I_{DIAG}$  must be programmed to compensate for  $I_{LEAK}$ .

Figure 23. Open Load diagnostic current flowing through the RLOAD in LS configuration

The  $V_{\text{out}}$  in steady state can be calculated according to the following equation.

$V_{out} = V_{BATT} - R_{LOAD} * I_{DIAG}$  (25)

Referring to Table 6, the turning point between OL and No OL is represented by the condition V<sub>out</sub> = V<sub>OL</sub>.

Eq:

Eq:

$$V_{out} = V_{OL} \Rightarrow R_{L\_OPEN} = \frac{V_{BATT} - V_{OL}}{I_{DIAG}}$$

(26)

AN5078 - Rev 1 page 28/41

Values of load resistance smaller than  $R_{L\_OPEN}$  will cause No OL detection, because the OL regulator current capability is not sufficient to bring the output voltage below the VOL threshold by increasing the drop on RL. On the other hand, values of load resistance greater than  $R_{L\_OPEN}$  will cause OL detection, because the OL regulator is able to control the current in the [0;  $I_{DIAG}$ ] range in order to force  $V_{out} = V_{OUT\_OL}$ .

Taking in account the process spread (refer to Table 8 and Table 9), the following corners can be evaluated for  $R_{L\ OPEN}$ .

Eq:

$$\begin{cases} R_{L\_OPENmin} = \frac{V_{BATT} - V_{OLmax}}{I_{DIAGmax}} \\ R_{L\_OPENmax} = \frac{V_{BATT} - V_{OLmin}}{I_{DIAGmin}} \end{cases}$$

(27)

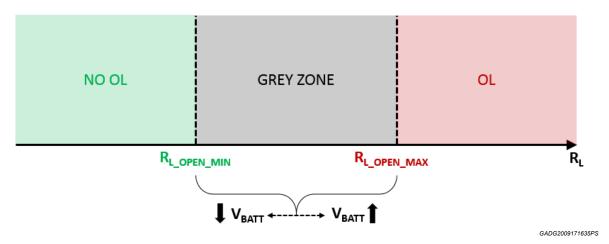

Differently from the HS configuration, the LS case introduces the dependency on the supply voltage. Corners will change according to the programmed OL regulator current capability  $I_{DIAG}$  and the  $V_{BATT}$ . Because  $V_{BATT}$  is not constant in a real scenario, the  $[R_{L\_OPEN\_MIN}; R_{L\_OPEN\_MAX}]$  is a dynamic range. Values for the most common applications are summarized in the following table:

Table 15. Minimum load resistance for open load detection RL\_OPEN: corner cases

| Supply Voltage [V]  | Parameter               | Weak IDIAG (100 μA) | Strong IDIAG (1 mA) | Unit |

|---------------------|-------------------------|---------------------|---------------------|------|

| Cranking (6.V)      | R <sub>L_OPEN_MIN</sub> | 26                  | 2.6                 | kΩ   |

| Cranking (6 V)      | R <sub>L_OPEN_MAX</sub> | 53.3                | 5.3                 | kΩ   |

| DV naminal (12.1/)  | R <sub>L_OPEN_MIN</sub> | 86                  | 8.6                 | kΩ   |

| PV nominal (12 V)   | R <sub>L_OPEN_MAX</sub> | 153.3               | 15.3                | kΩ   |

| DV typical (14 V)   | R <sub>L_OPEN_MIN</sub> | 106                 | 10.6                | kΩ   |

| PV typical (14 V)   | R <sub>L_OPEN_MAX</sub> | 186.7               | 18.7                | kΩ   |

| D) / may (40 ) /)   | R <sub>L_OPEN_MIN</sub> | 146                 | 14.6                | kΩ   |

| PV max (18 V)       | R <sub>L_OPEN_MAX</sub> | 253.3               | 25.3                | kΩ   |

| CV naminal (24.)()  | R <sub>L_OPEN_MIN</sub> | 206                 | 20.6                | kΩ   |

| CV nominal (24 V)   | R <sub>L_OPEN_MAX</sub> | 353.3               | 35.3                | kΩ   |

| CV to united (20 V) | R <sub>L_OPEN_MIN</sub> | 246                 | 24.6                | kΩ   |

| CV typical (28 V)   | R <sub>L_OPEN_MAX</sub> | 420                 | 42                  | kΩ   |

| C) / may (20 ) /)   | R <sub>L_OPEN_MIN</sub> | 326                 | 32.6                | kΩ   |

| CV max (36 V)       | R <sub>L_OPEN_MAX</sub> | 553.3               | 55.3                | kΩ   |

| Load Dump (F9.)/)   | R <sub>L_OPEN_MIN</sub> | 546                 | 54.6                | kΩ   |

| Load Dump (58 V)    | R <sub>L_OPEN_MAX</sub> | 920                 | 92                  | kΩ   |

Concluding the analysis for the LS configuration:

- Values of R<sub>LOAD</sub> < R<sub>L OPEN MIN</sub> will never flag OL

- Values of R<sub>LOAD</sub> > R<sub>L\_OPEN\_MAX</sub> will certainly flag OL

- The [R<sub>L\_OPEN\_MIN</sub>; R<sub>L\_OPEN\_MAX</sub>] represents a grey zone for OL detection due to process spread.

Moreover, such a range is dynamic and depends on the operating supply voltage

AN5078 - Rev 1 page 29/41

Figure 24. Summarizing critical values of load resistance for OL detection in LS configuration

AN5078 - Rev 1 page 30/41

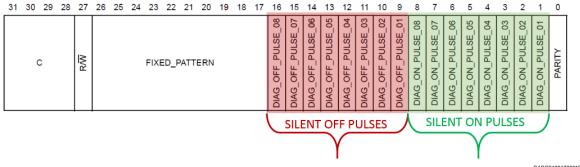

## 5 Diagnostic pulses

Diagnostic pulses are intended to be used for static loads, that is, external FETs that are permanently ON or OFF. Because diagnostics depend on the output state, L9945 offers the possibility to temporarily switch the channel in order to perform diagnostic tests without disturbing the normal operation of the load. Diagnostic pulses can also be used when the PWM frequency and duty cycle don't allow to perform valid ON/OFF diagnostics. The microcontroller may decide to interrupt the switching activity once in a while with a diagnostic pulse in order to perform diagnostics. Both ON and OFF silent pulses can be sent through **COMMAND 9**.

Figure 25. Silent diagnostic pulses can be executed independently on each channel by sending COMMAND 9

GADG2109170801P

In case both <code>DIAG\_OFF\_PULSE\_xx</code> and <code>DIAG\_ON\_PULSE\_xx</code> are set in the same command frame, the output reaction depends on current state:

- If the channel was being kept OFF, an ON pulse will be executed

- If the channel was being kept ON, an OFF pulse will be executed

Diagnostic pulses are not available for H-Bridge configuration. The IC will ignore any pulse request.

#### 5.1 ON Pulses

ON pulses are meant to perform a "try and catch" operation on a channel that is being permanently kept OFF or turned ON for a very short time interval, not sufficient to perform ON state diagnostics. They can be used to temporarily switch ON the channel and verify that no overcurrent event occurs. Diagnostic FSM will always follow the priority codes listed in Table 1:

- In case "No OL/STG/STB failure" (110) was latched during OFF state, the channel will be turned ON and:

- In case no overcurrent occurs, the "No failure" (100) code will be reported

- In case of OC, the "OC failure" (001) code will be reported

- In case a failure was latched during OFF state (e.g. "OL failure" (011))

- In case no overcurrent occurs, the failure code latched during the OFF state will be reported because it still has higher priority

- In case of OC, the "OC failure" (001) code will overwrite the previous fault code because the new failure has higher priority

Note: In order to be sure of reading the actual ON state failure code, reset the FSM by reading the diagnostics through COMMAND 9 before executing the ON pulse.

The ON pulse duration is fixed and falls in the [80-120]  $\mu$ s range. It has been designed according to the trade-off between leaving the load operation unaltered and meeting the VDS settling time in case of DSM (as discussed in Section 3 How to select the right filter time for ON state diagnostics (tBLANK\_OC)). When DSM is selected as OC detection strategy, overcurrent diagnostics are performed only if the blanking time is smaller than the ON pulse duration. Therefore, ON pulses will be effective only if used on channels whose blanking time has been set to tall the condition is not met, the diagnostic code reported will be the one latched during OFF state.

AN5078 - Rev 1 page 31/41

Note:

OC events can be predicted while in OFF state by seeking for STB/STG failure. In case of such failures, switching the output ON will most likely result in an OC event.

#### 5.2 OFF Pulses

OFF pulses are meant to perform a "try and catch" operation on a channel that is being permanently kept ON or turned OFF for a very short time interval, not sufficient to perform OFF state diagnostics. They can be used to temporarily switch OFF the channel and verify that no OL/STG/STB event occurs. Diagnostic FSM will always follow the priority codes listed in Table 1:

- In case "No OC failure" (101) was latched during ON state, the channel will be turned OFF and:

- In case no OL/STG/STB occurs, the "No failure" (100) code will be reported

- In case of OL/STG/STB, the corresponding fault code will be reported (e.g. "OL failure" (011))

- In case "OC failure" (011) was latched during ON state, its fault code will still be reported, independently of the OFF state diagnostics. This happens because OC events have a higher priority.

Note:

In order to be sure of reading the actual OFF state failure code, reset the FSM by reading the diagnostics through COMMAND 9 before executing the OFF pulse.