# SNUBBERLESS and logic level Triac behavior at turn-off

### Introduction

The use of Triacs is limited by their switching behavior. Indeed, there is a risk of spurious triggering after conduction if the slope of the decreasing current is too high or if the slope of the reapplied voltage is too high. The designer must then take some precautions: device over-rating, switching aid network (snubber), junction temperature margin, and so on. This generally involves additional costs.

After a brief discussion of commutation when a Triac is turned off, this article describe the behavior of the logic-level and SNUBBERLESS Triacs, which present high commutation capabilities.

## 1 Triac turn-off description

#### 1.1 Definition

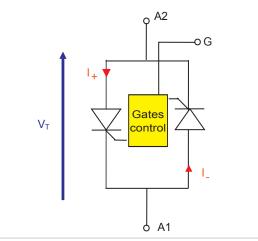

The Triac can be compared to two thyristors mounted back-to-back and coupled with a control area that allows the triggering of this alternating current switch with only one gate (see Figure 1).

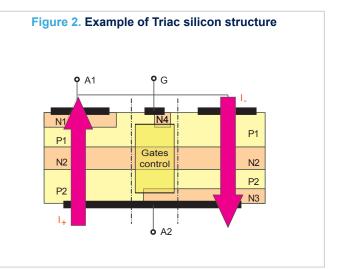

Looking at the Triac silicon structure (see Figure 2), it can be noted that the conduction areas, corresponding to these two thyristors, narrowly overlap each other on the control area.

Figure 1. Simplified equivalent schematic of Triac circuit

During the conduction time, a certain quantity of charge is injected into the structure. The biggest part of this charge disappears by recombination during the current decrease, while another part is extracted after the turn-off by the reverse recovery current. Nonetheless, an excess charge remains, particularly in the neighboring regions of the gate, which can induce the triggering of the other conduction area when the mains voltage is reapplied across the Triac. This is the problem of commutation.

For a given structure at a determined junction temperature, the turn-off behavior depends on:

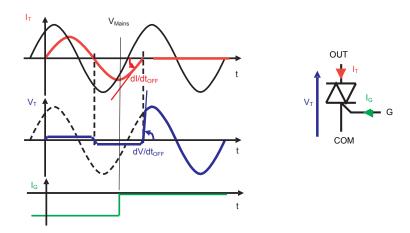

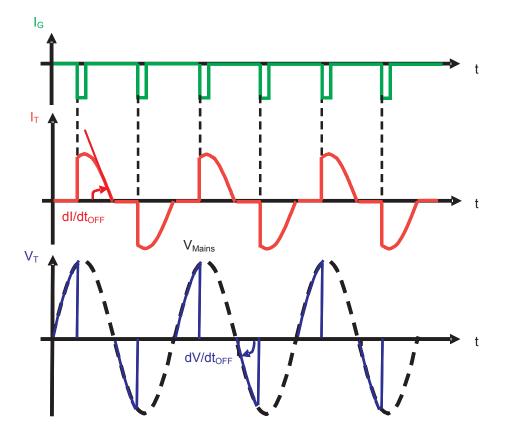

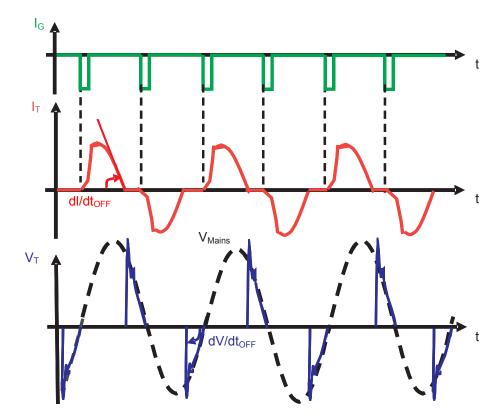

- 1. The quantity of charge which remains when the current drops to zero. The quantity of the charge is linked to the value of the current which was circulating in the Triac approximately 100 µs, about two or three times the minority carriers' life time, before the turn-off. Thus, the parameter to consider is the slope of the decreasing current, called the turn-off dl/dt or dl/dt<sub>OFF</sub> (see Figure 3).

- 2. **The slope of the reapplied voltage during turn-off**. This parameter is the commutation dV/dt, called the turn-off dV/dt or dV/dt<sub>OFF</sub> (see Figure 3). A capacitive current, proportional to the dV/dt<sub>OFF</sub>, flows into the structure, and therefore charges are injected and added to those coming from the previous conduction.

Figure 3. dl/dt and dV/dt at turn-off

AN439 - Rev 4 page 2/17

### 1.2 (dl/dt)c versus (dV/dt)c characterization

To characterize the turn-off Triac behavior, we consider a circuit in which the slope of the decreasing current can be adjusted. In addition, the slope of the reapplied voltage can be controlled by using a circuit of resistors and capacitors connected across the Triac.

For a determined dV/dt<sub>OFF</sub> ((dV/dt)c), we progressively increase the dl/dt<sub>OFF</sub> until a certain level induces the spontaneous triggering of the Triac. This is the critical dl/dt<sub>OFF</sub>, called the (dl/dt)c in Triac datasheets.

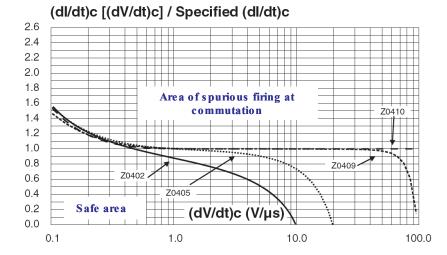

This is also the way to trace the curve of the Triac commutation behavior (see Triac datasheet curve "Relative variation of critical rate of decrease of main current (dl/dt)c versus reapplied (dV/dt)c").

In Triac datasheets, the commutation behavior is specified in different ways according to the Triac technologies. For standard Triacs, a minimum (dV/dt)c is specified for a given (dI/dt)c. For logic-level Triacs, a minimum (dI/dt)c is specified for two given (dV/dt)c (0.1 V/µs and 10 V/µs). For SNUBBERLESS Triacs, a minimum (dI/dt)c is specified without (dV/dt)c limitation.

Figure 4 represents the curve of the commutation behavior obtained with a standard 4 A Triac. This Triac is available with different sensitivities:

• Z0402:  $I_{GT} = 3 \text{ mA}$ • Z0405:  $I_{GT} = 5 \text{ mA}$ • Z0409:  $I_{GT} = 10 \text{ mA}$ • Z0410:  $I_{GT} = 25 \text{ mA}$

For lower sensitivity gate Triacs (Z0409 and Z0410), the (dl/dt)c is slightly modified according to the (dV/dt)c. For sensitive gate Triacs (Z0402 and Z0405), this parameter noticeably decreases when the slope of the reapplied voltage increases.

Figure 4. Relative variation of (dl/dt)c versus (dV/dt)c for a 4 A standard Triac (typical values)

In practice, the current waveform, and thus the  $dI/dt_{OFF}$ , is imposed by the load. Generally, we cannot change it. Therefore, in Triac applications, it is always necessary to know the  $dI/dt_{OFF}$  of the load to choose a Triac with a suitable  $(dI/dt)_c$ . This is the most important parameter.

Suppose a circuit in which the  $dI/dt_{OFF}$  reaches two times the specified  $(dI/dt)_c$ . The standard 4 A Triacs, characterized by the curves in Figure 4, is not suitable even if the  $dV/dt_{OFF}$  is equal to 0.1  $V/\mu$ s.

AN439 - Rev 4 page 3/17

## 1.3 Application requirements

### 1.3.1 Triac with resistive load

In this case, the Triac current and the mains voltage are in phase (see Figure 5). When the Triac switches off (that is, when the current drops to zero), the mains voltage is equal to zero at this instant and increase across the Triac according to the sinusoidal law:

$$V_{Mains} = V_{Max} \times \sin(\omega \times t) \tag{1}$$

For the European mains, i.e. V<sub>RMS</sub> = 220 V at 50 Hz, the slope is:

$$dV/dt_{OFF(V/\mu s)} = V_{RMS(V)} \times \sqrt{2} \times 2\pi \times f(Hz) \times 10^{-6} \approx 0.1 \quad V/\mu s$$

(2)

For 110 V, 60 Hz mains, the slope is:  $dV/dt_{OFF} \approx 0.06 V/\mu s$ .

These relatively low dV/dt<sub>OFF</sub> correspond to the left points on the curves in Figure 4. The dI/dt<sub>OFF</sub> only depends on the load rms current and the mains frequency. For resistive loads, as for most other loads, we have:

$$dl/dt_{OFF(A/\mu s)} = I_{RMS(V)} \times \sqrt{2} \times 2\pi \times f(Hz) \times 10^{-3} \approx 0.5 \times I_{RMS(A)}$$

(3)

Figure 5. Current and voltage waveforms for resistive loads (phase control)

AN439 - Rev 4 page 4/17

#### 1.3.2 Triac with inductive load

An inductive load induces a phase lag between the Triac current and the mains voltage (see Figure 6). When the current drops to zero, the Triac turns off and the voltage is abruptly applied across its terminals. To limit the speed of the reapplied voltage, a resistive/capacitive network mounted in parallel with the Triac is generally used (see Figure 13).

This "snubber" is calculated to limit the  $dV/dt_{OFF}$  at a value for which the  $dI/dt_{OFF}$  is lower than the (dI/dt)c specified in the datasheet. The  $dI/dt_{OFF}$  is also determined in this case by the load impedance (Z) and the mains rms voltage (see AN437 for RC snubber circuit design).

Figure 6. Current and voltage waveforms for inductive loads (phase control)

AN439 - Rev 4 page 5/17

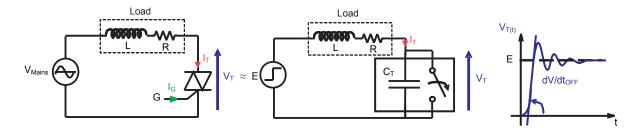

#### 1.4 Triac without snubber network

Without a snubber circuit, the  $dV/dt_{OFF}$  is limited by the capacitance between the anode and cathode junction of the Triac. When the current drops to zero, the Triac is considered a switch that turns off. The dampened oscillating circuit is constituted by the loads, L and R, and the internal capacitance, CT, of the Triac (see Figure 7). The final value E depends on the peak mains voltage and the phase difference ( $\phi$ ) between voltage and current.

Figure 7. Triac commutation on an inductive load without a snubber network

For a second order linear differential equation with a step function input, the voltage variation across the Triac  $(V_{T(t)})$  is given by:

$$\frac{1}{\omega_0^2} \times \frac{d^2 \times V_{T(t)}}{d_t^2} + \frac{2 \times \zeta}{\omega_0} \times \frac{dV_{T(t)}}{dt} + V_{T(t)} = E \tag{4}$$

With damping factor:

$$\zeta = \frac{R(\Omega)}{2} \times \sqrt{\frac{C_{T(F)}}{L(H)}} \tag{5}$$

Undamped natural resonance:

$$\omega_{0(rad/s)} = \frac{1}{\sqrt{L(H)} \times C_{T(F)}} \tag{6}$$

Final voltage value:

$$E = V_{RMS} \times \sqrt{2} \times \sin(\phi) \tag{7}$$

For example, the typical internal capacitances of 1 A, 12 A, and 24 A Triacs are 12 pF, 90 pF, and 180 pF, respectively (without direct voltage junction polarization, worst case). Without a snubber, and for most inductive loads, the damping factor ( $\xi$ ) is generally lower than 1.

For an underdamped oscillating circuit ( $0 \le \xi \le 1$ ), the voltage variation ( $V_{T(t)}$ ) across the Triac is defined by:

$$V_{T(t)} = E - E \times \left( \cos(\omega_p \times t) + \frac{\zeta \times \omega_0}{\omega_p} \times \sin(\omega_p \times t) \right) \times e^{-\zeta \times \omega_0 \times t}$$

(8)

With damped natural resonance:

$$\omega_p = \omega_0 \times \sqrt{1 - \zeta^2} \tag{9}$$

In the case of pure inductive load (R = 0, worst case), the circuit is undamped. The maximum reapplied  $dV/dt_{OFF}$  across the Triac is:

$$dV/dt_{OFF(V/\mu s)} = \frac{V_{RMS(V)} \times \sqrt{2}}{\sqrt{L(H)} \times C_{T(H)}} \times 10^{-6} \quad at \quad t = \frac{\pi}{2 \times \omega_0}$$

(10)

Without a snubber, according to the characteristics of inductive loads, the maximum  $dV/dt_{OFF}$  without a snubber is limited to about 60 V/ $\mu$ s for 100 – 220 V applications. Thus, it is not necessary to get the dl/dt values for dV/dt above 100 V/ $\mu$ s.

AN439 - Rev 4 page 6/17

# 2 Logic level and SNUBBERLESS Triacs

### 2.1 Operation in Q1-Q2-Q3 quadrants

To make significant progress in the Triac technology is to essentially improve the turn-off behavior. In other words, the critical (dl/dt)c has to be improved.

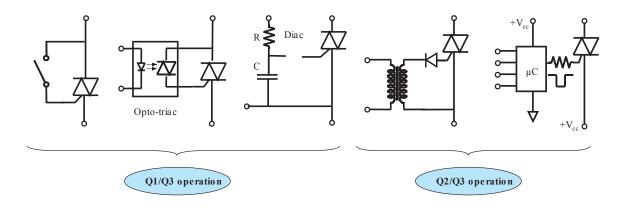

To reach this aim, a different structure has been developed. In this structure, the different active areas have been decoupled to separate the elementary thyristors and the gate area. This improvement provides the gate triggering in the fourth quadrant. In practice, this modification does not lead to a problem because the gate drive circuits generally work in Q1/Q3 or Q2/Q3 (see Figure 8).

Figure 8. Basic gate drive circuits in Q1/Q3 or Q2/Q3 operations

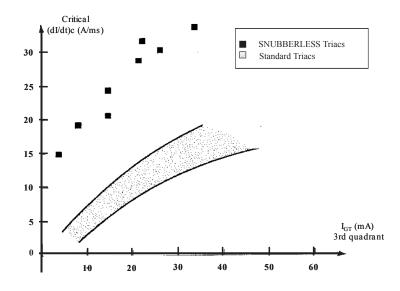

For a given technology, the Triac's commutation behavior depends on the gate sensitivity. The correlation between the critical (dl/dt)c and the triggering gate current for 12 A Triacs is represented in Figure 9. For the same current rating and gate sensitivity, SNUBBERLESS Triacs present a (dl/dt)c at least two times higher than for standard Triacs.

Figure 9. Correlation between commutation behavior and sensitivity (measurement performed on several lots of 12 A Triacs)

Logic-level Triacs use the breakthrough of the SNUBBERLESS technology to improve the trade-off between sensitivity and commutation. Nevertheless, a snubber can still be necessary with these Triacs.

AN439 - Rev 4 page 7/17

## 2.2 Performances and specifications

#### 2.2.1 Logic level Triacs

In this category, sensitive Triacs are defined by a maximum gate current ( $I_{GT}$ ) of 5 mA for the TW type and 10 mA for the SW type.

In the datasheets of logic-level Triacs, a minimum (dl/dt)c is specified for the following cases:

- Resistive load with a (dV/dt)c of 0.1 V/µs

- Inductive load with a (dV/dt)c of 10 V/μs

For example, a 6 A logic-level Triac is specified as follows:

**BTA06 / BTB06 Symbol Test conditions** Quadrant Unit TW sw I<sub>GT</sub><sup>(1)</sup> 1-11-111 Max. 5 10 mΑ  $V_D = 12 \text{ V}, R_L = 30 \Omega$ 1-11-111 V  $V_{\text{GT}}$ Max. 1.3  $(dV/dt)c = 0.1 V/\mu s$ ,  $T_i = 125 °C$ 27 3.5  $(dV/dt)c = 10 V/\mu s, T_i = 125 °C$  $(dI/dt)c^{(2)}$ Min. 1.2 2.4 A/ms Without snubber, T<sub>i</sub> = 125 °C

Table 1. (dl/dt)c and (dV/dt)c specifications for a 6 A logic level Triac

### 2.2.2 Snubberless Triacs

This series covers the range of 6 to 25 A with gate currents of 35 mA (CW type) and 50 mA (BW type). This series has been specially designed so that the Triacs turn off without an external snubber circuit.

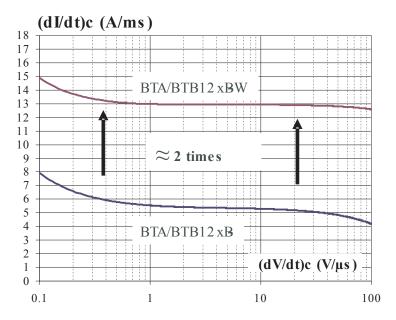

For the same size and gate sensitivity, the (dl/dt)c improvement is at least equal to 2 between SNUBBERLESS and standard Triacs (see Figure 10).

AN439 - Rev 4 page 8/17

<sup>1.</sup> Minimum  $I_{GT}$  is guaranted at 5 % of  $I_{GT}$  max.

<sup>2.</sup> For both polarities of A2 referenced to A1.

Whatever the nature of the load, there is no risk of spurious turn-off triggering if the  $dI/dt_{OFF}$  is lower than the specified (dI/dt)c value. The specified (dI/dt)c for a SNUBBERLESS Triac is higher than the decreasing slope of its rms on-state current specified ( $I_{T(RMS)}$ ).

$$dI/dt_{OFF(A/\mu s)} = I_{RMS(A)} \times \sqrt{2} \times 2\pi \times f(Hz) \times 10^{-3} \approx 0.5 \times I_{RMS(A)}$$

(11)

$$dI/dt_{OFF(A/\mu s)} = 0.44 \times I_{RMS(A)} for 50 Hz$$

$$dI/dt_{OFF(A/\mu s)} = 0.53 \times I_{RMS(A)} for 60 Hz$$

For example, the slope of the decreasing current in a Triac conducting 6 A, 8 A, 10 A, 12 A, 16 A or 25 A when the current drops to zero is given in the Table 2.

Table 2 summarizes also the characteristics of the available BW and CW Snubberless Triacs.

Table 2. (dl/dt)c specification for available BW and CW SNUBBERLESS Triacs and slope of the different decreasing rms on-state currents ( $I_{T(RMS)}$ )

| Type      | I <sub>T(RMS)</sub><br>(A) | Voltage<br>(V <sub>DRM</sub> /<br>V <sub>RRM</sub> )<br>(V) | Suffix | I <sub>GT max.</sub><br>(mA) | Static<br>(dV/dt) min.<br>(V/µs) | (dl/dt)c min. (1) (A/ms) | I <sub>T(RMS)</sub> x 0.5<br>(A/ms) |

|-----------|----------------------------|-------------------------------------------------------------|--------|------------------------------|----------------------------------|--------------------------|-------------------------------------|

| BTA / BTB | 6                          | 600                                                         | CW     | 35                           | 400                              | 3.5                      | 3                                   |

|           |                            |                                                             | BW     | 50                           | 1000                             | 5.3                      |                                     |

|           | 8                          | 600 or 800                                                  | CW     | 35                           | 400                              | 4.5                      | 4                                   |

|           |                            |                                                             | BW     | 50                           | 1000                             | 7                        |                                     |

|           | 10                         |                                                             | CW     | 35                           | 500                              | 5.5                      | 5                                   |

|           |                            |                                                             | BW     | 50                           | 1000                             | 9                        |                                     |

|           | 12                         |                                                             | CW     | 35                           | 500                              | 6.5                      | 6                                   |

|           |                            |                                                             | BW     | 50                           | 1000                             | 12                       |                                     |

|           | 16                         |                                                             | CW     | 35                           | 500                              | 8.5                      | 8                                   |

|           |                            |                                                             | BW     | 50                           | 1000                             | 14                       |                                     |

|           | 25                         |                                                             | CW     | 35                           | 500                              | 13                       | 12.5                                |

|           |                            |                                                             | BW     | 50                           | 1000                             | 22                       |                                     |

<sup>1. (</sup>dl/dt)c specified without snubber

AN439 - Rev 4 page 9/17

## 2.3 Typical applications

## 2.3.1 Logic level Triacs

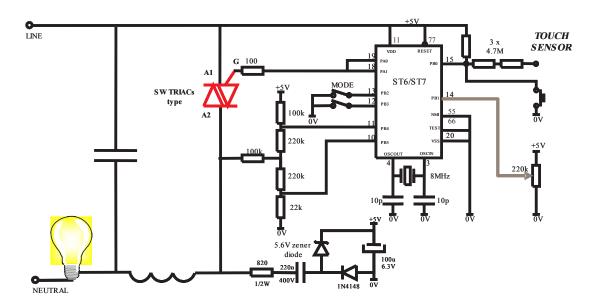

These Triacs can be directly controlled by logic circuits and microcontrollers like the ST6 or ST7 series. Outputs of ST6/ST7 can sink currents up to 20 mA per I/O line and therefore drive TW and SW.

These Triacs are ideal interfaces for power components supplied by 110 V or 220 V, such as valves, heating resistances, and small motors.

The specification of the critical (dl/dt)c on both resistive and inductive loads offers:

- Knowledge of the security margin of the circuit in relation to the risk of spurious triggering

- Optimization of the performance of the Triac used, which results in a cost reduction.

Figure 11. Light dimmer circuit with ST6/ST7 (SW Triacs type is recommended)

AN439 - Rev 4 page 10/17

#### 2.3.2 SNUBBERLESS Triacs

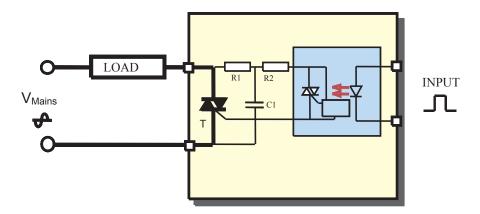

The commutation of SNUBBERLESS Triacs is specified without a (dV/dt)c limitation. The external snubber circuit can be suppressed for Triac turn-off and leads to a noticeable cost reduction. Nevertheless, a snubber circuit is sometimes used to eliminate spurious triggering due to fast line transients (see Figure 13).

Thanks to their significant improvement in the trade-off between gate sensitivity (I<sub>GT</sub>) and critical (dl/dt)c value and also static dV/dt, SNUBBERLESS Triacs are used in circuits that need a high safety margin, such as:

• Static relays in which the load is not well-defined. With standard Triacs, it is difficult to adapt the snubber to all possible cases. SNUBBERLESS Triacs resolve this problem (see Figure 12)

Figure 12. Solid-state relay diagram, using zero voltage switching with opto-Triac

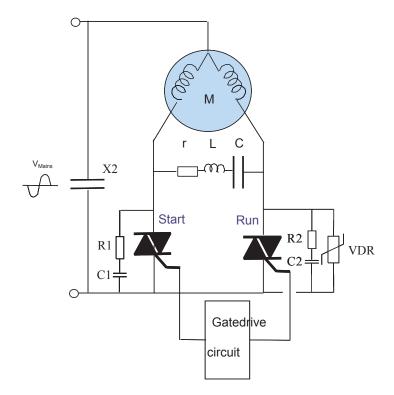

Motor drive circuits. The circuit Figure 12 shows an asynchronous motor controlled in both directions by turning on each Triac alternately.

Figure 13. Motor control circuit using SNUBBERLESS Triacs (Ls + r = network for series protection)

AN439 - Rev 4 page 11/17

Note:

Series impedance (R + L) is needed to protect the blocked Triac in case of unwanted triggering (when the other is already on). Only one clamping device (VDR) provides overvoltage protection for both Triacs (IEC 61000-4-5). Snubber networks (R1C1 and R2C2) eliminate spurious triggering due to fast line transients (IEC 61000-4-4).

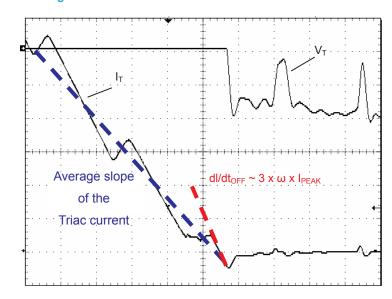

The specified (dl/dt)c for a SNUBBERLESS Triacs is higher than the decreasing slope of its specified RMS on-state current ( $I_{T(RMS)}$ ). This feature is important for several applications, including:

• Circuits in which the dl/dt<sub>OFF</sub> is higher than the dl/dt<sub>OFF</sub> calculated with Eq. (3). For universal motors, due to the impact of the brushes, the dl/dt<sub>OFF</sub> is typically three times higher (see Figure 14). Table 3 illustrates the component choice optimization by using SNUBBERLESS Triacs. For example, an 8 A SNUBBERLESS Triacs is sufficient to control a 110 V / 600 W motor instead of a 16 A standard Triac.

Figure 14. Triac turn-off behavior for universal motors

Table 3. Triac choice for universal motor control

| Power  | Mains voltage and frequency | Load<br>current | I <sub>T(RMS)</sub> | dl/dt <sub>OFF</sub><br>max. | Standard<br>Triac          | SNUBBERLESS<br>Triac |

|--------|-----------------------------|-----------------|---------------------|------------------------------|----------------------------|----------------------|

| 600 W  | 220 V / 50 Hz               | 3 A rms         | 6 A                 | 3.5 A/ms                     | BTx10-600B                 | BTx06-600BW          |

| 600 VV | 110 V / 60 Hz               | 6 A rms         | 10 A                | 7 A/ms                       | BTx16-600B <sup>(2)</sup>  | BTx08-600BW          |

|        | 220 V / 50 Hz               | 6 A rms         | 10 A                | 7 A/ms                       | BTx16-600B <sup>(2)</sup>  | BTx08-600BW          |

| 1200 W | 110 V / 60 Hz               | 12 A rms        | 16 A                | 15 A/ms                      | BTx40-600B<br>/ BTx41-600B | BTx24-600CW          |

- $1. \quad \textit{Maximum dI/dt}_{\textit{OFF}}. \ \textit{This parameter depends on the type of motor and can be higher during start-up}.$

- 2. This type specified at 7 A/ms minimum can be too small. Certain applications could need 25 A standard Triac.

- Circuits that generate waveforms with a very high dl/dt<sub>OFF</sub>, such as inductive loads controlled by a diode bridge (see Figure 15). The current variation at turn-off is then only limited by the parasitic inductance of the line and the diode bridge circuit.

AN439 - Rev 4 page 12/17

V<sub>Mains</sub>

The second of the se

Figure 15. Inductive load controlled by a diode bridge

AN439 - Rev 4 page 13/17

## 3 Conclusion

Thanks to the logic-level and SNUBBERLESS Triacs, the designer can use devices with a commutation behavior that is compatible with all applications in the 50 or 60 Hz range. This includes phase control and static commutation for loads ranging from a few watts to several kilowatts.

These classes of Triacs offer:

- An increase in the security margin of circuits, particularly where there is a risk of spurious triggering

- Reduction of costs by using logic-level Triacs, without the need for an interface between the Triac gate and the logic circuit, or using SNUBBERLESS Triacs, which are specified without a resistive/capacitive network.

AN439 - Rev 4 page 14/17

# **Revision history**

Table 4. Document revision history

| Date        | Revision | Changes                                                                                                              |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------|

| May-1992    | 1        | Initial release.                                                                                                     |

| 19-Apr-2004 | 2        | Stylesheet update. No content change.                                                                                |

| 07-Mar-2008 | 3        | Reformatted to current standards. Complete rewrite for text and graphics. Part numbers updated for current products. |

| 25-Apr-2025 | 4        | Document reworked to improve readability. No content changes.                                                        |

AN439 - Rev 4 page 15/17

# **Contents**

| 1  | Tria   | Triac turn-off description                |                           |    |  |  |  |

|----|--------|-------------------------------------------|---------------------------|----|--|--|--|

|    | 1.1    |                                           |                           |    |  |  |  |

|    | 1.2    | (dl/dt)c versus (dV/dt)c characterization |                           |    |  |  |  |

|    | 1.3    | Application requirements                  |                           |    |  |  |  |

|    |        | 1.3.1                                     | Triac with resistive load | 4  |  |  |  |

|    |        | 1.3.2                                     | Triac with inductive load | 5  |  |  |  |

|    | 1.4    | Triac v                                   | without snubber network   | 6  |  |  |  |

| 2  | Log    | Logic level and SNUBBERLESS Triacs        |                           |    |  |  |  |

|    | 2.1    | Operation in Q1-Q2-Q3 quadrants           |                           |    |  |  |  |

|    | 2.2    | Performances and specifications           |                           |    |  |  |  |

|    |        | 2.2.1                                     | Logic level Triacs        | 8  |  |  |  |

|    |        | 2.2.2                                     | Snubberless Triacs        | 8  |  |  |  |

|    | 2.3    | 3 Typical applications                    |                           |    |  |  |  |

|    |        | 2.3.1                                     | Logic level Triacs        | 10 |  |  |  |

|    |        | 2.3.2                                     | SNUBBERLESS Triacs        | 11 |  |  |  |

| 3  | Con    | clusion                                   | 1                         | 14 |  |  |  |

| Re | vision | history                                   | 1                         | 15 |  |  |  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2025 STMicroelectronics – All rights reserved

AN439 - Rev 4 page 17/17