# AN3994 Application note

Managing the best in class MDmesh™ V and MDmesh™ II super junction technologies: driving and layout key notes

#### Introduction

One of the bigger challenges of the 21<sup>st</sup> century is to deal with the growing need for power and, at the same time, the necessity of product compactness.

The new MDmesh™ V series from STMicroelectronics, based on the super junction concept, meets these targets by offering an extremely low R<sub>DS(on)</sub> value in a given package, unobtainable in standard HV MOSFETs.

In addition to the dramatic reduction of  $R_{DS(on)}$ , super junction MOSFETs are extremely fast in transients and this may lead to some issues when a better performing technology replaces an older version on the same board with the same driving network.

The two main components in the ST super junction MOSFET family (MDmesh™ II and MDmesh™ V) are analyzed and compared in terms of energy losses, voltage, and current rates. It is shown how the external driving network impacts on their performances. Furthermore, a separate section is dedicated to the layout parasitic effects and their impact on MOSFET behavior.

It is clear in the end that layout can be crucial, especially when managing very fast transients, and it must be carefully planned in order to help the MOSFET exploit its best potential.

December 2011 Doc ID 022380 Rev 1 1/53

Contents AN3994

# **Contents**

| 1 | ST n | ST multidrain technology evolution5                                                                 |  |  |  |  |  |

|---|------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2 | Para | Parasitic capacitances overview 8                                                                   |  |  |  |  |  |

| 3 | MOS  | MOSFET standard turn-on and turn-off analysis                                                       |  |  |  |  |  |

| 4 | Gate | Gate charge curve impact on dynamic responses                                                       |  |  |  |  |  |

| 5 | Late | st ST MD II and MD V technology at a glance 20                                                      |  |  |  |  |  |

| 6 | MDI  | I and MD V: which is the lowest loss one?                                                           |  |  |  |  |  |

|   | 6.1  | STB42N65M5 vs. STW48NM60N                                                                           |  |  |  |  |  |

|   | 6.2  | STP35N65M5 vs. STB36NM60N                                                                           |  |  |  |  |  |

|   | 6.3  | STP21N65M5 vs. STP24NM60N                                                                           |  |  |  |  |  |

|   | 6.4  | STP16N65M5 vs. STP18NM60N                                                                           |  |  |  |  |  |

|   | 6.5  | Comments about energy ON comparison                                                                 |  |  |  |  |  |

|   | 6.6  | Comments about energy OFF comparison                                                                |  |  |  |  |  |

| 7 | MOS  | SFET critical parameters in high switching environments 36                                          |  |  |  |  |  |

|   | 7.1  | Parasitic inductance influence on switching losses                                                  |  |  |  |  |  |

|   | 7.2  | Common source inductance                                                                            |  |  |  |  |  |

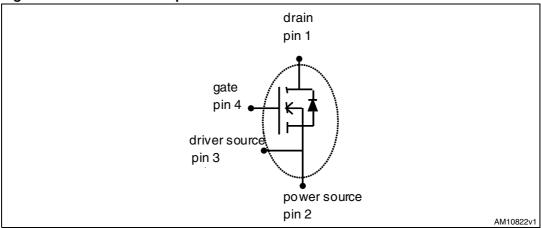

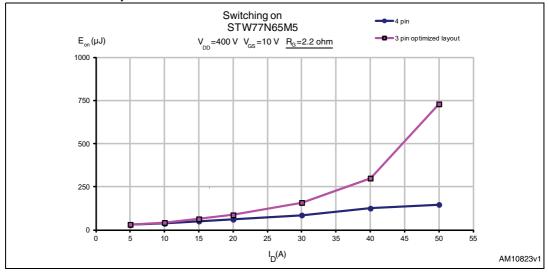

|   | 7.3  | Minimizing common source inductance: layout optimization and Kelvin source connection on STW77N65M5 |  |  |  |  |  |

|   | 7.4  | Minimizing common source inductance impact at turn-off: negative                                    |  |  |  |  |  |

|   |      | V <sub>GMoff</sub>                                                                                  |  |  |  |  |  |

|   | 7.5  | Switching loop inductance                                                                           |  |  |  |  |  |

| В | Revi | sion history 52                                                                                     |  |  |  |  |  |

AN3994 List of figures

# **List of figures**

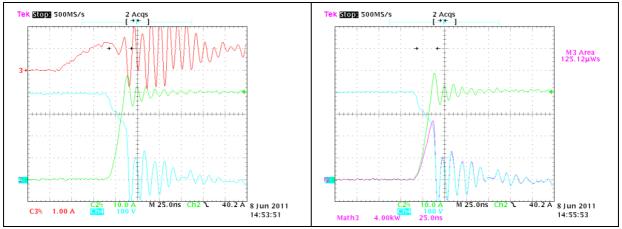

| Figure 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 1.  | Standard HV MOSFET device cross section                                          | . 5 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------------------------------------------------------|-----|

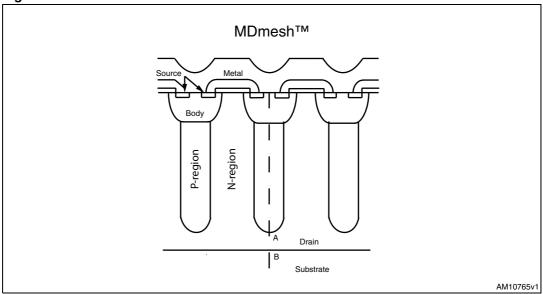

| Figure 4.         ST's HV technology evolution.         7           Figure 5.         N-channel Power MOSFET structure and intrinsic capacitances.         8           Figure 7.         Clamped inductive load test circuit used to carry out the dynamic tests on the MOSFET at 12           Figure 9.         Turn-on of a MOSFET in a clamped inductive load         12           Figure 10.         Turn-off of a MOSFET in a clamped inductive load         13           Figure 11.         Turn-off of a MOSFET in a clamped inductive load         13           Figure 12.         Vg(t) curve measured on STB42NM60N @16 A, 400 V, IG=1.5 mA         17           Figure 13.         Turn-on of STB42N65M5 @16 A, 400 V, 47 W         19           Figure 14.         Turn-on of STB42N65M5 @16 A, 400 V, 47 W         19           Figure 15.         Turn-off of STB42N65M5 @16 A, 400 V, 47 W         19           Figure 17.         Minimum RDS(on) per package achievable by MD II and MD V         20           Figure 18.         STB42N65M5 vs. STW48NM60N dolf at a turn-on @ 8 A/16 A, 400 V         21           Figure 20.         STB42N65M5 vs. STW48NM60N dolf at a turn-on @ 8 A/16 A, 400 V         21           Figure 21.         STB42N65M5 vs. STW48NM60N dolf at a turn-on @ 8 A/16 A, 400 V         22           Figure 22.         STB42N65M5 vs. STW48NM60N dolf at a turn-on @ 8 A/16 A, 400 V         22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 2.  | MD device cross section                                                          | . 5 |

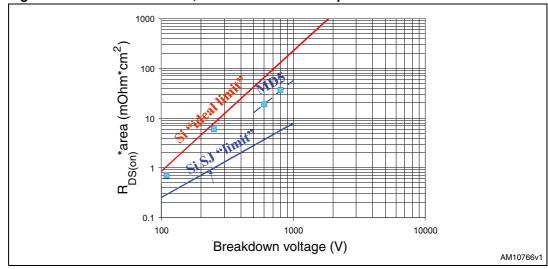

| Figure 5. Figure 6. Figure 7. Figure 8. Figure 7. Clamped inductive load test circuit used to carry out the dynamic tests on the MOSFET in 12 Figure 9. Figure 9. Figure 9. Figure 9. Figure 10. Turn-on of a MOSFET in a clamped inductive load. Figure 11. Figure 11. Figure 12. Figure 13. Figure 14. Figure 13. Figure 14. Figure 14. Figure 15. Figure 16. Figure 17. Figure 17. Figure 18. Figure 18. Figure 19. Figure 19. Figure 19. Figure 19. Figure 19. Figure 10. Figure 10. Figure 10. Figure 10. Figure 11. Figure 12. Figure 13. Figure 14. Figure 14. Figure 16. Figure 17. Figure 17. Figure 17. Figure 18. Figure 18. Figure 19. Figure 21. Figure 21. Figure 21. Figure 22. Figure 22. Figure 23. Figure 24. Figure 24. Figure 25. Figure 25. Figure 26. Figure 27. Figure 27. Figure 28. Figure 28. Figure 29. Figure 20. Figure 20. Figure 21. Figure 30. Figure 30. Figure 41. Figure 41. Figure 51. Figure 61. Figure 61. Figure 71. Figure 72. Figure 73. Figure 74. Figure 75. Figure 75. Figure 76. Figure 77. Figure 77. Figure 78. Figure 79. Figure 89. Figure 80. | Figure 3.  | Silicon ideal limit, SJ limit and ST MD V position                               | . 6 |

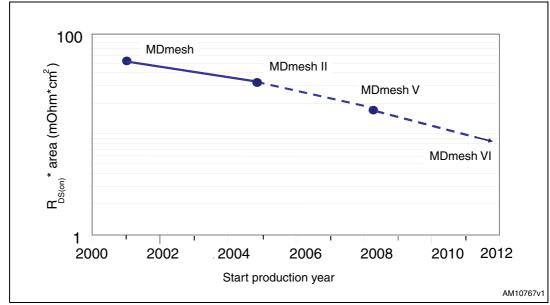

| Figure 7. Figure 7. Figure 7. Figure 7. Figure 8. Clamped inductive load test circuit used to carry out the dynamic tests on the MOSFETs 10 Turn-on of a MOSFET in a clamped inductive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 4.  | ST's HV technology evolution                                                     | . 7 |

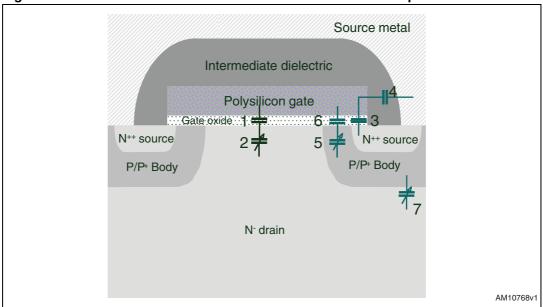

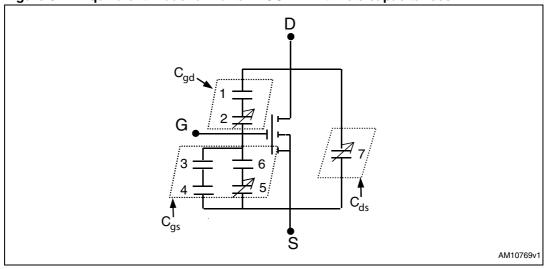

| Figure 7. Clamped inductive load test circuit used to carry out the dynamic tests on the MOSFETS 10 Figure 8. Turn-on of a MOSFET in a clamped inductive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 5.  | N-channel Power MOSFET structure and intrinsic capacitances                      | . 8 |

| Figure 7. Clamped inductive load test circuit used to carry out the dynamic tests on the MOSFETS 10 Figure 8. Turn-on of a MOSFET in a clamped inductive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -          |                                                                                  |     |

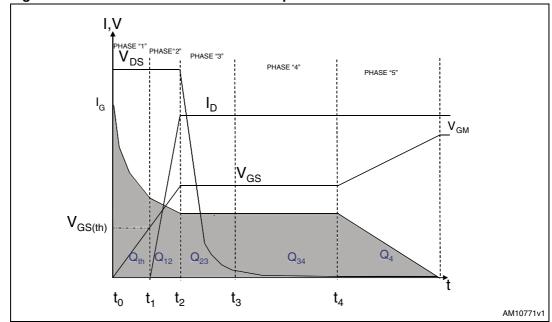

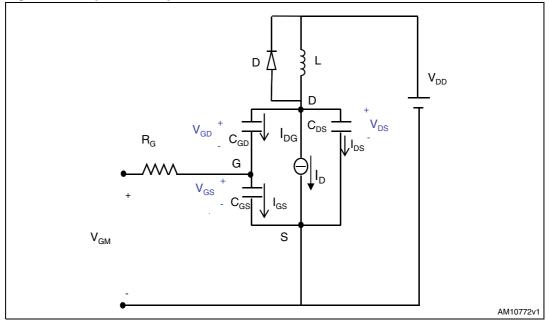

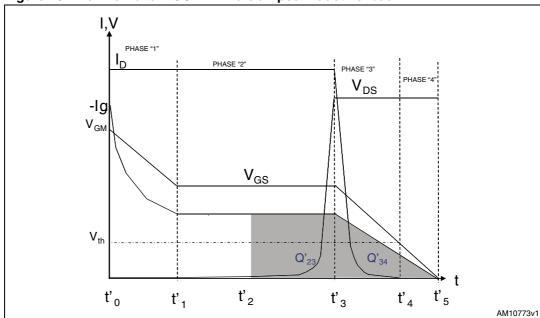

| Figure 9. Equivalent capacitive model of a MOSFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •          |                                                                                  |     |

| Figure 9.         Equivalent capacitive model of a MOSFET in a clamped inductive load         13           Figure 10.         Turn-off of a MOSFET in a clamped inductive load         13           Figure 12.         Vg(t) curve measured on STB42NM60N @ 16 A, 400 V, IG=1.5 mA         17           Figure 12.         Vg(t) curve measured on STW48NM60N @ 16 A, 400 V, 47 W         19           Figure 13.         Turn-on of STB42N65M5 @ 16 A, 400 V, 47 W         19           Figure 15.         Turn-off of STB42N65M5 @ 16 A, 400 V, 47 W         19           Figure 16.         Turn-off of STW48NM60N @ 16 A, 400 V, 47 W         19           Figure 17.         Minimum RDS(on) per package achievable by MD II and MD V         20           Figure 18.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V         21           Figure 19.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V         21           Figure 21.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A 400 V         22           Figure 22.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A 400 V         22           Figure 23.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V         23           Figure 24.         STB42N65M5 vs. STB48NM60N di/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STB36NM60N di/dt at tur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | •          |                                                                                  |     |

| Figure 10. Turn-off of a MOSFET in a clamped inductive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -          |                                                                                  |     |

| Figure 12.         Vg(t) curve measured on STB42NM60N @ 16 A, 400 V, IG=1.5 mA.         17           Figure 12.         Vg(t) curve measured on STW48NM60N @ 16 A, 400 V, IG=1.5 mA.         17           Figure 13.         Turn-on of STB42N65M5 @ 16 A, 400 V, 47 W.         19           Figure 15.         Turn-off of STB42N65M5 @ 16 A, 400 V, 47 W.         19           Figure 15.         Turn-off of STW48NM60N @ 16 A, 400 V, 47 W.         19           Figure 17.         Minimum RDS(on) per package achievable by MD II and MD V.         20           Figure 18.         STB42N65M5 vs. STW48NM60N Eon @ 8 A/16 A, 400 V.         21           Figure 20.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V.         22           Figure 21.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V.         22           Figure 22.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V.         22           Figure 23.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V.         23           Figure 24.         STB42N65M5 vs. STW48NM60N di/dt at turn-off @ 8 A/16 A, 400 V.         23           Figure 25.         STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 8 A/16 A, 400 V.         24           Figure 26.         STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V.         25           Figure 27.         STP35N65M5 vs. STB36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                                                                                  |     |

| Figure 12.         Vg(t) curve measured on STW48NM60N @ 16 A, 400 V, IG=1.5 mA         17           Figure 13.         Turn-on of STB42N65M5 @ 16 A, 400 V, 47 W         19           Figure 15.         Turn-on of STW48NM60N @ 16 A, 400 V, 47 W         19           Figure 15.         Turn-off of STB42N65M5 @ 16 A, 400 V, 47 W         19           Figure 17.         Minimum RDS(on) per package achievable by MD II and MD V         20           Figure 18.         STB42N65M5 vs. STW48NM60N Eon @ 8 A/16 A, 400 V         21           Figure 19.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V         21           Figure 20.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A 400 V         22           Figure 21.         STB42N65M5 vs. STW48NM60N zoom of dv/dt at turn-on @ 8 A/16 A 400 V         22           Figure 22.         STB42N65M5 vs. STW48NM60N zoom of dv/dt at turn-on @ 8 A/16 A 400 V         23           Figure 23.         STB42N65M5 vs. STW48NM60N zoom of dv/dt at turn-on @ 8 A/16 A, 400 V         23           Figure 24.         STB42N65M5 vs. STW48NM60N di/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STB36NM60N zoom of dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N zoom of dv/dt at turn-off @ 8 A/16 A, 400 V         25           Figure 27. <td< td=""><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |            |                                                                                  |     |

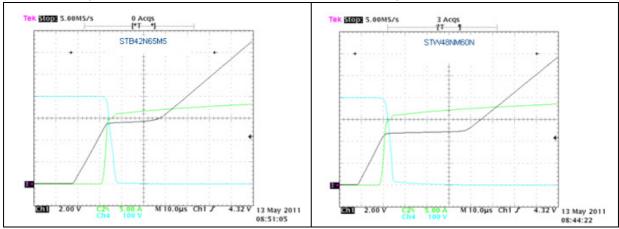

| Figure 13.         Turn-on of STB42N65M5 @ 16 A, 400 V, 47 W         19           Figure 14.         Turn-on of STW48NM60N @ 16 A, 400 V, 47 W         19           Figure 15.         Turn-off of STB42N65M5 @ 16 A, 400 V, 47 W         19           Figure 16.         Turn-off of STW48NM60N @ 16 A, 400 V, 47 W         19           Figure 17.         Minimum RDS(on) per package achievable by MD II and MD V         20           Figure 19.         STB42N65M5 vs. STW48NM60N Eon @ 8 A/16 A, 400 V         21           Figure 20.         STB42N65M5 vs. STW48NM60N dv/dt at turn-on @ 8 A/16 A, 400 V         22           Figure 21.         STB42N65M5 vs. STW48NM60N dv/dt at turn-on @ 8 A/16 A, 400 V         22           Figure 22.         STB42N65M5 vs. STW48NM60N dv/dt at turn-on @ 8 A/16 A, 400 V         23           Figure 23.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         23           Figure 24.         STB42N65M5 vs. STB36NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                                                                                  |     |

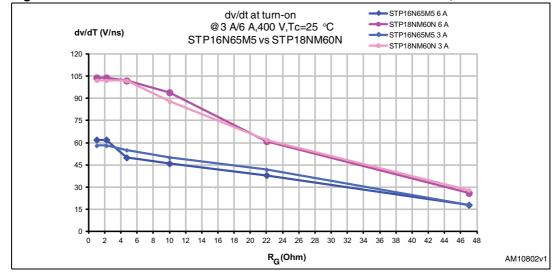

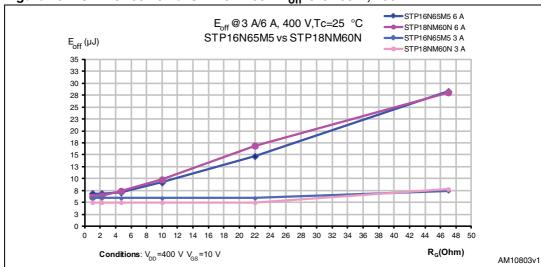

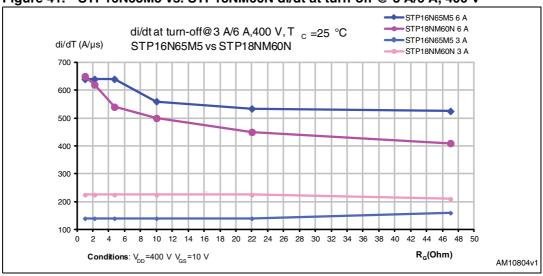

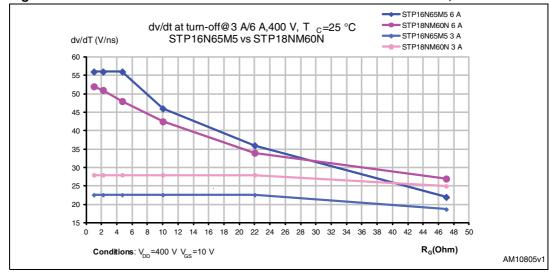

| Figure 14. Turn-off of STW48NM60N @16 A, 400 V, 47 W 19 Figure 15. Turn-off of STB42N65M5 @16 A, 400 V, 47 W 19 Figure 17. Minimum RDS(on) per package achievable by MD II and MD V 20 Figure 18. STB42N65M5 vs. STW48NM60N Eon @ 8 A/16 A, 400 V 21 Figure 19. STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V 21 Figure 20. STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V 22 Figure 21. STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V 22 Figure 22. STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V 22 Figure 23. STB42N65M5 vs. STW48NM60N ben @ 8 A/16 A, 400 V 23 Figure 24. STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V 23 Figure 25. STB42N65M5 vs. STW48NM60N di/dt at turn-off @ 8 A/16 A, 400 V 23 Figure 26. STP35N65M5 vs. STB48NM60N di/dt at turn-off @ 8 A/16 A, 400 V 24 Figure 27. STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 8 A/16 A, 400 V 24 Figure 28. STP35N65M5 vs. STB36NM60N di/dt at turn-on @ 7.5 A/15 A, 400 V 25 Figure 29. STP35N65M5 vs. STB36NM60N di/dt at turn-on @ 7.5 A/15 A, 400 V 26 Figure 29. STP35N65M5 vs. STB36NM60N di/dt at turn-on @ 7.5 A/15 A, 400 V 26 Figure 29. STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V 26 Figure 30. STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V 26 Figure 31. STP21N65M5 vs. STP24NM60N Eon @ 4 A/8 A, 400 V 27 Figure 32. STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V 28 Figure 33. STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V 28 Figure 34. STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V 29 Figure 35. STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V 29 Figure 36. STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V 29 Figure 37. STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V 30 Figure 38. STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V 30 Figure 39. STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V 30 Figure 39. STP16N65M5 vs. STP18NM60N di/dt at turn-off @ 3 A/6 A, 400 V 30 Figure |            |                                                                                  |     |

| Figure 15.         Turn-off of STB42N65M5 @ 16 A, 400 V, 47 W.         19           Figure 16.         Turn-off of STW48NM60N @ 16 A, 400 V, 47 W.         19           Figure 18.         Minimum RDS(on) per package achievable by MD II and MD V.         20           Figure 18.         STB42N65M5 vs. STW48NM60N Eon @ 8 A/16 A, 400 V.         21           Figure 29.         STB42N65M5 vs. STW48NM60N dv/dt at turn-on @ 8 A/16 A, 400 V.         22           Figure 20.         STB42N65M5 vs. STW48NM60N dv/dt at turn-on @ 8 A/16 A, 400 V.         22           Figure 21.         STB42N65M5 vs. STW48NM60N zoom of dv/dt at turn-on @ 8 A/16 A, 400 V.         22           Figure 22.         STB42N65M5 vs. STW48NM60N dv/dt at turn-on @ 8 A/16 A, 400 V.         23           Figure 23.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V.         23           Figure 24.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V.         24           Figure 25.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V.         24           Figure 26.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V.         25           Figure 27.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V.         26           Figure 28.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V.         26           Figure 30. <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |            |                                                                                  |     |

| Figure 16.         Turn-off of STW48NM60N @16 A, 400 V, 47 W         19           Figure 17.         Minimum RDS(on) per package achievable by MD II and MD V         20           Figure 19.         STB42N65M5 vs. STW48NM60N Eon @ 8 A/16 A, 400 V         21           Figure 19.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V         21           Figure 20.         STB42N65M5 vs. STW48NM60N dv/dt at turn-on @ 8 A/16 A 400 V         22           Figure 21.         STB42N65M5 vs. STW48NM60N zoom of dv/dt at turn-on @ 8 A/16 A 400 V         23           Figure 22.         STB42N65M5 vs. STW48NM60N Eoff @ 8 A/16 A, 400 V         23           Figure 23.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         23           Figure 24.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 28.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB24NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |            |                                                                                  |     |

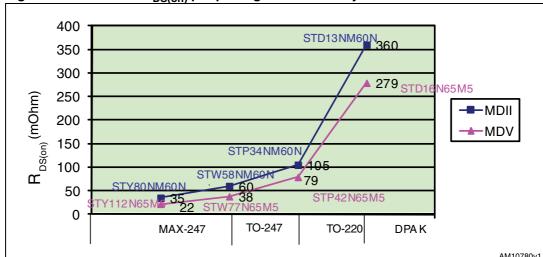

| Figure 17.         Minimum RDS(on) per package achievable by MD II and MD V         20           Figure 18.         STB42N65M5 vs. STW48NM60N Eon @ 8 A/16 A, 400 V         21           Figure 19.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V         21           Figure 20.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A 400 V         22           Figure 21.         STB42N65M5 vs. STW48NM60N bene @ 8 A/16 A, 400 V         22           Figure 22.         STB42N65M5 vs. STW48NM60N Eoff @ 8 A/16 A, 400 V         23           Figure 23.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V         23           Figure 24.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 8 A/16 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N Eon @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N Eonf @ 7.5 A/15 A, 400 V         25           Figure 28.         STP35N65M5 vs. STB36NM60N Eonf @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N Eonf @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N Eonf @ 7.5 A/15 A, 400 V         26           Figure 30.         STP21N65M5 vs. STP24NM60N Eonf @ 7.5 A/15 A, 400 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |            |                                                                                  |     |

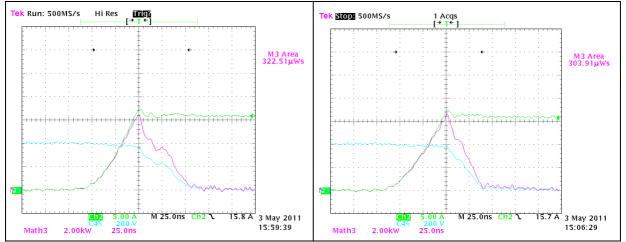

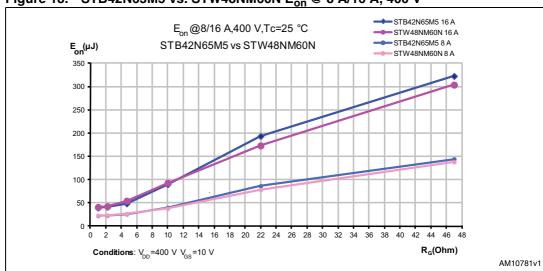

| Figure 18.         STB42N65M5 vs. STW48NM60N Eon @ 8 A/16 A, 400 V         21           Figure 20.         STB42N65M5 vs. STW48NM60N dv/dt at turn-on @ 8 A/16 A, 400 V         22           Figure 21.         STB42N65M5 vs. STW48NM60N dv/dt at turn-on @ 8 A/16 A, 400 V         22           Figure 22.         STB42N65M5 vs. STW48NM60N zoom of dv/dt at turn-on @ 8 A/16 A, 400 V         22           Figure 23.         STB42N65M5 vs. STW48NM60N Eoff @ 8 A/16 A, 400 V         23           Figure 24.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N Eon @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 28.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 31.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 32.         STP21N65M5 vs. STP24NM60N Eon @ 4 A/8 A, 400 V         28           Figure 33.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 34.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |            |                                                                                  |     |

| Figure 19.         STB42N65M5 vs. STW48NM60N di/dt at turn-on @ 8 A/16 A, 400 V         21           Figure 20.         STB42N65M5 vs. STW48NM60N dv/dt at turn-on @ 8 A/16 A 400 V         22           Figure 21.         STB42N65M5 vs. STW48NM60N zoom of dv/dt at turn-on @ 8 A/16 A 400 V         22           Figure 22.         STB42N65M5 vs. STW48NM60N Eoff @ 8 A/16 A, 400 V         23           Figure 23.         STB42N65M5 vs. STW48NM60N di/dt at turn-off @ 8 A/16 A, 400 V         23           Figure 24.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STB36NM60N Eon @ 7.5 A/15 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N beoff @ 7.5 A/15 A, 400 V         25           Figure 28.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 30.         STP35N65M5 vs. STP24NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 31.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 32.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | _          |                                                                                  |     |

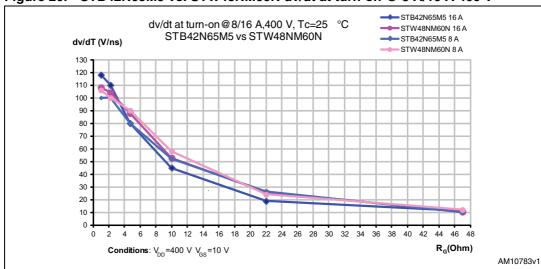

| Figure 20.         STB42N65M5 vs. STW48NM60N dv/dt at turn-on @ 8 A/16 A 400 V         22           Figure 21.         STB42N65M5 vs. STW48NM60N zoom of dv/dt at turn-on @ 8 A/16 A 400 V         22           Figure 22.         STB42N65M5 vs. STW48NM60N Eoff @ 8 A/16 A, 400 V         23           Figure 23.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 24.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N Eon @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 28.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 30.         STP35N65M5 vs. STP24NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 31.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 32.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 33.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |            |                                                                                  |     |

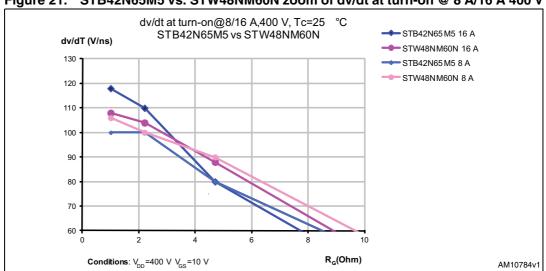

| Figure 21.         STB42N65M5 vs. STW48NM60N zoom of dv/dt at turn-on @ 8 A/16 A 400 V         22           Figure 22.         STB42N65M5 vs. STW48NM60N Eoff @ 8 A/16 A, 400 V         23           Figure 23.         STB42N65M5 vs. STW48NM60N di/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 24.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STB36NM60N Eoff @ 7.5 A/15 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N di/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 28.         STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 30.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 31.         STP21N65M5 vs. STP24NM60N be on @ 4 A/ 8 A, 400 V         27           Figure 32.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 33.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         29           Figure 34.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         29           Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -          |                                                                                  |     |

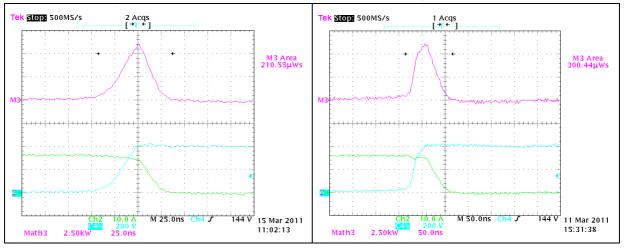

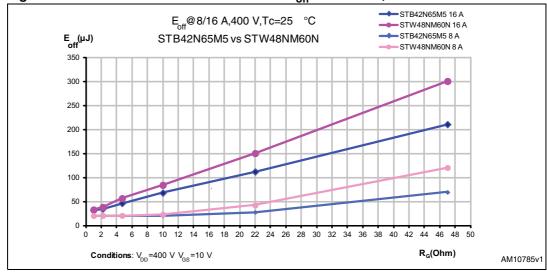

| Figure 22.         STB42N65M5 vs. STW48NM60N Eoff @ 8 A/16 A, 400 V         23           Figure 23.         STB42N65M5 vs. STW48NM60N di/dt at turn-off @ 8 A/16 A, 400 V         23           Figure 24.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STB36NM60N Eon @ 7.5 A/15 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N di/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 28.         STP35N65M5 vs. STB36NM60N Eoff @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 30.         STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 31.         STP21N65M5 vs. STP24NM60N Eoff @ 7.5 A/15 A, 400 V         27           Figure 32.         STP21N65M5 vs. STP24NM60N Eoff @ 7.5 A/15 A, 400 V         28           Figure 33.         STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V         28           Figure 34.         STP21N65M5 vs. STP24NM60N Eoff @ 4 A/8 A, 400 V         29           Figure 35.         STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V         29           Figure 36.         STP218M5M0N di/dt a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                                                                                  |     |

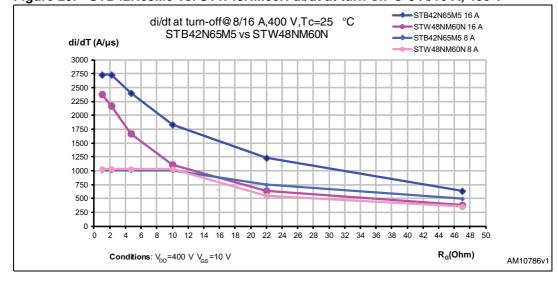

| Figure 23.         STB42N65M5 vs. STW48NM60N di/dt at turn-off @ 8 A/16 A, 400 V         23           Figure 24.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/ 16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STB36NM60N Eon @ 7.5 A/15 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N di/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A 400 V         25           Figure 28.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 30.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 31.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         27           Figure 32.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 33.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 34.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         29           Figure 35.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 3 A/6 A, 400 V         30           Figure 36.         STP16N65M5 vs. STP18NM60N dv/dt at turn-on @ 3 A/6 A, 400 V         30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -          |                                                                                  |     |

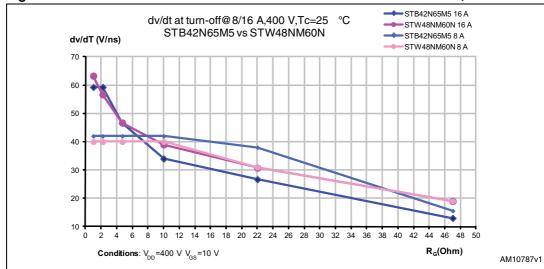

| Figure 24.         STB42N65M5 vs. STW48NM60N dv/dt at turn-off @ 8 A/ 16 A, 400 V         24           Figure 25.         STP35N65M5 vs. STB36NM60N Eon @ 7.5 A/15 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A 400 V         25           Figure 28.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 30.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 31.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 32.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 33.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         28           Figure 34.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         29           Figure 35.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         29           Figure 36.         STP21N65M5 vs. STP18NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         30           Figure 37.         STP16N65M5 vs. STP18NM60N dv/dt at turn-off @ 3 A/6 A, 400 V         31      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -          |                                                                                  |     |

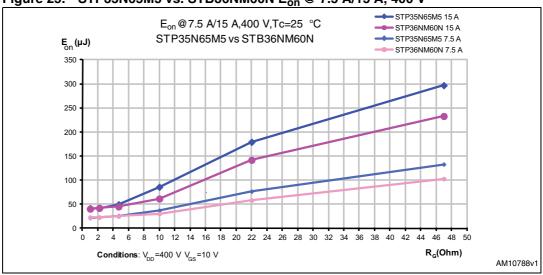

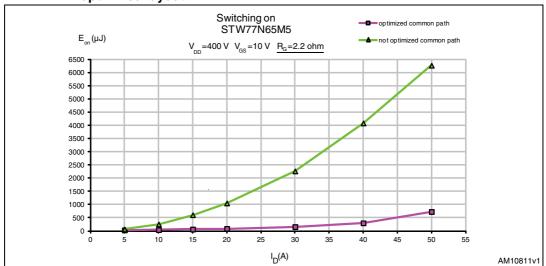

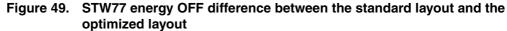

| Figure 25.         STP35N65M5 vs. STB36NM60N Eon @ 7.5 A/15 A, 400 V         24           Figure 26.         STP35N65M5 vs. STB36NM60N di/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 28.         STP35N65M5 vs. STB36NM60N Eoff @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 30.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 31.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 32.         STP21N65M5 vs. STP24NM60N Eon @ 4 A/8 A, 400 V         28           Figure 33.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 34.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         29           Figure 35.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         29           Figure 36.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         30           Figure 37.         STP16N65M5 vs. STP18NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         30           Figure 38.         STP16N65M5 vs. STP18NM60N dv/dt at turn-on @ 3 A/6 A, 400 V         31           Figure 49.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -          |                                                                                  |     |

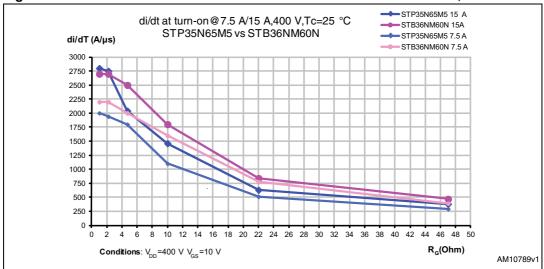

| Figure 26.         STP35N65M5 vs. STB36NM60N di/dt at turn-on @ 7.5 A/15 A, 400 V         25           Figure 27.         STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A 400 V         25           Figure 28.         STP35N65M5 vs. STB36NM60N Eoff @ 7.5 A/15 A, 400 V         26           Figure 39.         STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 30.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 31.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         27           Figure 32.         STP21N65M5 vs. STP24NM60N di/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 33.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 34.         STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V         29           Figure 35.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         29           Figure 36.         STP21N65M5 vs. STP18NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         30           Figure 37.         STP16N65M5 vs. STP18NM60N dv/dt at turn-on @ 3 A/6 A, 400 V         30           Figure 38.         STP16N65M5 vs. STP18NM60N dv/dt at turn-on @ 3 A/6 A, 400 V         31           Figure 40.         STP16N65M5 vs. STP18NM60N dv/dt at turn-on @ 3 A/6 A, 400 V         32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -          |                                                                                  |     |

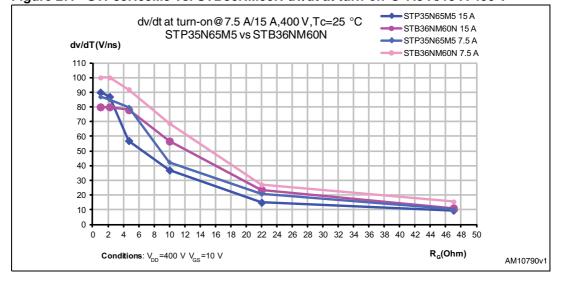

| Figure 27.       STP35N65M5 vs. STB36NM60N dv/dt at turn-on @ 7.5 A/15 A 400 V       25         Figure 28.       STP35N65M5 vs. STB36NM60N Eoff @ 7.5 A/15 A, 400 V       26         Figure 29.       STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V       26         Figure 30.       STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V       27         Figure 31.       STP21N65M5 vs. STP24NM60N Eon @ 4 A/8 A, 400 V       27         Figure 32.       STP21N65M5 vs. STP24NM60N di/dt at turn-on @ 4 A/8 A, 400 V       28         Figure 33.       STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V       28         Figure 34.       STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V       29         Figure 35.       STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V       29         Figure 36.       STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V       30         Figure 37.       STP1N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V       30         Figure 38.       STP1N65M5 vs. STP18NM60N dv/dt at turn-off @ 4 A/8 A, 400 V       30         Figure 39.       STP16N65M5 vs. STP18NM60N dv/dt at turn-off @ 3 A/6 A, 400 V       31         Figure 40.       STP16N65M5 vs. STP18NM60N dv/dt at turn-off @ 3 A/6 A, 400 V       32         Figure 41.       STP16N65M5 vs. STP18NM60N dv/dt at turn-off @ 3 A/6 A, 400 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -          |                                                                                  |     |

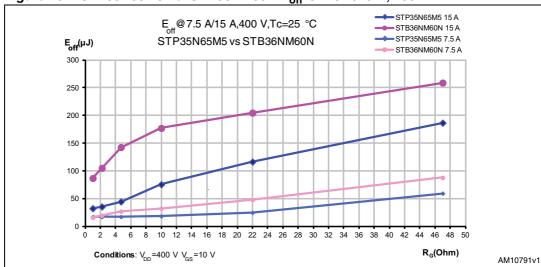

| Figure 28.         STP35N65M5 vs. STB36NM60N Eoff @ 7.5 A/15 A, 400 V         26           Figure 29.         STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 30.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 31.         STP21N65M5 vs. STP24NM60N Eon @ 4 A/8 A, 400 V         27           Figure 32.         STP21N65M5 vs. STP24NM60N di/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 33.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 34.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         29           Figure 35.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         29           Figure 36.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         30           Figure 37.         STP16N65M5 vs. STP18NM60N Eon @ 3 A/6 A, 400 V         30           Figure 38.         STP16N65M5 vs. STP18NM60N dv/dt at turn-on @ 3 A/6 A, 400 V         31           Figure 40.         STP16N65M5 vs. STP18NM60N dv/dt at turn-on @ 3 A/6 A, 400 V         32           Figure 41.         STP16N65M5 vs. STP18NM60N dv/dt at turn-off @ 3 A/6 A, 400 V         32           Figure 42.         STP16N65M5 vs. STP18NM60N dv/dt at turn-off @ 3 A/6 A, 400 V         33           Figure 43.         E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -          |                                                                                  |     |

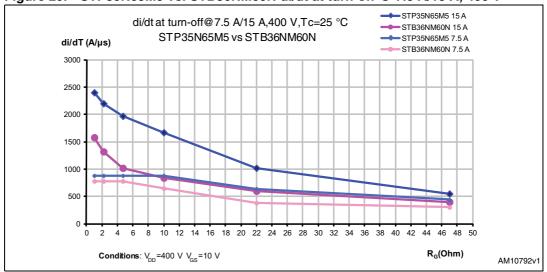

| Figure 29.         STP35N65M5 vs. STB36NM60N di/dt at turn-off @ 7.5 A/15 A, 400 V         26           Figure 30.         STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V         27           Figure 31.         STP21N65M5 vs. STP24NM60N Eon @ 4 A/8 A, 400 V         27           Figure 32.         STP21N65M5 vs. STP24NM60N di/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 33.         STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V         28           Figure 34.         STP21N65M5 vs. STP24NM60N Eoff @ 4 A/8 A, 400 V         29           Figure 35.         STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V         29           Figure 36.         STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         30           Figure 37.         STP16N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V         30           Figure 38.         STP16N65M5 vs. STP18NM60N Eoff @ 3 A/6 A, 400 V         30           Figure 39.         STP16N65M5 vs. STP18NM60N dv/dt at turn-on @ 3 A/6 A, 400 V         31           Figure 40.         STP16N65M5 vs. STP18NM60N dv/dt at turn-on @ 3 A/6 A, 400 V         32           Figure 41.         STP16N65M5 vs. STP18NM60N dv/dt at turn-off @ 3 A/6 A, 400 V         32           Figure 42.         STP16N65M5 vs. STP18NM60N dv/dt at turn-off @ 3 A/6 A, 400 V         33           Figure 43.         Equ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -          |                                                                                  |     |

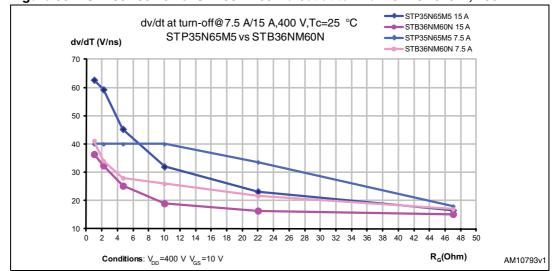

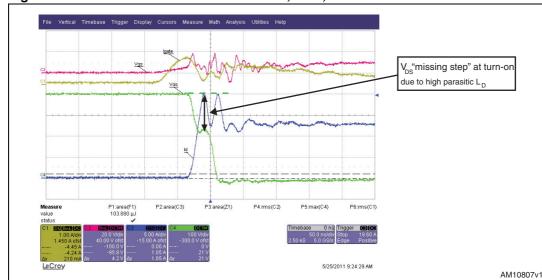

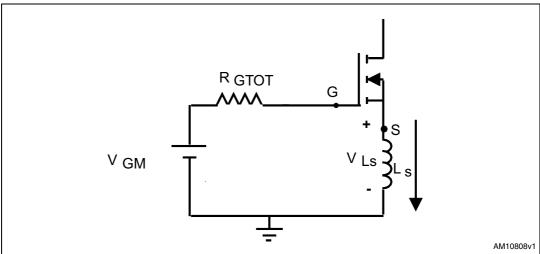

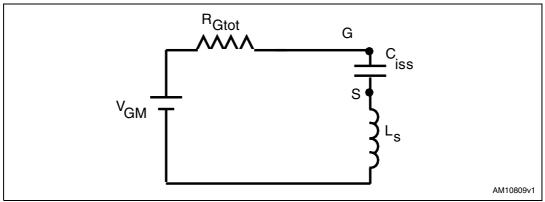

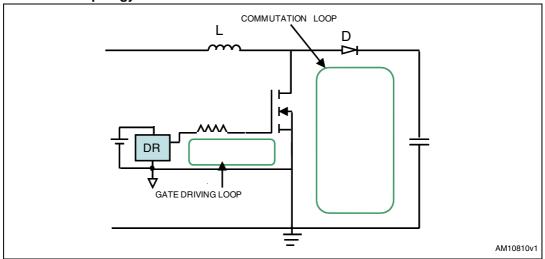

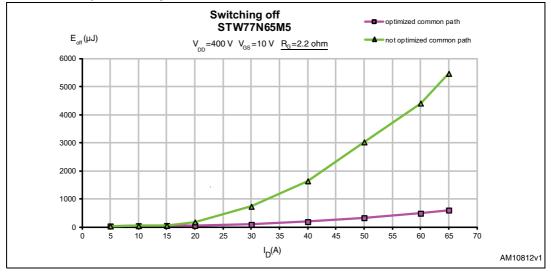

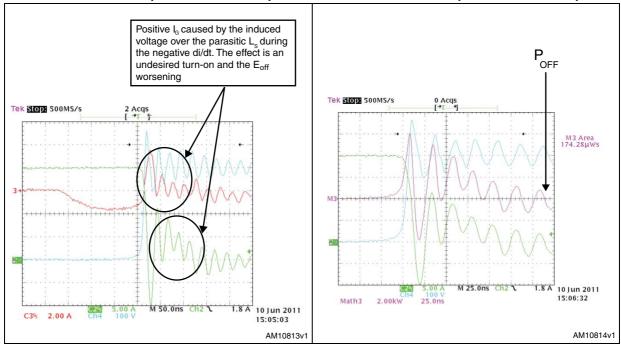

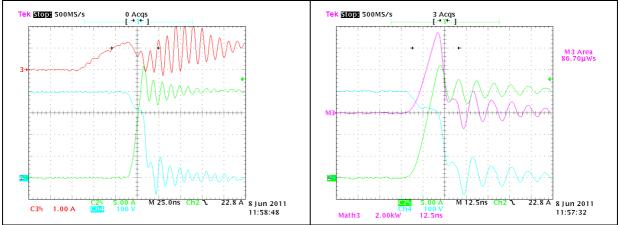

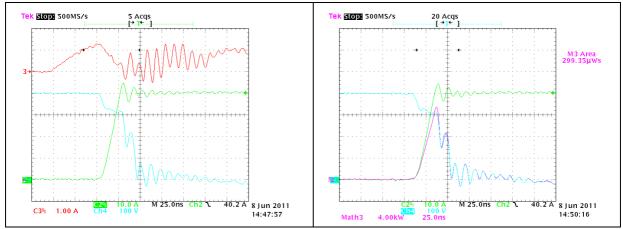

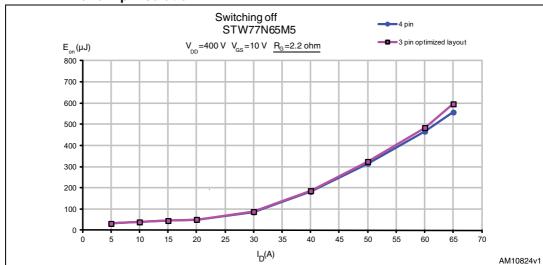

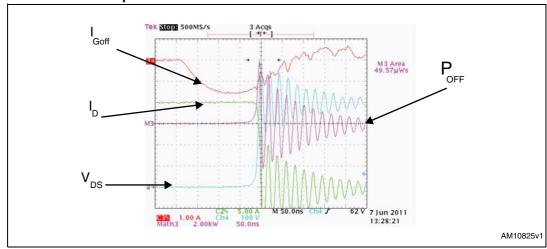

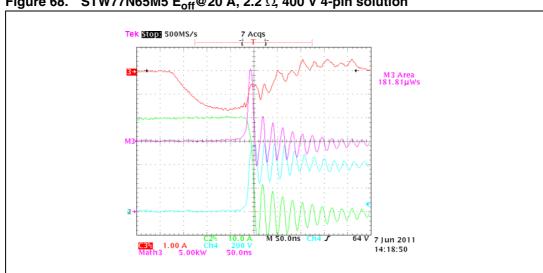

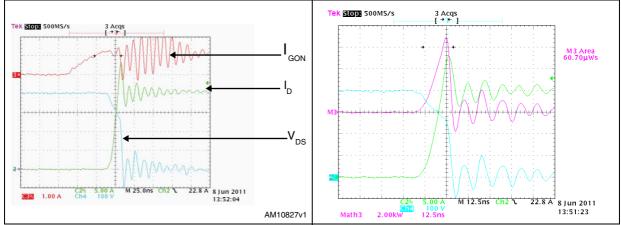

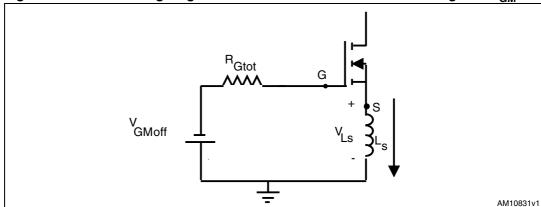

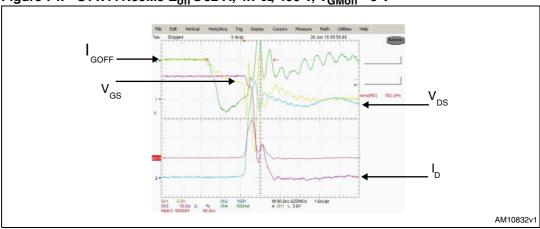

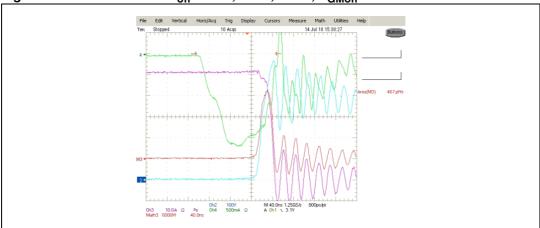

| Figure 30.       STP35N65M5 vs. STB36NM60N dv/dt at turn-off @ 7.5 A/15 A, 400 V       27         Figure 31.       STP21N65M5 vs. STP24NM60N Eon @ 4 A/8 A, 400 V       27         Figure 32.       STP21N65M5 vs. STP24NM60N di/dt at turn-on @ 4 A/8 A, 400 V       28         Figure 33.       STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V       28         Figure 34.       STP21N65M5 vs. STP24NM60N Eoff @ 4 A/8 A, 400 V       29         Figure 35.       STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V       29         Figure 36.       STP21N65M5 vs. STP24NM60N dv/dt at turn-off @ 4 A/8 A, 400 V       30         Figure 37.       STP16N65M5 vs. STP18NM60N Eon @ 3 A/6 A, 400 V       30         Figure 38.       STP16N65M5 vs. STP18NM60N di/dt at turn-on @ 3 A/6 A, 400 V       31         Figure 40.       STP16N65M5 vs. STP18NM60N dv/dt at turn-on @ 3 A/6 A, 400 V       32         Figure 41.       STP16N65M5 vs. STP18NM60N di/dt at turn-off @ 3 A/6 A, 400 V       32         Figure 42.       STP16N65M5 vs. STP18NM60N dv/dt at turn-off @ 3 A/6 A, 400 V       32         Figure 43.       Equivalent capacitive model of a MOSFET with parasitic inductances at turn-on       36         Figure 44.       Turn-on of STW77N65M5@400 V, 13 A, 25 °C       37         Figure 45.       Equivalent driving circuit of a MOSFET at turn-on with parasitic source inductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -          |                                                                                  |     |

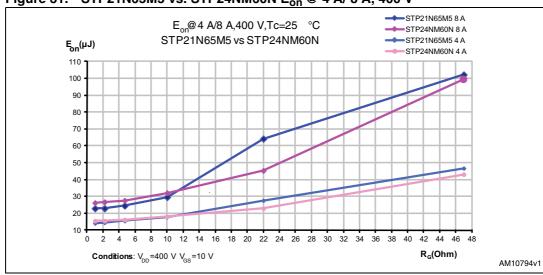

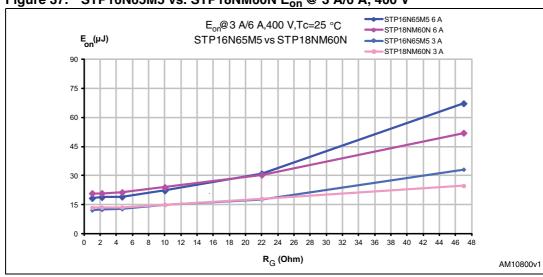

| Figure 31. STP21N65M5 vs. STP24NM60N Eon @ 4 A/8 A, 400 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -          |                                                                                  |     |

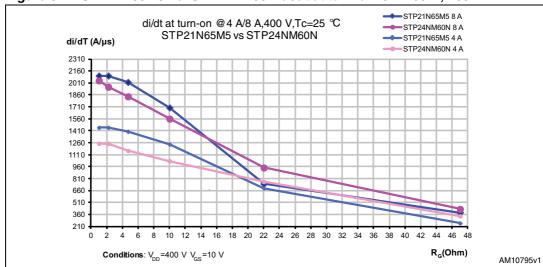

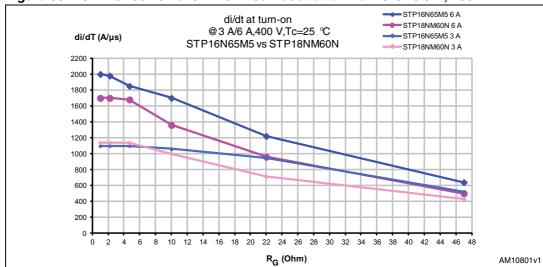

| Figure 32. STP21N65M5 vs. STP24NM60N di/dt at turn-on @ 4 A/8 A, 400 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -          |                                                                                  |     |

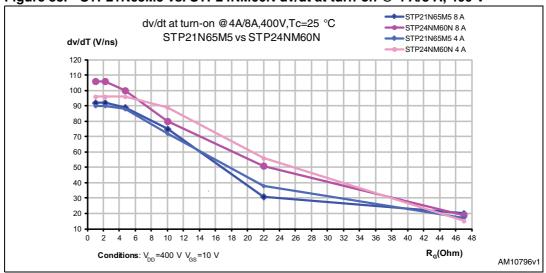

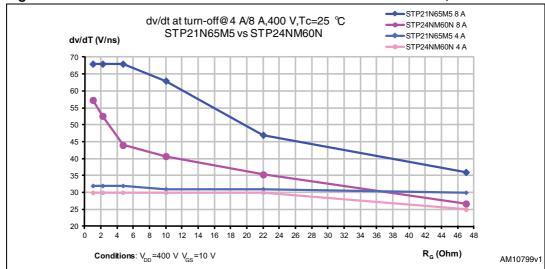

| Figure 33. STP21N65M5 vs. STP24NM60N dv/dt at turn-on @ 4 A/8 A, 400 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -          |                                                                                  |     |

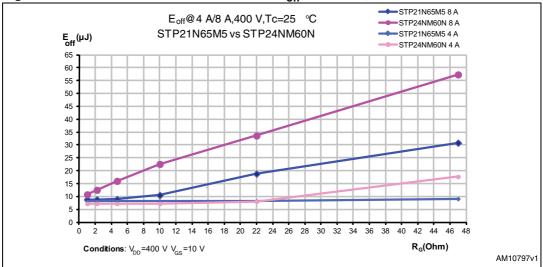

| Figure 34. STP21N65M5 vs. STP24NM60N Eoff @ 4 A/8 A, 400 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -          |                                                                                  |     |

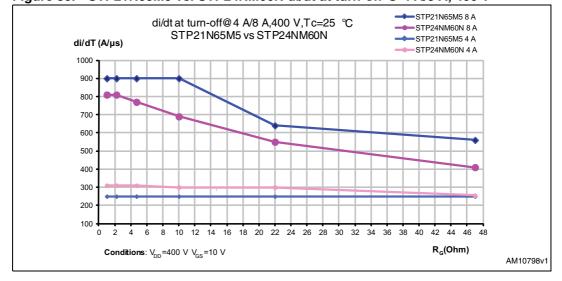

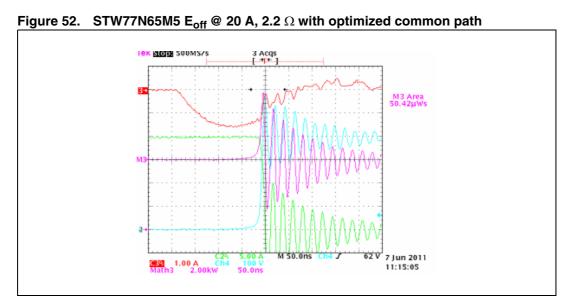

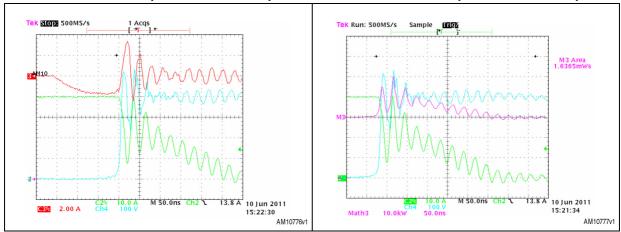

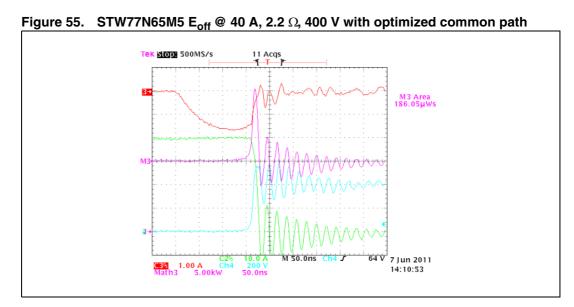

| Figure 35. STP21N65M5 vs. STP24NM60N di/dt at turn-off @ 4 A/8 A, 400 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -          |                                                                                  |     |