# AN3261 Application note

# Dual push-button Smart Reset<sup>™</sup> devices with user-adjustable setup delays

### Introduction

The Smart Reset<sup>™</sup> family of devices consists of several products with a combination of features selected to best suit most typical applications. Their basic common feature is dual-button reset with setup delay that requires both input reset buttons to be continuously pressed for a defined period of time. This improves system stability compared to simple manual reset button devices and eliminates the need for a traditional reset access hole (e.g. two standard keys on the mobile phone keyboard can be used as Smart Reset<sup>™</sup> inputs). Numerous additional features and device options are factory-programmed or can be implemented upon request.

Common STM65xx Smart Reset™ family features include:

- Dual-button Smart Reset<sup>™</sup> inputs

- V<sub>CC</sub> range 1.0 to 5.5 V (active-low output valid)

- Industrial operating temperature range -40 °C to +85 °C

- Space-saving TDFN8 package (2 mm x 2 mm x 0.75 mm)

- RoHS compliance

Differentiating features of the devices are:

- With or without Power-on Reset (POR)

- With or without V<sub>CC</sub> monitoring

- Independent battery monitoring feature with battery-low warning (STM6505 only)

- Input logic voltage levels: standard CMOS or fixed threshold

- Smart Reset<sup>™</sup> output characteristics

- Defined reset pulse duration or push-button controlled (undefined) reset pulse duration

- Reset pulse duration: factory-programmed or capacitor-adjustable

- Smart Reset<sup>™</sup> delay: tri-state / dual-state / capacitor-adjustable

- Open-drain or push-pull reset output

- Single or dual reset output

September 2010

Doc ID 17837 Rev 1

1/17

Contents AN3261

# **Contents**

| 1 | Features                              |                                                    |  |  |

|---|---------------------------------------|----------------------------------------------------|--|--|

| 2 | Турі                                  | cal application diagrams                           |  |  |

|   | 2.1                                   | Single-button reset 5                              |  |  |

|   | 2.2                                   | Dual-button reset 7                                |  |  |

|   | 2.3                                   | Multiple-button reset                              |  |  |

|   | 2.4                                   | Input pull-up considerations (CMOS/fixed levels) 9 |  |  |

|   | 2.5                                   | Output pull-up considerations                      |  |  |

|   | 2.6                                   | Reliability note                                   |  |  |

| 3 | Demonstration boards, promotion tools |                                                    |  |  |

|   | 3.1                                   | STM6503 demonstration board11                      |  |  |

|   | 3.2                                   | STM65xx interposer boards                          |  |  |

|   | 3.3                                   | Smartphone demonstration example                   |  |  |

| 4 | Con                                   | clusion                                            |  |  |

| 5 | Revi                                  | sion history                                       |  |  |

AN3261 List of figures

# **List of figures**

| Figure 1.  | Single-button Smart Reset™ typical application diagram, with "early-warning"   |    |

|------------|--------------------------------------------------------------------------------|----|

|            | feature, STM6503                                                               | 5  |

| Figure 2.  | Timing diagram - single push-button Smart Reset™                               | 6  |

| Figure 3.  | Dual push-button Smart Reset™ typical application diagram, STM6503             | 7  |

| Figure 4.  | Timing diagram - dual push-button Smart Reset™                                 | 7  |

| Figure 5.  | Three push-button delayed Smart Reset™ typical application diagram, STM6503    | 8  |

| Figure 6.  | Timing diagram - three push-button Smart Reset™                                | 9  |

| Figure 7.  | Smart Reset <sup>™</sup> demonstration board, STM6503                          | 11 |

| Figure 8.  | The STM65xx interposer boards; a dedicated board is available for each STM65xx |    |

| _          | Smart Reset™ device                                                            | 12 |

| Figure 9.  | Smartphone demonstration example shows STM6503 implemented in an actual        |    |

| · ·        | application                                                                    | 13 |

| Figure 10. | Smart Reset <sup>™</sup> demonstration in an actual smartphone application     | 14 |

Features AN3261

### 1 Features

• The Smart Reset™ functionality is a feature that introduces a reset output response delay. Both of the Smart Reset™ input buttons must be pressed for a defined t<sub>SRC</sub> period, only after which an output reset pulse is generated. This results in a robust hardware reset. The reset function can then be assigned to the existing keys of a device, which eliminates the traditional reset hole in the back cover of the device, while maintaining system stability. All the STM65xx family devices have this feature with the exception of the STM6504.

- The edge trigger functionality is a reset input with an immediate reset response and a special debounce feature. Found only on the STM6504 (a device with single-button edge trigger immediate reset and a single-button delayed Smart Reset™ input, independent but with a common reset output).

- V<sub>CC</sub> monitoring/undervoltage reset. When the monitored V<sub>CC</sub> voltage drops below the factory-programmed undervoltage reset threshold V<sub>RST</sub>, the reset output(s) immediately go active and remain so until V<sub>CC</sub> rises above V<sub>RST</sub> and hysteresis, plus the defined t<sub>RFC</sub> period.

- Battery-low detection is an additional independent voltage monitoring function with a

dedicated battery-low detection output pin. It works as a pure comparator with

V<sub>RFF</sub>=1.25 V. STM6505 only.

- Fixed input logic levels are suitable for configurations where the device driving the input buttons (keyboard) is connected to a lower voltage than the supply voltage of the STM65xx device. This is in contrast to the devices with the standard CMOS input logic levels that are relative to V<sub>CC</sub> and are suitable only for applications in which the device driving the inputs of the Smart Reset™ device is powered by the same voltage supply.

# 2 Typical application diagrams

The STM65xx family of Smart Reset™ products provides a broad variety of options for various types of applications.

### 2.1 Single-button reset

The STM65xx devices allow for different reset input configurations. In simple applications, only one input reset button with delayed reset  $\underline{may}$  be sufficient. In this case, for product options without internal input pull-up resistors,  $\overline{SR0}$  and  $\overline{SR1}$  can be either connected together or the unused  $\overline{SR}$  input permanently grounded. In the case of a product version with internal input pull-up resistors, just connect the inputs together. Permanent grounding of the unused  $\overline{SR}$  input would, in this case, cause a continuous current to flow through the pull-up resistor from  $V_{CC}$  to  $V_{SS}$ .

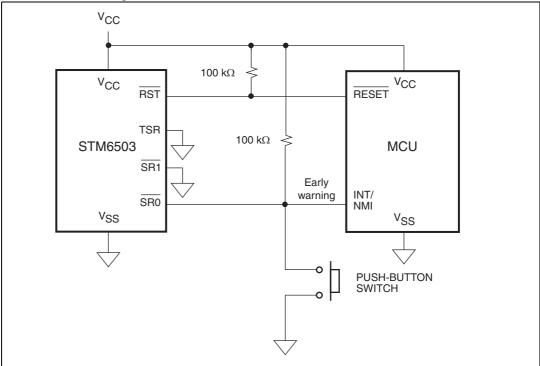

Figure 1. Single-button Smart Reset™ typical application diagram, with "early-warning" feature, STM6503

Early warning feature: the input reset push-button can be also used as an early warning to the processor (through the interrupt input) that a reset may come after the t<sub>SRC</sub> reset setup delay.

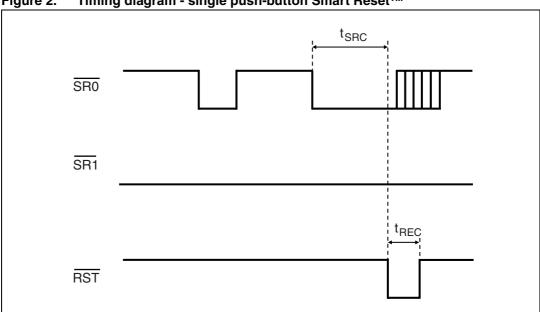

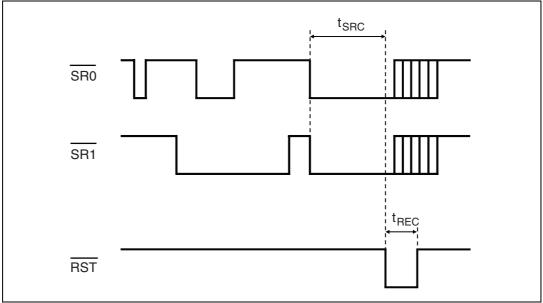

Figure 2. Timing diagram - single push-button Smart Reset™

### 2.2 Dual-button reset

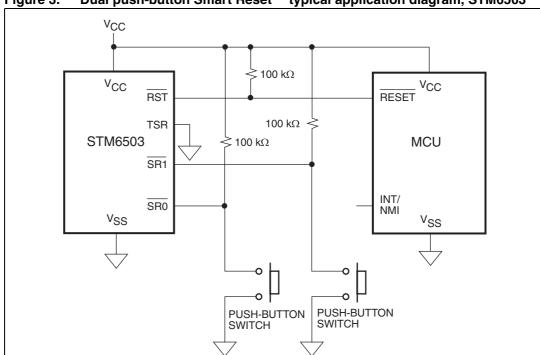

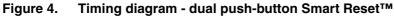

The most frequent application requires a configuration with two reset buttons which further improves immunity to undesired resets by adding a second input reset button with delayed reset. In this case, the reset pulse occurs only when both the buttons have been pressed and held for the defined t<sub>SRC</sub> delay.

Figure 3. Dual push-button Smart Reset™ typical application diagram, STM6503

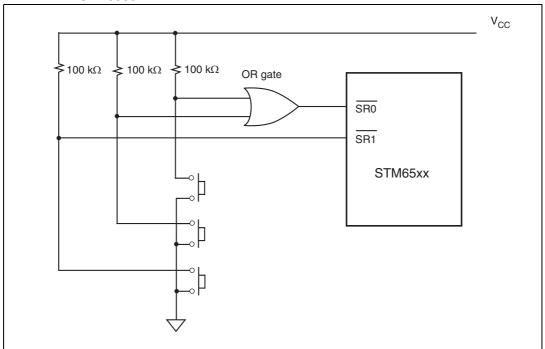

## 2.3 Multiple-button reset

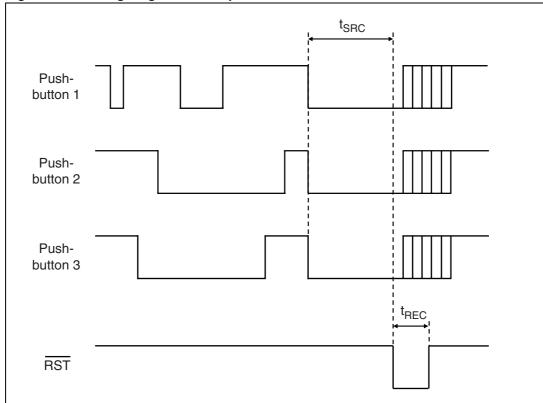

Adding even more input buttons is possible by adding a simple OR gate. All of the buttons must then be pressed simultaneously for at least  $t_{SRC}$  input delay seconds to get a reset pulse on the STM65xx output. For a configuration with three input reset buttons, connect one button to one  $\overline{SR}$  input as usual and the remaining two buttons to an OR gate and tie its output to the second  $\overline{SR}$  input.

Figure 5. Three push-button delayed Smart Reset™ typical application diagram, STM6503

Figure 6. Timing diagram - three push-button Smart Reset™

### 2.4 Input pull-up considerations (CMOS/fixed levels)

Inputs without internal pull-up resistors can be pulled to a different voltage level than the supply voltage of the STM65xx devices, however:

- the input pull-up voltage level should not exceed 5.5 V

- the input logic levels specifications must be respected:

- V<sub>IH</sub>min = 0.7V<sub>CC</sub>, V<sub>IL</sub>max = 0.3V<sub>CC</sub> in case of standard CMOS input cells (it is recommended to always keep V<sub>IL</sub> on the ground level and V<sub>IH</sub> on the V<sub>CC</sub> level)

- V<sub>IH</sub>min = 0.85 V, V<sub>IL</sub>max = 0.3 V in case of the fixed-logic levels devices (STM6520, STM6522).

# 2.5 Output pull-up considerations

Open-drain  $\overline{RST}$  outputs without internal pull-up resistors can also be pulled up to any voltage independent of  $V_{CC}$  (higher or lower than  $V_{CC}$ ) (but absolute maximum ratings must be respected). The STM65xx devices can thus serve also as a simple level shifter.

### 2.6 Reliability note

# Devices with timings adjusted by external components vs. environmental considerations

For device options with timings ( $t_{SRC}$ ,  $t_{REC}$ ) adjusted by an external capacitor, there are several additional factors to be considered that may affect the accuracy of the timings. The given specifications apply to the STM65xx device alone, i.e. with an ideal timing capacitor. External tolerances, temperature dependencies and leakages are excluded.

The Smart Reset<sup>TM</sup> devices are designed to meet strict requirements for the lowest possible current consumption and to maintain the common timing constant 10 s/ $\mu$ F, therefore the constant current used to charge the external timing capacitor is very low, in the magnitude of 100 nA. Any external leakage (e.g. poor quality timing capacitors or excessive humidity, especially if dew-point is exceeded and moisture condensation occurs on the PCB tracks) may cause a significant leakage current which is deducted from the constant charging current that the device provides, reducing the effective external timing capacitor charging current which results in extending the  $t_{SRC}$  ( $t_{REC}$ ) timings. To minimize this effect, the PCB tracks between the SRC (TREC<sub>ADJ</sub>) pin and its respective timing capacitor should be as short as possible, properly covered with solder mask and isolated from other tracks (especially  $v_{SS}$ ) by as great a distance as possible. Also, low-leakage timing capacitors (ceramic or film capacitor) should be used.

10/17 Doc ID 17837 Rev 1

## 3 Demonstration boards, promotion tools

A complete set of demonstration/promotion tools is available for various purposes, from easy, high-level application functional demonstration, down to tools for detailed testing. These tools are based on the STM6503 as the primary representative of the Smart Reset<sup>™</sup> family, as the basic Smart Reset<sup>™</sup> functionality is common.

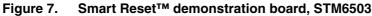

### 3.1 STM6503 demonstration board

#### **Purpose**

The demonstration board serves as a functional demonstration of the Smart Reset<sup>™</sup> devices and the easily accessible test points provide for basic measurements and testing.

- Simultaneous push of the SR0 and SR1 buttons is indicated by an LED

- LED and audible indication of the reset pulse after t<sub>SRC</sub> reset delay

- Test points available for easy tracking of the Smart Reset<sup>™</sup> signals

- Jumper-selectable Smart Reset<sup>™</sup> delay (2/6/10 seconds minimum)

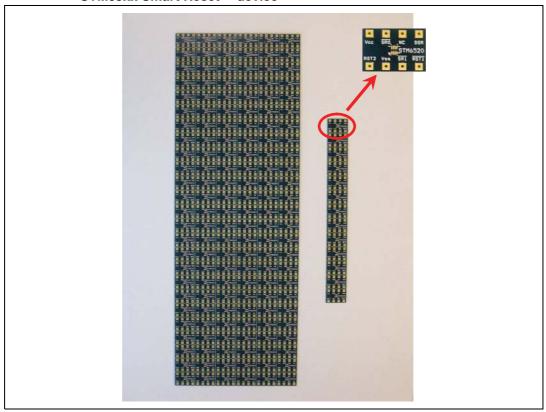

### 3.2 STM65xx interposer boards

### **Purpose**

The dedicated interposer PC boards were created for each STM65xx Smart Reset<sup>™</sup> device for a quick and flexible application/testing setup preparation. The boards include labels on each pin for easy identification. The pitch of the interposer pins easily fits into a breadboard and allows a very flexible application setup testing, or soldering wires for external connections (to a tester for example).

Figure 8. The STM65xx interposer boards; a dedicated board is available for each STM65xx Smart Reset™ device

12/17 Doc ID 17837 Rev 1

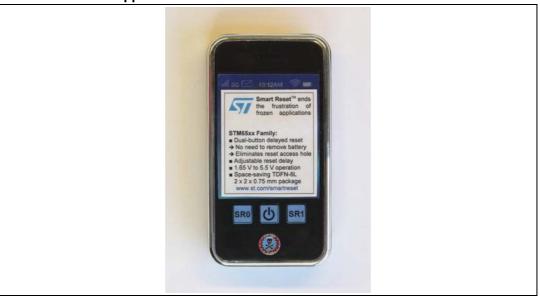

# 3.3 Smartphone demonstration example

### **Purpose**

The STM65xx smartphone demonstration shows the Smart Reset™ concept and functionality in a real application (dual push-button delayed reset):

Figure 9. Smartphone demonstration example shows STM6503 implemented in an actual application

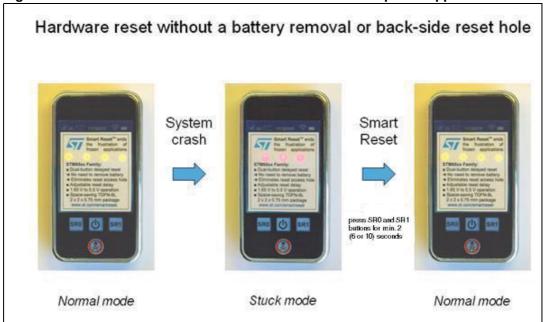

### Smart Reset<sup>™</sup> concept demonstration

- Push ON/OFF button → goes into a normal ON state (amber display backlight on)

- Push stuck button → goes into stuck mode that simulates frozen smartphone (red display backlight on) during which it cannot even be turned off

- Push SR0 and SR1 buttons simultaneously for 2 (6 or 10) seconds minimum (jumperselectable) → returns to the normal state from which it can be turned off by pressing the ON/OFF button

Figure 10. Smart Reset™ demonstration in an actual smartphone application

14/17 Doc ID 17837 Rev 1

AN3261 Conclusion

# 4 Conclusion

The family of Smart Reset<sup>™</sup> devices provides a variety of smartphone or PDA hardware reset solutions, some examples of which are shown in this application note, others are in the datasheet of the specific device. The most up-to-date information on the Smart Reset<sup>™</sup> portfolio can be found at <a href="https://www.st.com/smartreset">www.st.com/smartreset</a>.

Revision history AN3261

# 5 Revision history

Table 1. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 22-Sep-2010 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com