# AN3024 Application note

SPC560B4x/5x, SPC560C4x/5x, SPC560B54/6x, SPC560D30/40 hardware design guideline

#### Introduction

This application note complements the information in the device datasheet (see *Section A.1: Reference documents*) by describing requirements useful for a hardware implementation of the development board features such as power supply, reset control, clock management, boot mode setting, debug management and I/Os settings. It shows how to use the product and defines the minimum hardware resources required to start an application development.

Sections of this document describe certain device features in brief without describing the device blocks in detail. For a detailed description of these features, refer to the device datasheet, the reference manual or the errata sheet, or all three documents (see *Section A.1: Reference documents*).

This application note applies to the devices listed in *Table 1*.

Table 1. Device summary

| Reference  | Part number                           |

|------------|---------------------------------------|

| SPC560B4x  | SPC560B40L3, SPC560B40L5, SPC560B44L3 |

| SPC560B5x  | SPC560B50L3, SPC560B50L5, SPC560B50B2 |

| SPC560C4x  | SPC560C40L3, SPC560C44L3              |

| SPC560C50  | SPC560C50L3                           |

| SPC560B54x | SPC560B54L3, SPC560B54L5              |

| SPC560B60x | SPC560B60L3, SPC560B60L5, SPC560B60L7 |

| SPC560B64x | SPC560B64L5, SPC560B64L7              |

| SPC560D30x | SPC560D30L3                           |

| SPC560D40x | SPC560D40L1, SPC560D40L3              |

September 2013 Doc ID 16127 Rev 5 1/34

# **Contents**

| 1 | Pow  | ver supplies                                          | 6  |

|---|------|-------------------------------------------------------|----|

|   | 1.1  | Introduction                                          | 6  |

|   | 1.2  | Power supply scheme                                   | 7  |

|   | 1.3  | Current consumption and voltage regulator             | 7  |

|   | 1.4  | Layout recommendations                                | 8  |

| 2 | Rese | et                                                    | 9  |

|   | 2.1  | Introduction                                          | 9  |

|   | 2.2  | Power-on reset (POR) and low voltage detectors (LVDs) | 10 |

|   | 2.3  | System reset pin                                      | 10 |

|   |      | 2.3.1 Input characteristics                           | 11 |

|   |      | 2.3.2 Output characteristics                          | 11 |

|   | 2.4  | Reset scheme                                          | 11 |

| 3 | ADC  | · · · · · · · · · · · · · · · · · · ·                 | 13 |

|   | 3.1  | Introduction                                          | 13 |

|   | 3.2  | ADC performances optimization                         | 15 |

| 4 | Exte | ernal oscillators                                     | 16 |

|   | 4.1  | Introduction                                          | 16 |

|   | 4.2  | Fast external crystal oscillator (4 to 16 MHz)        | 16 |

|   | 4.3  | Slow external crystal oscillator (32 kHz)             |    |

|   |      | 4.3.1 Some recommended crystal                        |    |

|   | 4.4  | Layout recommendations                                | 17 |

| 5 | Boo  | t configuration                                       | 19 |

|   | 5.1  | Introduction                                          | 19 |

|   | 5.2  | Boot mode selection                                   | 19 |

|   | 5.3  | Boot pin scheme                                       | 20 |

| 6 | Deb  | ug                                                    | 21 |

|   | 6.1  | Introduction                                          |    |

|   | 6.2  | JTAG I/Os                                             |    |

|   |      |                                                       | _  |

|          | 6.3     | JTAG connector scheme               | 22 |

|----------|---------|-------------------------------------|----|

| 7        | I/Os .  |                                     | 23 |

|          | 7.1     | Introduction                        | 23 |

|          | 7.2     | I/O types                           | 23 |

|          | 7.3     | I/Os configuration after reset      | 23 |

|          | 7.4     | Maximum output current              | 24 |

|          | 7.5     | I/O characteristic in STANDBY mode  | 25 |

|          | 7.6     | General consideration for I/O       | 26 |

| 8        | EMC (   | guidelines                          | 27 |

|          | 8.1     | SPC560Bx/Dx software configurations | 27 |

|          | 8.2     | Hardware guidelines                 | 27 |

| 9        | Refere  | ence schematic                      | 29 |

| Appendix | A Do    | ocument management                  | 32 |

|          | A.1     | Reference documents                 | 32 |

|          | A.2     | Acronyms                            | 32 |

| Revision | history | y                                   | 33 |

List of tables AN3024

# List of tables

| Table 1. | Device summary                  | . 1 |

|----------|---------------------------------|-----|

| Table 2. | ADC module                      | 13  |

| Table 3. | Recomanded crystal              | 17  |

| Table 4. | Boot mode selection             | 20  |

| Table 5. | Debug features                  | 21  |

| Table 6. | I/O supply segment - SPC560B50x | 24  |

| Table 7. | I/O weight                      | 25  |

| Table 8. | Acronyms                        | 32  |

| Table 9. | Document revision history       | 33  |

5//

AN3024 List of figures

# **List of figures**

| Figure 1.  | Power supply overview                                | . 6 |

|------------|------------------------------------------------------|-----|

| Figure 2.  | Power supply scheme                                  | . 7 |

| Figure 3.  | Typical layout for VDD/VSS pair                      | . 8 |

| Figure 4.  | System reset and low power circuitry                 | 10  |

| Figure 5.  | Noise filtering on reset signal                      | 11  |

| Figure 6.  | Reference reset circuit                              | 12  |

| Figure 7.  | ADC input scheme                                     | 14  |

| Figure 8.  | Input equivalent circuit                             | 15  |

| Figure 9.  | Reference oscillator circuit                         | 16  |

| Figure 10. | Low power oscillator and resonator connection scheme | 17  |

| Figure 11. | Oscillator circuitry layout                          | 18  |

| Figure 12. | Boot mode selection                                  | 19  |

| Figure 13. | Boot mode selection implementation example           | 20  |

| Figure 14. | JTAG connector scheme                                | 22  |

| Figure 15. | Typical application schematic of SPC560B40x-LQFP144  | 29  |

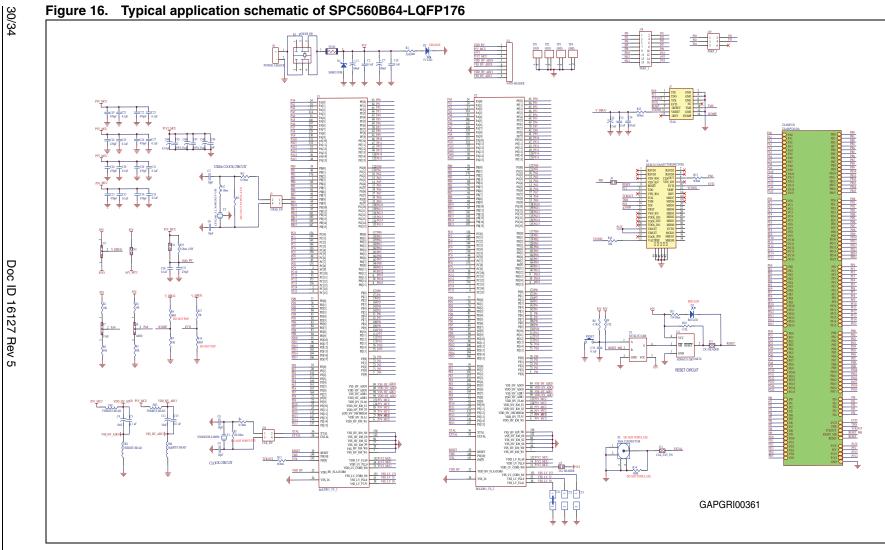

| Figure 16. | Typical application schematic of SPC560B64-LQFP176   | 30  |

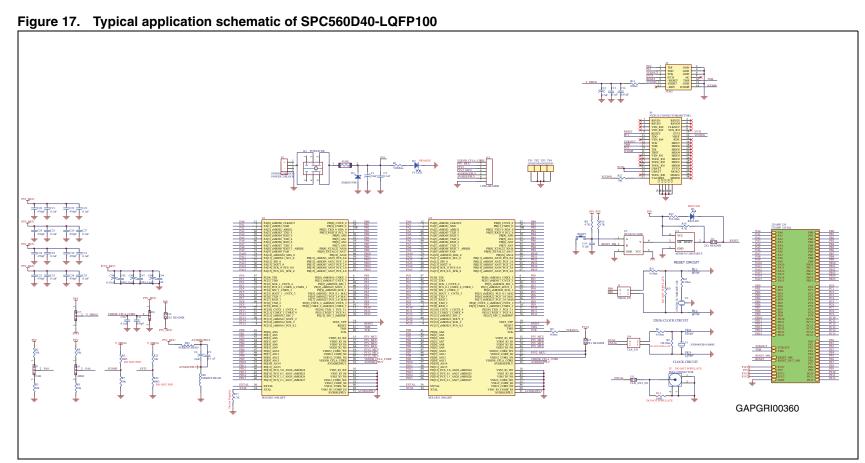

| Figure 17. | Typical application schematic of SPC560D40-LQFP100   | 31  |

Power supplies AN3024

# 1 Power supplies

#### 1.1 Introduction

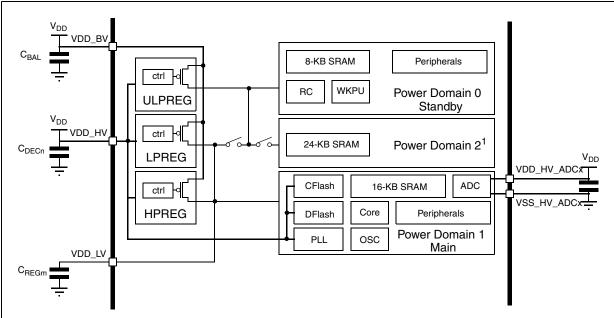

The device requires a 3.3 V or 5.0 V operating voltage supply (high voltage). An embedded regulator is used to supply the internal 1.2 V digital power (low voltage).

Three different high voltage pin supply types are used:

- VDD\_HV—high voltage external power supply for internal voltage regulators, I/O pins and Flash

- VDD\_BV—high voltage external power supply for internal voltage regulator ballast transistors

- VDD\_HV\_ADCx—high voltage external power supply for each analog-to-digital converter

Three different independent voltage regulators provide the 1.2 V digital power supply:

- HPREG—high power internal voltage regulator used during normal operations. It can be switched off in STOP mode and is automatically switched off in STANDBY mode.

- LPREG—low power internal voltage regulator used when HPREG is off. It can be switched off in STOP mode and is automatically switched off in STANDBY mode.

- ULPREG—ultra low power internal voltage regulator. Always switched on and used in STANDBY or in STOP mode when all other regulators are switched off.

External capacitors connected between the VDD\_LV/VSS\_LV pin pairs ensure the stability of the internal 1.2 V HPREG and LPREG regulators.

Figure 1. Power supply overview

1. PD2 is not developed in SPC560D30x/40x devices.

AN3024 Power supplies

For a detailed list of supply-related pins for all packages, please refer to the voltage supply pins section in device reference manual (see *Section A.1: Reference documents*).

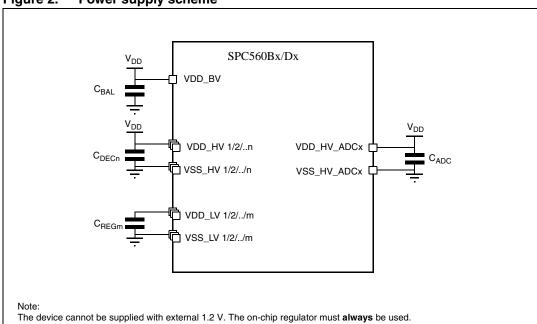

# 1.2 Power supply scheme

The circuit is powered by a stabilized power supply V<sub>DD</sub>.

- VDD\_HV pins must be connected to V<sub>DD</sub> with external decoupling capacitors C<sub>DECn</sub>.

- VDD\_BV pin must be connected to V<sub>DD</sub> with external decoupling capacitor C<sub>BAI</sub>.

- VDD\_HV\_ADC pin be connected to VDD with external decoupling capacitor CADC.

- VDD\_LV pins must be connected with external decoupling capacitors C<sub>REGm</sub> placed as close as possible to the device pins.

- VSS\_HV and VSS\_LV pins must all be connected together to GND.

Refer to the voltage regulator electrical characteristics section in the device datasheet (see *Section A.1: Reference documents*) for exact capacitor values.

Figure 2. Power supply scheme

Caution:

All BV and HV and ADCx supplies must be powered with a voltage level in the range  $V_{DD}\pm0.1$  V, and all grounds must be in the range  $V_{SS}\pm0.1$  V.

# 1.3 Current consumption and voltage regulator

In order to select a suitable external voltage regulator and design a supply circuit, the designer of the application must consider:

- The maximum consumption in steady state

- 2. The maximum inrush current during device start-up

Power supplies AN3024

The maximum consumption in steady state depends on the frequency of the CPU, the usage of the peripheral and the current drawn by the outputs. It can be estimated by referring to the device datasheet (see *Section A.1: Reference documents*).

The inrush current required by the device during power-on reset or exit from STANDBY is clamped at 300 mA and lasts for few microseconds (maximum 20  $\mu$ s) until the C<sub>REGm</sub> stabilization capacitors (total value ~1  $\mu$ F) are charged. This current is drawn from the VDD\_BV pin.

Note:

The inrush current must be considered to dimension the decoupling capacitance of the ballast (C\_DEC1) value as during this inrush the application must ensure  $V_{DD}$  remains in the voltage range of the application (5 V or 3.3 V  $\pm$ 10 %). The steady current is used to define the voltage regulator capability of the application.

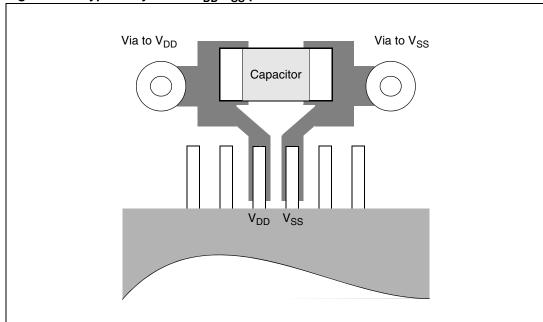

## 1.4 Layout recommendations

All the supply connections, including pads, tracks and vias, must have impedance as low as possible (less than 5 nH). This is typically achieved by using thick and wide Cu tracks and preferably dedicated power supply planes in multilayer PCBs.

Moreover, it is recommended to use both low equivalent series resistance (ESR) and low equivalent series inductance (ESL) capacitors. The capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB. *Figure 3* shows the typical layout of such a  $V_{DD}/V_{SS}$  pair.

Figure 3. Typical layout for  $V_{DD}/V_{SS}$  pair

AN3024 Reset

#### 2 Reset

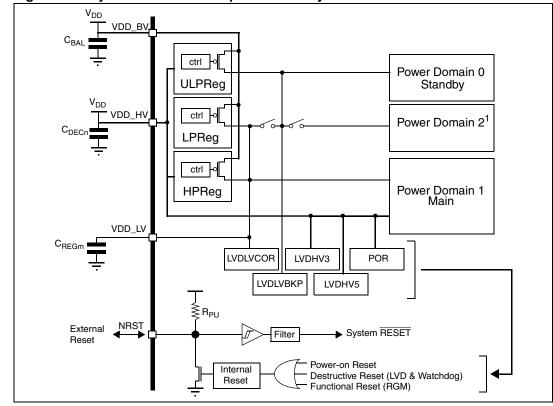

#### 2.1 Introduction

The device has an integrated POR (power-on reset) to ensure a correct power-up sequence: The device remains in reset state as long as the  $V_{DD}$  is below the specified threshold.

The device has four low voltage detectors to monitor  $V_{DD\ HV}$  and  $V_{DD\ LV}$ :

- LVDHV3—monitors V<sub>DD</sub> so as to ensure that the device reset occurs for voltage values less than minimum functional supply value

- LVDHV5—monitors V<sub>DD</sub> when the application uses devices operating in the range 5.0 V ± 10%. By default the LVDHV5 is disabled (to allow 3.3 V operation) and must be activated by the application.

- LVDLVCOR—monitors the voltage provided to the main power domain (core, Flash, PLL, JTAG and peripherals not included in the standby power domain)

- LVDLVBKP—monitors the voltage provided to the power domain in standby mode (8 Kbyte SRAM, optionally 24 Kbyte SRAM, power control unit, reset generation module, voltage regulator, wake-up unit, API, CAN sampler, internal RC oscillators, etc.)

The device has a dedicated bidirectional RESET pin (NRST) with Schmitt-Trigger characteristics and noise filter for system reset.

For detailed information on reset sequence, please refer to the reset state machine section in device reference manual (see *Section A.1: Reference documents*).

Reset AN3024

Figure 4. System reset and low power circuitry

1. PD2 is not developed in SPC560D30/40 devices.

# 2.2 Power-on reset (POR) and low voltage detectors (LVDs)

POR is required to initialize the chip during power-up and works only on the rising edge of the VDD\_HV supply. It is asserted when  $V_{DD\_HV}$  is above  $V_{PORUPmin}$  and released when  $V_{DD\_HV}$  is above  $V_{PORH}$ .

Once the POR is released, power management modules, including internal LVDs, are up and running. The system remains in reset state until the LVDHV3, LVDLVCOR and LVDLVBKP thresholds are reached.

Note:

At power-up, although the  $V_{DD}$  slope at the VDD\_HV pad rises, it must remain in the range of 3 V/s to 0.25 V/µs (see  $T_{VDD}$  parameter in the device datasheet—refer to Section A.1: Reference documents).

# 2.3 System reset pin

The device implements a dedicated bidirectional RESET pin (NRST) with Schmitt-Trigger characteristics and noise filter.

10/34 Doc ID 16127 Rev 5

AN3024 Reset

#### 2.3.1 Input characteristics

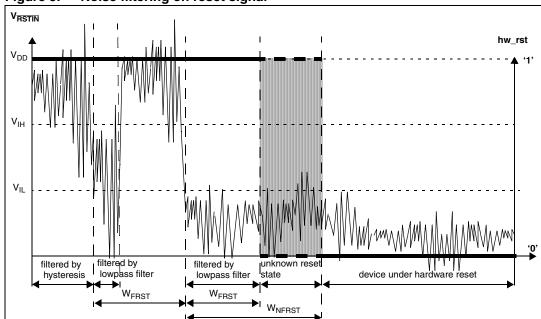

The external reset signal (pulse) on the NRST pin must be greater than  $W_{NFRST}$  (500 ns). Pulses less than  $W_{FRST}$  (50 ns) are ignored. Any pulse between  $W_{FRST}$  and  $W_{NFRST}$  may or may not generate an internal reset.

A noise applied on the reset signal might wrongly put the device in reset. In order to avoid unexpected reset of the device, the NRST pad includes an analog filter which makes the system immune to noise.

For additional information about filter characteristics, please refer to the nRSTIN electrical characteristics section in the device datasheet (see *Section A.1: Reference documents*).

Figure 5. Noise filtering on reset signal

## 2.3.2 Output characteristics

The NRST pad, when used as output, behaves as a MEDIUM pad (see the nRSTIN electrical characteristics section in the device datasheet—refer to *Section A.1: Reference documents*).

The duration of the NRST active time depends on the reset source and the device configuration, but the minimum reset duration guaranteed is  $80 \, \mu s$ .

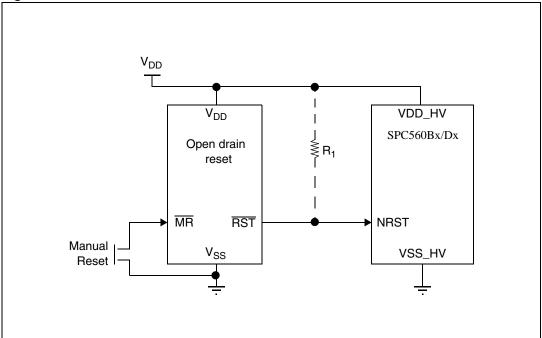

#### 2.4 Reset scheme

*Figure 6* shows a typical circuit for controlling the NRST pin operation. The reset input pin has an internal weak pull-up configured by default exiting from power-on, thus R<sub>1</sub> can be omitted. In the case in which an external capacitor is used to filter the NRST external signal, an external pull-up reduces the charging time of this capacitor.

Reset AN3024

Figure 6. Reference reset circuit

AN3024 ADC

## 3 ADC

#### 3.1 Introduction

Table 2 shows ADC module present in the devices.

Table 2. ADC module

| Devices                       | ADC0 10-bit | ADC1 12-bit |

|-------------------------------|-------------|-------------|

| SPC560B4x/5x,<br>SPC560C4x/5x | 1           | 0           |

| SPC560B54/6x                  | 1           | 1           |

| SPC560D30x/40x                | 0           | 1           |

The device uses a dedicated supply pair VDD\_HV\_ADC/VSS\_HV\_ADC for each ADC analog module so as to decouple the ADC reference voltage from the noise generated either by another part of the device or by the external application components. VDD\_HV\_ADC must be at the same voltage level as the VDD\_HV.

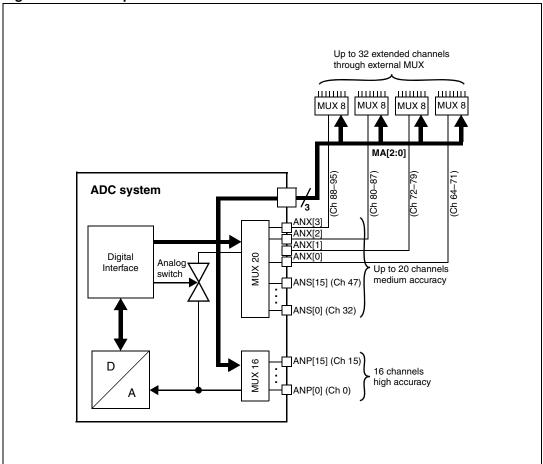

There are three different ADC input channels types:

- ANP—internal multiplexed precise channels used for conversion requiring a low TUE

- ANS—internal multiplexed standard channels used for conversion requiring a standard TUE

- ANX—external multiplexed channels used in conjunction with external multiplexer controlled directly by the device

ANPs are input only pins. For channel characteristics, please refer to the ADC electrical characteristics section in the device datasheet (see *Section A.1: Reference documents*).

ADC AN3024

Figure 7. ADC input scheme

AN3024 ADC

## 3.2 ADC performances optimization

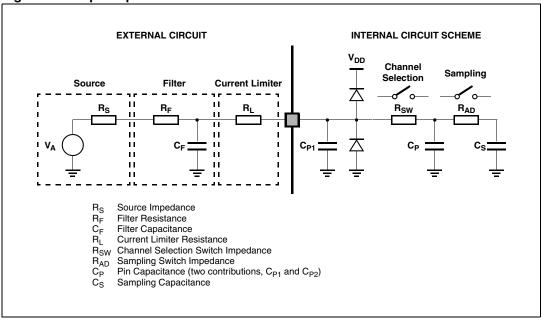

The equivalent analog input interface for both 10-bit and 12-bit ADC channel is shown in *Figure 8*.

Figure 8. Input equivalent circuit

To minimize the error induced by the voltage partitioning between this resistance (sampled voltage on  $C_S$ ) and the sum of  $R_S + R_F + R_L + R_{SW} + R_{AD}$ , the external circuit must be designed to respect the *Equation 1*:

#### **Equation 1**

$$V_{A} \bullet \frac{R_S + R_F + R_L + R_{SW} + R_{AD}}{R_{FO}} < \frac{1}{2} LSB$$

Please refer to the analog-to-digital converter (ADC) chapter in device reference manual or type specification versus pins and to the ADC electrical characteristics section in the device datasheet for parameter values (see *Section A.1: Reference documents*).

External oscillators AN3024

#### 4 External oscillators

#### 4.1 Introduction

The product offers four clock sources to cover the various types of application:

- Fast internal RC oscillator

- Fast external crystal oscillator

- Slow internal RC oscillator

- Slow external crystal oscillator

An internal PLL is available to optimize the oscillator choice versus the required system frequency.

This section is focused on the two external oscillators:

- The fast external crystal oscillator for the system clock covering 4 MHz to 16 MHz

- The slow external crystal oscillator for the 32 kHz low power clock

# 4.2 Fast external crystal oscillator (4 to 16 MHz)

The fast external crystal oscillator must be in the frequency range from 4 MHz to 16 MHz. If the crystal (resonator) is in the range from 4 MHz to 8 MHz, the oscillator margin can be adjusted by using an option bit which reduces the fast external crystal oscillator consumption (low consumption configuration). The default manufacturing oscillator margin is in the range from 4 MHz to 16 MHz.

Please refer to the device reference manual (see Section A.1: Reference documents) for additional information about option bits and oscillator margin.

To reduce EMC emissions, it is recommended to use the slowest crystal (resonator) together with the internal PLL, thus achieving the proper system operating frequency. The drawback of using a slow crystal is the longer start-up time.

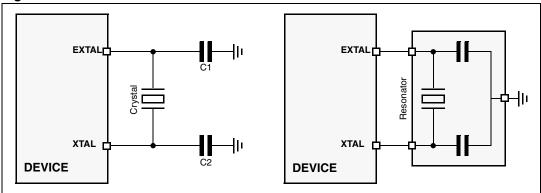

Figure 9 shows the external circuit needed for using the oscillator with a crystal or a resonator.

Figure 9. Reference oscillator circuit

For additional information, please refer to the fast external crystal oscillator (4 to 16 MHz) electrical characteristics section in the device datasheet (see *Section A.1: Reference documents*).

16/34 Doc ID 16127 Rev 5

AN3024 External oscillators

# 4.3 Slow external crystal oscillator (32 kHz)<sup>(a)</sup>

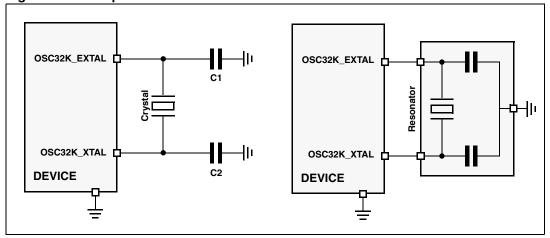

*Figure 10* shows the external circuit needed for using the low power oscillator with a 32 kHz crystal.

Figure 10. Low power oscillator and resonator connection scheme

For additional information, please refer to the slow external crystal oscillator (32 kHz) electrical characteristics section in the device datasheet (see *Section A.1: Reference documents*).

#### 4.3.1 Some recommended crystal

*Table 3* gives the references of recommended crystals certified by resonators suppliers and verified through designer simulation in addition to the ones listed in the DS..

Table 3. Recomanded crystal

| Part number     | Family name | Freq. | CL   | Supplier |

|-----------------|-------------|-------|------|----------|

| EXS00A-MU00265  | NX3215SA    | 32kHz | 15pF | NDK      |

| 1TJF0SPFP1AC00E | DST310S     | 32kHz | 15pF | KDS      |

However it is suggested to perform matching directly on customer application board, in order to verify board parassitics.

# 4.4 Layout recommendations

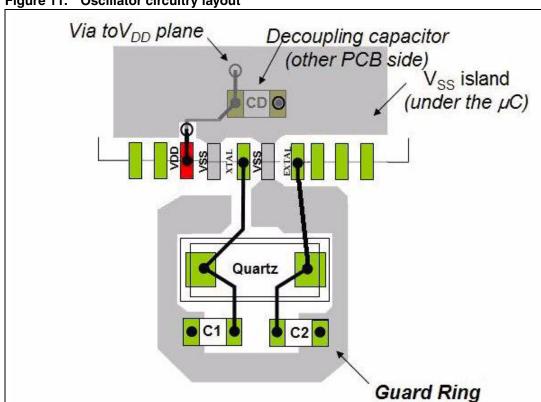

The following recommendations should be observed for designing the oscillator circuitry layout:

A current flow at the crystal fundamental frequency runs through the oscillator circuit. If the oscillator is clipped, then the higher order harmonics are present. To minimize the emissions generated by these currents, the oscillator circuit should be kept as compact as possible.

a. 32 KHz external oscillator is not developed on SPC560D30x/40x device

AN3024 **External oscillators**

> VSS\_HV should be connected directly to GND (VSS island) so that return currents can flow easily between VSS\_HV and the two capacitors (C<sub>1</sub> and C<sub>2</sub>).

- Avoid other high frequency signals near the oscillator circuitry.

- Use the same GND for oscillator and oscillator driver (VSS\_HV is between EXTAL and XTAL, V<sub>SS</sub> island)

- Layout: configure the GND supply at low impedance.

- Shield the crystal with an additional ground plane underneath the crystal.

- Do not place sensitive signals near the oscillator. Analyze cross-talk between different layers.

- The VSS pins close to the XTAL pin must be connected to GND plane (V<sub>SS</sub> island) and decoupled from the closest VDD pin.

- Capacitors are placed between both ends of the crystal and GND (guard ring). The ring must be as small as possible.

- If the crystal package is metallic, it should be connected directly to GND.

- For isolating the noise from or to a particular area of the PCB, it is possible to surround this area with a "guard ring."

Figure 11 shows an example of an oscillator circuitry layout.

Figure 11. Oscillator circuitry layout

AN3024 Boot configuration

# 5 Boot configuration

#### 5.1 Introduction

The boot of the device is managed by the boot assist module (BAM).

The following boot modes are supported:

- Single chip (SC)—The device boots from the first bootable section of the Flash main array.

- Serial boot (SBL)—The device downloads boot code from either LINFlex\_0 or FlexCAN\_0 interface and executes it.

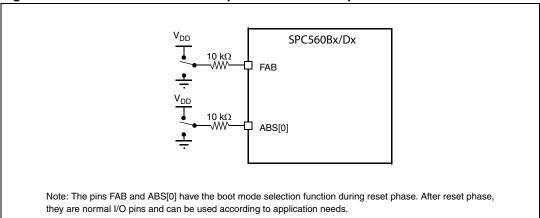

The boot mode selection is obtained by setting two pins: FAB and ABS[0].

## 5.2 Boot mode selection

The device detects the boot mode based on external pins (FAB and ABS[0]) and device status. *Figure 12* shows the boot sequence.

**POR** Serial Boot (SBL) ABS=0 FABM = 1 ABS = ?LINFlex Serial Boot (SBL) Ń ABS=1 FlexCAN Flash Boot-ID Flash Boot from in any boot sector? lowest sector no Boot-ID Static Mode GAPGRI00205

Figure 12. Boot mode selection

In *Figure 12*, the grey blocks represent hardware-implemented functions, while the white ones are software-implemented functions in ROM memory.

Boot configuration AN3024

To boot either from FlexCAN\_0 or LINFlex\_0, the device must be forced into an alternate boot loader mode via FAB pin (pad PA[9]). The type of alternate boot mode (CAN or LIN) is selected according to the ABS[0] pin (pad PA[8]).

FAB and ABS[0] pins must be forced in the required state before initiating the reset sequence.

| able ii Boot iiida coloctoii |                       |           |             |  |  |  |  |  |  |

|------------------------------|-----------------------|-----------|-------------|--|--|--|--|--|--|

| FAB<br>(pad PA[9])           | ABS[0]<br>(pad PA[8]) | Boot ID   | Boot mode   |  |  |  |  |  |  |

| 1                            | 0                     | Х         | LINFlex_0   |  |  |  |  |  |  |

| 1                            | 1                     | Х         | FlexCAN_0   |  |  |  |  |  |  |

| 0                            | X                     | Valid     | Single chip |  |  |  |  |  |  |

| 0                            | Х                     | Not valid | Static mode |  |  |  |  |  |  |

Table 4. Boot mode selection

In single-chip mode, hardware searches the Flash boot sector for a valid boot ID. As soon as the device detects a bootable sector, it reads the 32-bit word at offset 0x4 at the detected sector. Single-chip mode is managed by hardware and BAM is not used.

BAM is executed only in the following cases:

- Serial boot mode has been selected by FAB pin.

- Hardware has not found a valid Boot-ID in any Flash boot locations.

If booting is not possible with the selected configuration (for example, if no Boot ID is found in the selected boot location) then the device enters the static mode.

Please refer to the boot assist module (BAM) chapter in device reference manual (see *Section A.1: Reference documents*) for additional information.

# 5.3 Boot pin scheme

To make all boot configurations possible, it is recommended to use external switches connected to the FAB and ABS[0] pins, as shown in *Figure 13*.

Figure 13. Boot mode selection implementation example

GAPGRI00206

20/34 Doc ID 16127 Rev 5

AN3024 Debug

# 6 Debug

#### 6.1 Introduction

*Table 5* shows debug features of the devices.

Table 5. Debug features

| Devices                    | JTAG | Nexus2+            |

|----------------------------|------|--------------------|

| SPC560B4x/5x, SPC560C4x/5x | Yes  | Yes <sup>(1)</sup> |

| SPC560B54/6x               | Yes  | Yes <sup>(1)</sup> |

| SPC560D30x/40x             | Yes  | No                 |

<sup>1.</sup> Only on the LBGA208 development package.

Nexus2+ is not discussed in this document.

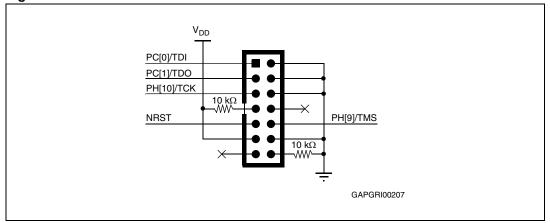

#### 6.2 JTAG I/Os

The JTAG interface is composed of:

- Test data input (TDI) on pin PC[0]

- Test data output (TDO) on pin PC[1]

- Test mode select (TMS) on pin PH[10]

- Test clock input (TCK) on pin PH[9]

Out of reset, all JTAG signals are configured for the JTAG communication. They can be configured by software as user I/Os and made available to the application. If the application needs to combine both the JTAG functionality for debug and programming purposes together with the standard I/O function, some limitations must be considered:

- PC[0], PC[1], PH[9] and PH[10] cannot be debugged using a JTAG debug interface.

- The configuration of PC[0], PC[1], PH[9] or PH[10] as user I/Os prevents the communication with the debugger, making impossible to debug the application.

- These pins can only be set back to the JTAG functionality by means of a hardware or software reset (it cannot be done through the JTAG debugger).

An external hardware application connected to those signals might interfere with JTAG signals, making it impossible to enter debug mode without disconnecting the external hardware. It is preferable to use these JTAG pins to define the hardware configuration of the application rather than critical application functions.

Debug AN3024

# 6.3 JTAG connector scheme

Figure 14. JTAG connector scheme

AN3024 I/Os

#### 7 I/Os

#### 7.1 Introduction

The device features a unique pad technology to sustain a current injection of IINJPAD (refer to device datasheet, *Section A.1: Reference documents*) on digital and analog inputs. A simple serial resistor is sufficient to protect the input characteristics.

# **7.2** I/O types

The device features three I/O types with different drive strength:

- SLOW type—This is the most common output type suitable for most of the application output signals and ensuring low electromagnetic emission.

It allows to drive up to 2 mA and can sustain a maximum frequency of 2 MHz.

- MEDIUM type—This output type can sustain a higher frequency with a reduced delay to meet the requirements of SPI communication or high speed CAN communication. It allows to drive up to 3.8 mA and can sustain a maximum frequency of 16 MHz. Out of reset, the medium speed outputs are configured as slow. To obtain the medium performance the application must configure the slew rate using the SRC field in the corresponding SIUL pad configuration register (SIUL\_PCR).

- FAST type—Only the Nexus MCKO signal features a fast pad which is not a user signal.

Maximum output frequency depends directly on the capacitive load connected on the output.

Please refer to the device datasheet and Reference manual (see *Section A.1: Reference documents*), for the detailed electrical characteristics and port mapping.

Note: 1 All output types have a slope control (current) to reduce the EMI.

2 TDO pad is medium speed only. Writing the SRC field in the corresponding SIUL\_PCR has no effect.

# 7.3 I/Os configuration after reset

To avoid activating external components while under reset, all pads are forced to high impedance inputs, with the following exceptions:

- RESET is driven low

- Boot mode pins

- FAB is pull-down

- ABS[0] is pull-up

- JTAG pins

- TCK, TMS and TDI are pull-up

- TDO is high impedance

I/Os AN3024

#### 7.4 Maximum output current

The application must not modify the maximum current drive expected on each I/O type and I/O segment. An I/O segment is a group of pads supplied by the same  $V_{DD\ HV}/V_{SS\ HV}$  pair.

Table 6. I/O supply segment - SPC560B50x

| Package                | Supply segment                                               |             |               |              |   |   |  |  |  |

|------------------------|--------------------------------------------------------------|-------------|---------------|--------------|---|---|--|--|--|

| rackage                | 1                                                            | 2           | 3             | 4            | 5 | 6 |  |  |  |

| LBGA208 <sup>(1)</sup> | Equivalent to LQFP144 segment pad distribution MCKO MDOn/MSE |             |               |              |   |   |  |  |  |

| LQFP144                | pin20-pin49                                                  | pin51-pin99 | pin100-pin122 | pin123-pin19 | _ | _ |  |  |  |

| LQFP100                | pin16-pin35                                                  | pin37-pin69 | pin70-pin83   | pin84-pin15  | _ | _ |  |  |  |

<sup>1.</sup> LBGA208 available only as development package for Nexus2+.

In order to keep the maximum current on each segment in specification, both static and dynamic consumptions must be considered:

- The maximum static current must remain below maximum I<sub>AVGSEG</sub> value so as to ensure device reliability. The parameter I<sub>AVGSEG</sub> represents the average current drawn by all outputs belonging to the same segment. For example, if V<sub>DD</sub> = 5 V then I<sub>AVGSEG</sub> = 70 mA.

- So, for example, if a body application uses loads that totally draw more than 70mA, these loads should be distributed over more than one segment.

- The maximum dynamic current must guarantee that the sum of the weight of concurrent (per clock cycle) switching I/Os on a single segment should remain below the 100%. For example, consider I/O's weight in *Table 7* related to segment 4 on SPC560B40x device. Suppose we use the following concurrent switching I/Os for LQFP144 package: PB3, PC9, PC14, PC15, PG5, PG4, PG3, PG2, PA2, PE0, PA1 if the pads are configured as slow (SRC=0), device functionality is guaranteed in case of V<sub>DD</sub>=5 V (sum of weights=96%) but not for V<sub>DD</sub>=3.3 V (sum of weights=114%)

AN3024 I/Os

Table 7. I/O weight<sup>(1)</sup>

| Supply segment |             |            | LQFP144/LQFP100 |                        |              | LQFP64 <sup>(2)</sup> |            |         |              |         |         |

|----------------|-------------|------------|-----------------|------------------------|--------------|-----------------------|------------|---------|--------------|---------|---------|

|                |             | Pad        | Weight 5 V      |                        | Weight 3.3 V |                       | Weight 5 V |         | Weight 3.3 V |         |         |

| LQFP<br>144    | LQFP<br>100 | LQFP<br>64 |                 | SRC <sup>(3)</sup> = 0 | SRC = 1      | SRC = 0               | SRC = 1    | SRC = 0 | SRC = 1      | SRC = 0 | SRC = 1 |

|                |             | 3          | PB[3]           | 10%                    | _            | 12%                   | _          | 10%     | _            | 12%     | _       |

|                | 4           | 3          | PC[9]           | 10%                    | _            | 12%                   | _          | 10%     | _            | 12%     | _       |

|                | 4           | _          | PC[14]          | 9%                     | _            | 11%                   | _          | _       | _            | _       | _       |

| 4              |             | _          | PC[15]          | 9%                     | 13%          | 11%                   | 12%        | _       | _            | _       |         |

|                | _           | _          | PG[5]           | 9%                     | _            | 11%                   | _          | _       | _            | _       | _       |

|                | _           | _          | PG[4]           | 9%                     | 12%          | 10%                   | 11%        | _       | _            | _       | _       |

|                | _           | _          | PG[3]           | 9%                     | _            | 10%                   | _          | _       | _            | _       | _       |

|                | _           | _          | PG[2]           | 8%                     | 12%          | 10%                   | 10%        | _       | _            | _       | _       |

|                |             | 3          | PA[2]           | 8%                     | _            | 9%                    | _          | 8%      | _            | 9%      | _       |

|                |             | _          | PE[0]           | 8%                     | _            | 9%                    | _          | _       | _            | _       | _       |

|                |             | 3          | PA[1]           | 7%                     | _            | 9%                    | _          | 7%      | _            | 9%      | _       |

| 4              |             | _          | PE[1]           | 7%                     | 10%          | 8%                    | 9%         | _       | _            | _       | _       |

| 4              | 4           | _          | PE[8]           | 7%                     | 9%           | 8%                    | 8%         | _       | _            | _       | _       |

|                |             | _          | PE[9]           | 6%                     | _            | 7%                    | _          | _       | _            | _       | _       |

|                |             | _          | PE[10]          | 6%                     | _            | 7%                    | _          | _       | _            | _       | _       |

|                |             | 3          | PA[0]           | 5%                     | 8%           | 6%                    | 7%         | 5%      | 8%           | 6%      | 7%      |

|                |             | _          | PE[11]          | 5%                     | _            | 6%                    | _          | _       | _            |         | _       |

- 1.  $V_{DD}$  = 3.3 V ± 10% / 5.0 V ± 10%,  $T_A$  = -40 to125 °C, unless otherwise specified.

- 2. All LQFP64 information is indicative and must be confirmed during silicon validation.

- 3. SRC: "Slew Rate Control" bit in SIU\_PCR.

Please refer to the I/O pad current specification section in the device datasheet and device reference manual (see *Section A.1: Reference documents*) for the detailed electrical characteristics and port mapping.

The dynamic consumption is caused by the output driver transistors during the output switch and therefore is present only during the transition phase of the output (rising or falling edge).

## 7.5 I/O characteristic in STANDBY mode

In STANDBY mode the I/Os are disconnected from supply and they are in high impedance state. Only the wake-up lines can be configured as:

- High-impedance input (default configuration)

- Input with weak pull-up

I/Os AN3024

The configuration of the wake-up lines is supported in the wake-up unit. Please refer to the wakeup unit (WKPU) chapter in reference manual (see *Section A.1: Reference documents*) for additional information.

Note:

All wake-up lines left floating cause additional consumption due to their Schmitt Trigger logic. To avoid unnecessary consumption all wake-up lines should be kept to  $V_{SS}$  or  $V_{DD}$  either by the application or using the internal weak pull-up.

The TDO pad is part of the STANDBY domain in order to provide a handshaking mechanism with a debugger in STANDBY mode. However, in STANDBY mode the TDO pin is configured as input without pull-resistor and as a consequence, when no debugger is connected, the TDO pad is floating causing additional current consumption.

In order to avoid additional consumption, TDO must be tied to  $V_{DD}$  or GND by means of an external pull-up (or pull-down) resistor in the range of 47–100 k $\Omega$ .

If the PA[1] pin is configured as NMI the pull-up is automatically activated, but this has no effect during STANDBY mode. In this case pull-up is then correctly configured through the WKPU\_WIPUER register; no external resistor is necessary.

#### 7.6 General consideration for I/O

To avoid excess consumption and to improve the reliability of the application it is recommended to configure unused I/Os as input with pull-up.

During the application design the absolute maximum voltage on I/O must be considered:

- respect to ground: +6 V

- respect to  $V_{DD}$ : Voltage of each pin must remain in the range from  $V_{DD}$  0.3 and  $V_{DD}$  + 0.3

For more details refer to the device datasheet (see Section A.1: Reference documents).

AN3024 EMC guidelines

# 8 EMC guidelines

This section summarizes recommendations for the system designers to improve the EMC (electromagnetic compatibility) and, in particular, to reduce the radiant emissions of a system based on the SPC560Bx/Dx devices.

Obviously, not all EMC techniques are covered. Therefore, it is recommended to refer to other, more general EMC documentation in parallel to the present application note.

# 8.1 SPC560Bx/Dx software configurations

The SPC560Bx/Dx family offers some features that allow, with software configurations, to cover some requests for reduction in the electromagnetic interference (or EMI) emissions:

- The system clock should be chosen to avoid overlapping with known frequency (bands of interest)

- The FMPLL gives the possibility to modulate the system clock so to reduce the picks of emission.

- Choose the lowest possible slew rate of pins accordantly with the functionality choose for the pins

- The peripherals that are not used in the application should be disabled and clock gated

- Configuring the unused pins as input weak pull-up (default configuration)

# 8.2 Hardware guidelines

Some recommendations to design a system layout are listed below:

V<sub>DD</sub> decoupling capacitors

Decoupling capacitors must be used to decouple BV and all HV and ADC supply pins from GND. To avoid that the decoupling capacitors' parasitic inductance couples with the capacitance plane of the supply planes, certain measures of precaution should be taken:

- Place the capacitors as close as possible to the V<sub>DD</sub> pins on the SPC560Bx/Dx device.

- Use power planes or wide traces to connect from the SPC560Bx/Dx device to the capacitor.

- Use as many vias as possible in the connections from the SPC560Bx/Dx device to the capacitors. For example, use at least two vias to connect the positive side of the capacitor to the power plane.

- Fast external crystal oscillator

To reduce EMC emissions, it is recommended to use the slowest crystal (resonator) together with the internal PLL, thus achieving the proper system operating frequency. The drawback of using a slow crystal is the longer startup time. In order to minimize the amount of emissions, generated from the currents flowing in the oscillator circuit at the crystal's fundamental frequency, the oscillator circuit should be kept as compact as possible.

EMC guidelines AN3024

#### Grounding

Usually in a system it is possible identify different parts of circuits including digital, analog, high current switching circuitry, I/O, and the main power supply. If these different parts of the circuit use isolated grounds, they will be connected together at a single point.

#### PCB considerations:

- For single-chip applications, a minimum of four layers is used. For expanded mode applications, a minimum of six layers is used.

- There is at least one ground plane.

- There is at least one power plane.

- From the power and ground planes have not be present structures which obstruct the flow of current, such as via overlapping (it is not allowed three via anti-pads to merged). Furthermore, vias should be staggered as much as possible because aligned vias create slots that obstruct the flow of current.

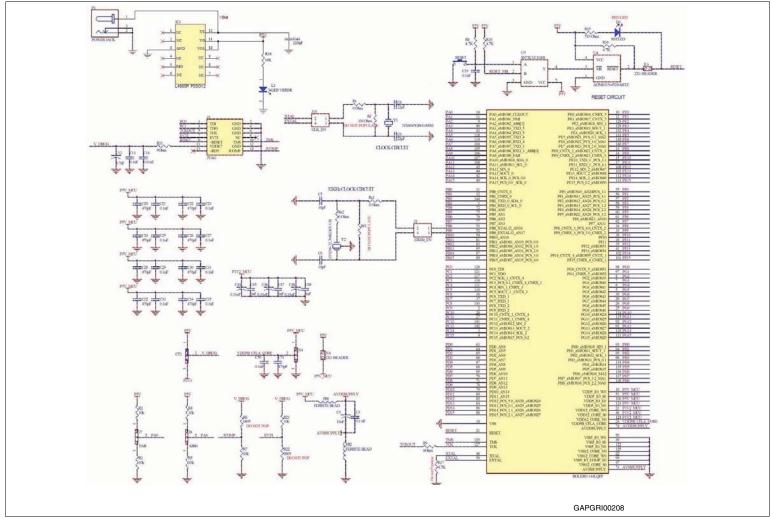

# **Reference schematic**

*Figure 15* shows a typical application schematic.

Figure 15. Typical application schematic of SPC560B40x-LQFP144

Doc ID 16127 Rev 5

Doc ID 16127 Rev 5

# Appendix A Document management

#### A.1 Reference documents

- 32-bit MCU family built on the Power Architecture<sup>®</sup> embedded category for automotive body electronics applications (SPC560B54x, SPC560B60x and SPC560B64x datasheet, Doc ID 15131)

- 32-bit MCU family built on the Power Architecture® embedded category for automotive body electronics applications (SPC560D30x, SPC560D40x datasheet, Doc ID 16315)

- 32-bit MCU family built on the Power Architecture® embedded category for automotive body electronics applications (SPC560D30x, SPC560D40x errata sheet, Doc ID 022965)

- 32-bit MCU family built on the Power Architecture<sup>®</sup> embedded category for automotive body electronics applications (SPC560B4x, SPC560B5x, SPC560C4x, SPC560C5x datasheet, Doc ID 14619)

- 32-bit MCU family built on the Power Architecture<sup>®</sup> embedded category for automotive body electronics applications (SPC560B4x/50 – SPC560C4x/50 errata sheet, Doc ID 15844)

# A.2 Acronyms

Table 8. Acronyms

| Acronym | Name                               |  |  |  |

|---------|------------------------------------|--|--|--|

| ADC     | Analog-to-digital converter        |  |  |  |

| BAM     | Boot assist mode                   |  |  |  |

| CRC     | Cyclic redundancy check            |  |  |  |

| EMC     | Electromagnetic compatibility      |  |  |  |

| EMI     | Electromagnetic interference       |  |  |  |

| ESL     | Equivalent series inductance       |  |  |  |

| ESR     | Equivalent series resistance       |  |  |  |

| LVD     | Low voltage detector               |  |  |  |

| NVUSRO  | Non-volatile user options register |  |  |  |

| POR     | Power-on reset                     |  |  |  |

| SIUL    | System integration unit lite       |  |  |  |

| TCK     | Test clock input                   |  |  |  |

| TDI     | Test data input                    |  |  |  |

| TDO     | Test data output                   |  |  |  |

| TMS     | Test mode select                   |  |  |  |

AN3024 Revision history

# **Revision history**

Table 9. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                           |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Sep-2009 | 1        | Initial release.                                                                                                                                                                                                                  |

| 03-Sep-2010 | 2        | Editorial and formatting changes throughout document Updated Section 1.3: Current consumption and voltage regulator and Section 7.5: I/O characteristic in STANDBY mode Added Section 8: EMC guidelines Updated Table 8: Acronyms |

| 04-Jun-2012 | 3        | Added Section 4.3.1: Some recommended crystal.                                                                                                                                                                                    |

| 17-Dec-2012 | 4        | Added following RPN: -SPC560B54/6x -SPC560D30x/40x Updated entire document.                                                                                                                                                       |

| 17-Sep-2013 | 5        | Updated Disclaimer.                                                                                                                                                                                                               |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

34/34 Doc ID 16127 Rev 5